ISSCC 2026: Lightmatter 3D硅光CPO解决方案赋能AI时代超高速互连

ISSCC 2026: Lightmatter 3D硅光CPO解决方案赋能AI时代超高速互连

光芯

发布于 2026-03-10 11:18:27

发布于 2026-03-10 11:18:27

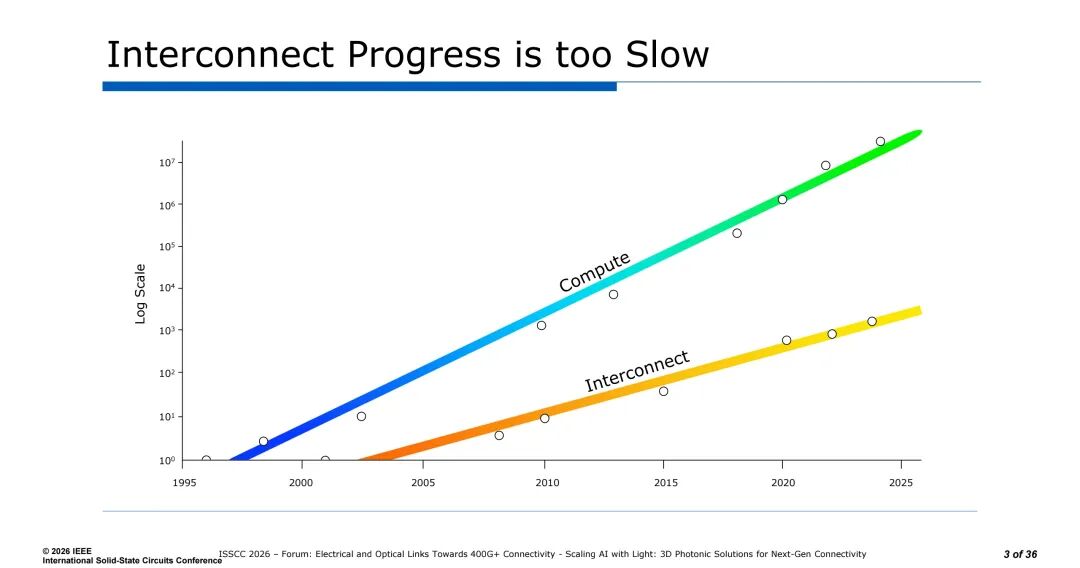

过去十年,AI领域实现了从AlphaGo到GPT-5的一系列突破性进展,算力的指数级增长成为AI性能提升的核心驱动力。但与之形成鲜明对比的是,互连技术的发展进度已严重滞后于算力增长,芯片I/O能力无法匹配算力芯片的扩容需求。

行业核心共识明确指出:AI性能过去的1000倍提升源于计算,而未来的1000倍增长将完全依赖互连技术的革新。在400G+乃至T级超高速互连的需求下,传统电互连体系已触及物理与工程极限,3D硅光子学成为支撑下一代AI数据中心互连升级的核心解决方案。

一、传统互连体系的多重极限桎梏

当前主流互连方案面临两大核心约束,已无法适配AI算力的持续扩容需求。

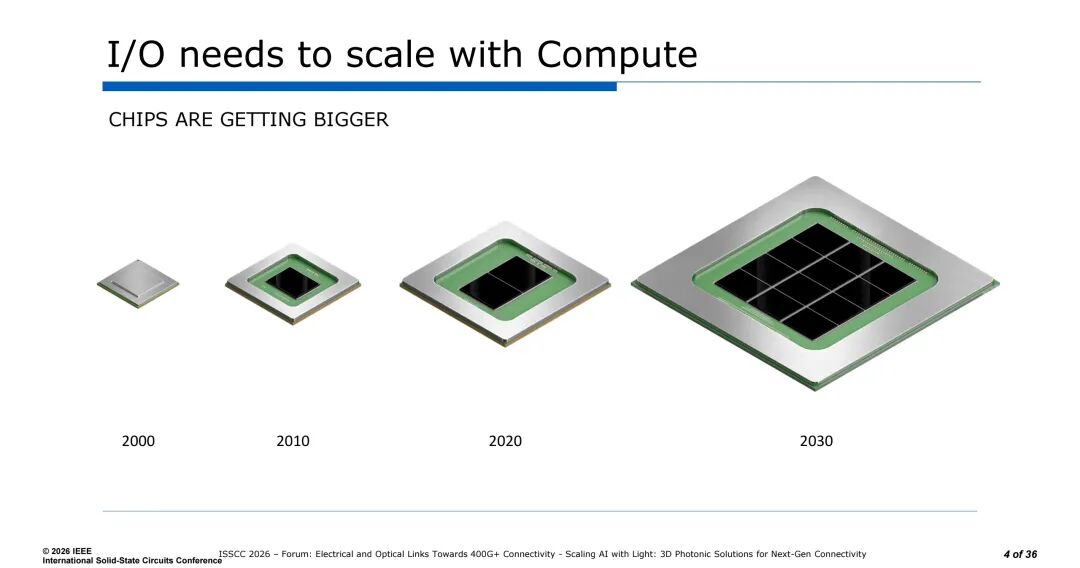

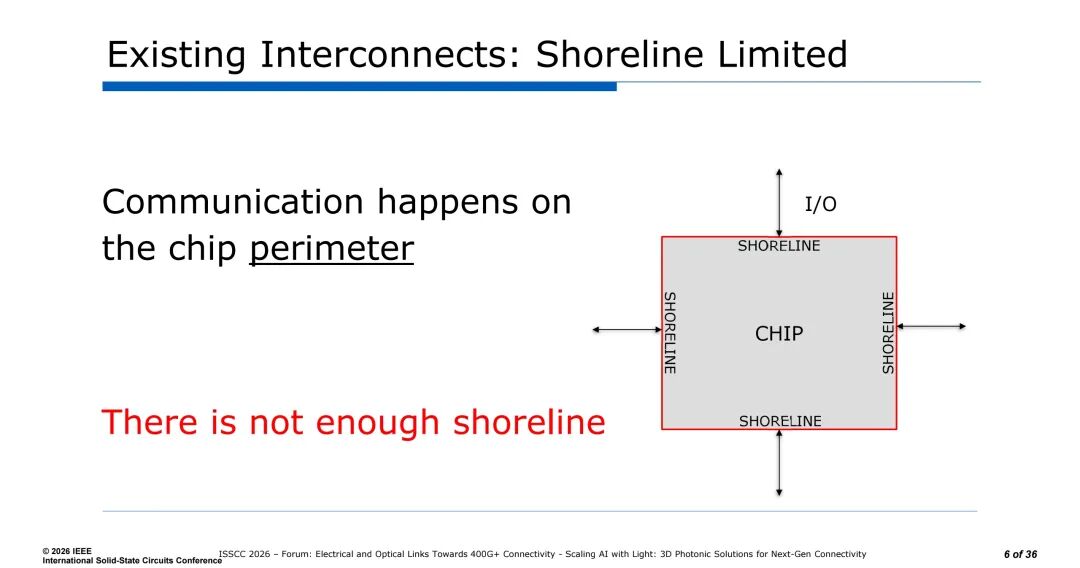

第一是岸线限制。传统互连的通信能力仅能依托芯片周边的岸线资源实现,随着芯片尺寸持续增大,有限的芯片周长无法匹配指数级增长的I/O带宽需求,岸线资源成为带宽扩容的核心瓶颈。

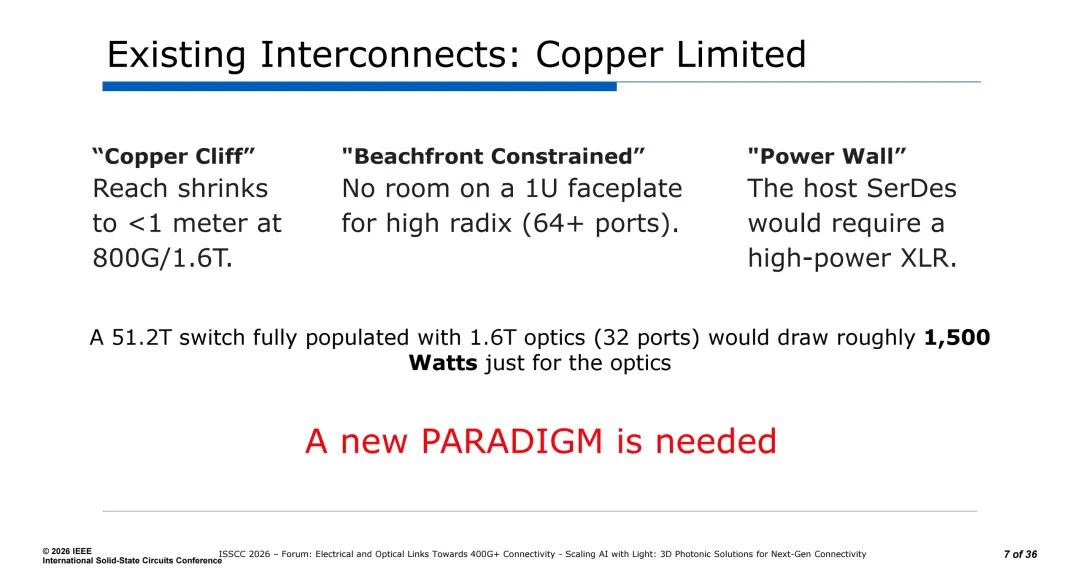

第二是铜互连的性能天花板,集中体现为三大核心壁垒:其一为“Copper Cliff”,在800G/1.6T的高速率下,铜互连的有效传输距离收缩至1米以内,无法满足数据中心内的跨机柜传输需求;其二为“边沿约束(Beachfront Constrained)”,1U面板的物理空间无法支撑64+端口的高基数交换机设计,直接限制了交换容量的扩容;其三为“功率墙(Power Wall)”,高速率下主机SerDes需采用高功耗XLR方案,仅光学部分的功耗就已极为可观——一台满配32个1.6T光模块的51.2T交换机,仅光模块的光学部分功耗就高达约1500瓦。

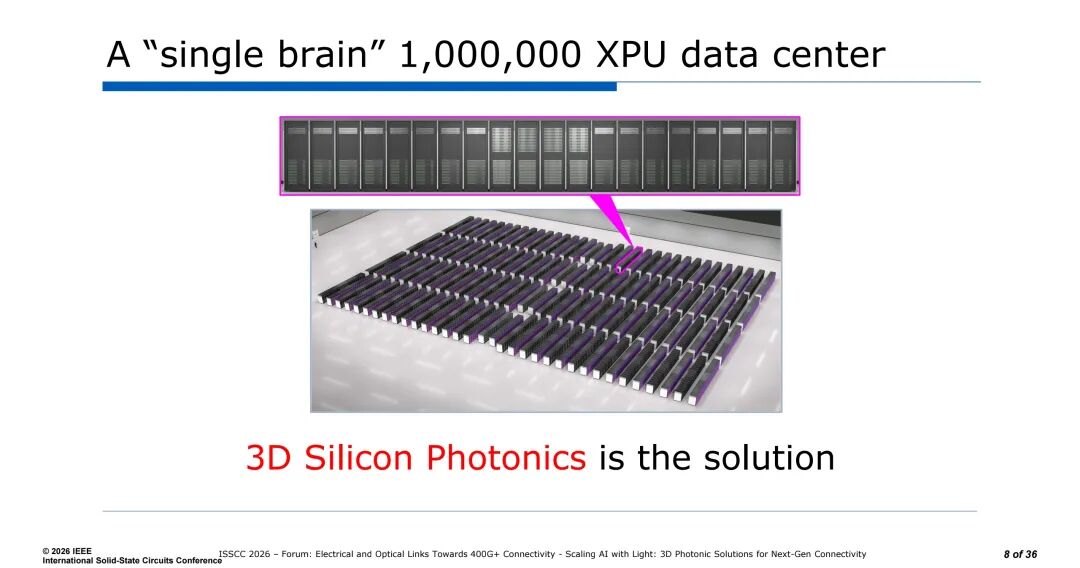

传统二维集成的互连方案已无法突破上述极限,无法支撑百万级XPU构成的“单脑”数据中心的互连需求,亟需全新的技术范式实现突破。

二、硅光子学的技术演进与基础架构

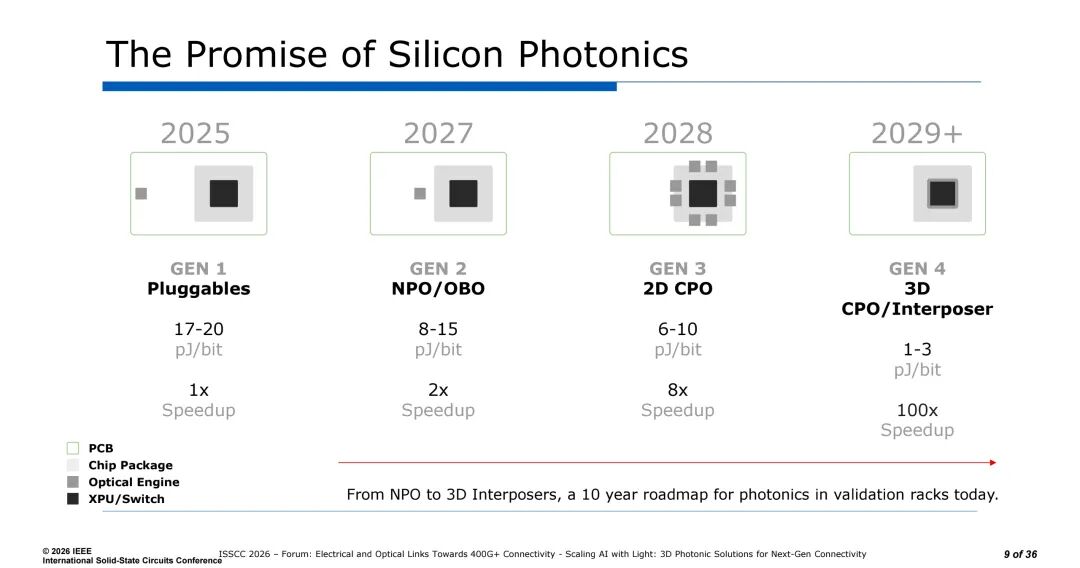

硅光子学通过将光通信技术与集成电路封装集成,实现了高速、低功耗、高密度的互连能力,其技术发展形成了清晰的十年演进路线图,且相关方案已在当前的验证机架中落地。

2.1 硅光子学的代际演进路线

硅光子学的技术演进分为四代,核心围绕功耗降低与带宽提速持续升级:

- 第一代(GEN 1)为可插拔光模块,对应2025年节点,功耗为17-20 pJ/bit,带宽提速能力为1倍基准;

- 第二代(GEN 2)为NPO/OBO方案,功耗降至8-15 pJ/bit,带宽提速能力提升至2倍;

- 第三代(GEN 3)为2D共封装光学(CPO)方案,功耗进一步降至6-10 pJ/bit,带宽提速能力达8倍;

- 第四代(GEN 4)为3D CPO/中介层方案,功耗可降至1-3 pJ/bit,带宽提速能力实现100倍的飞跃,是下一代超高速互连的核心形态。

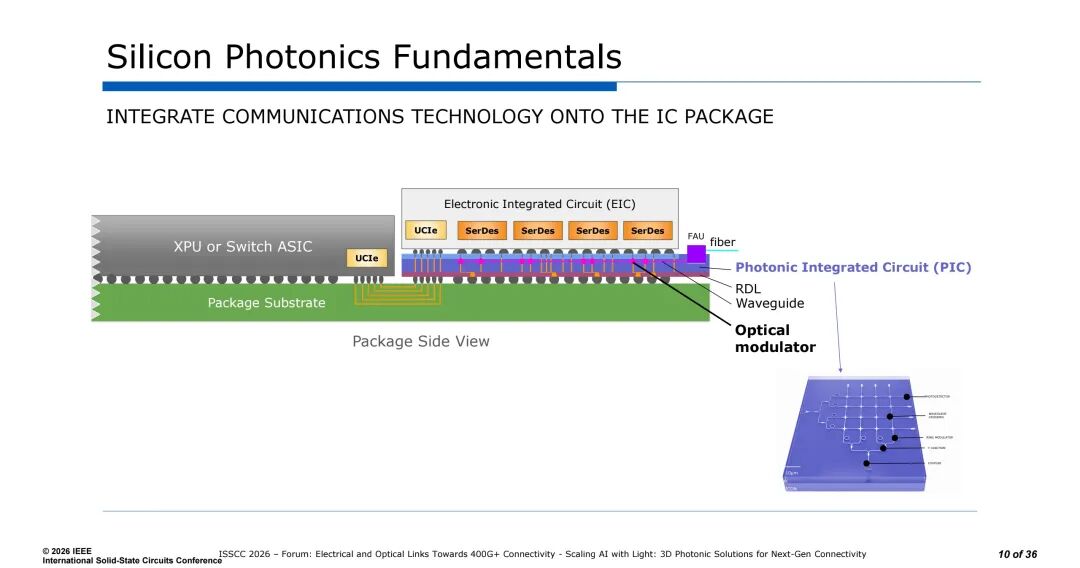

2.2 硅光子学的基础集成架构

硅光子学的核心是将通信技术集成到IC封装内,实现电子集成电路(EIC)与光子集成电路(PIC)的深度协同。其典型封装侧架构为:XPU或交换ASIC通过UCIe接口与SerDes链路连接,与EIC实现协同;PIC通过重分布层(RDL)与封装基板集成,PIC内部集成了波导、光调制器、光电探测器等核心光学器件,通过光纤阵列单元(FAU)实现与外部光纤的耦合,最终完成电信号-光信号的转换与高速传输。

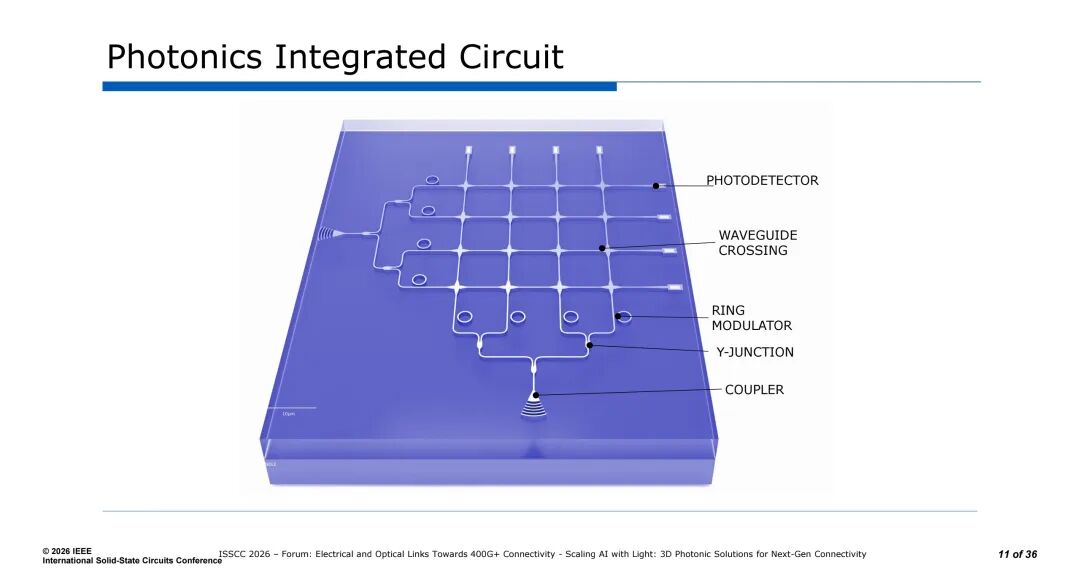

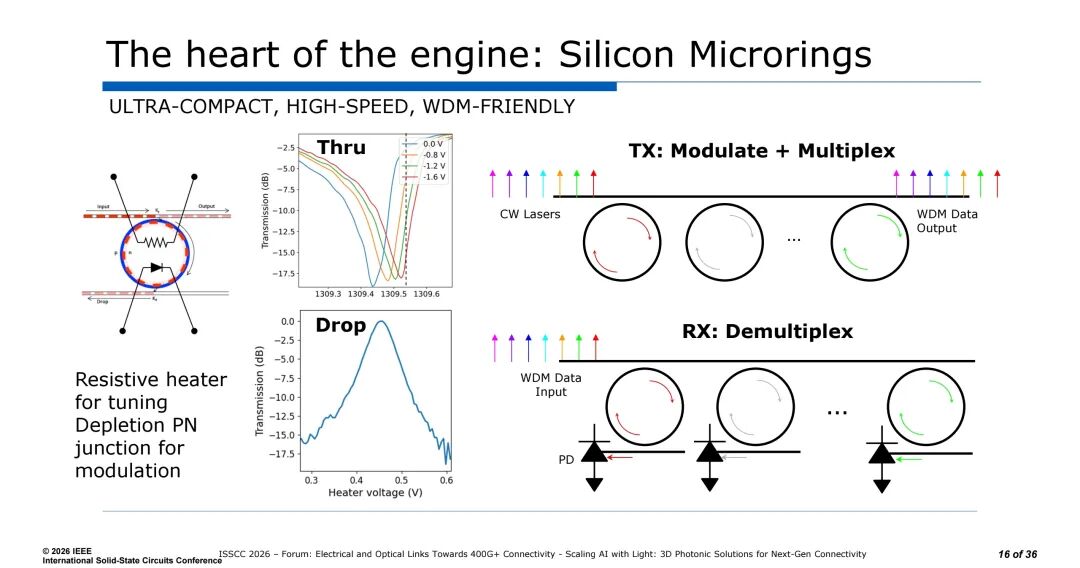

其中,PIC是硅光子学的核心载体,其核心组成器件包括光电探测器、波导、交叉结构、微环调制器(MRM)、Y结、耦合器等,而调制器则是光子链路的核心功能单元,直接决定了链路的尺寸、功耗与整体性能。

三、核心调制器技术:微环调制器(MRM)的性能突破

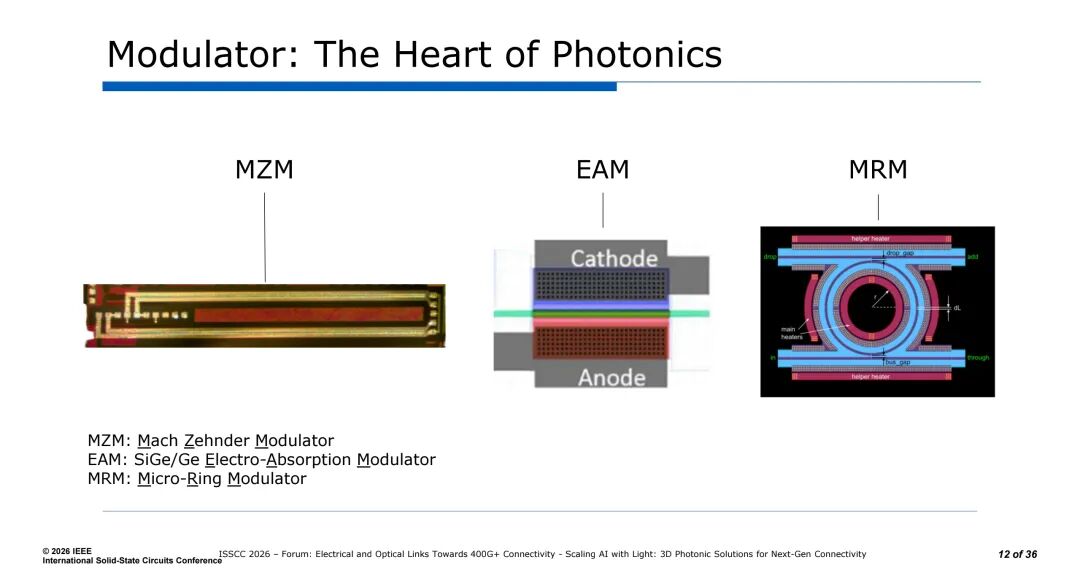

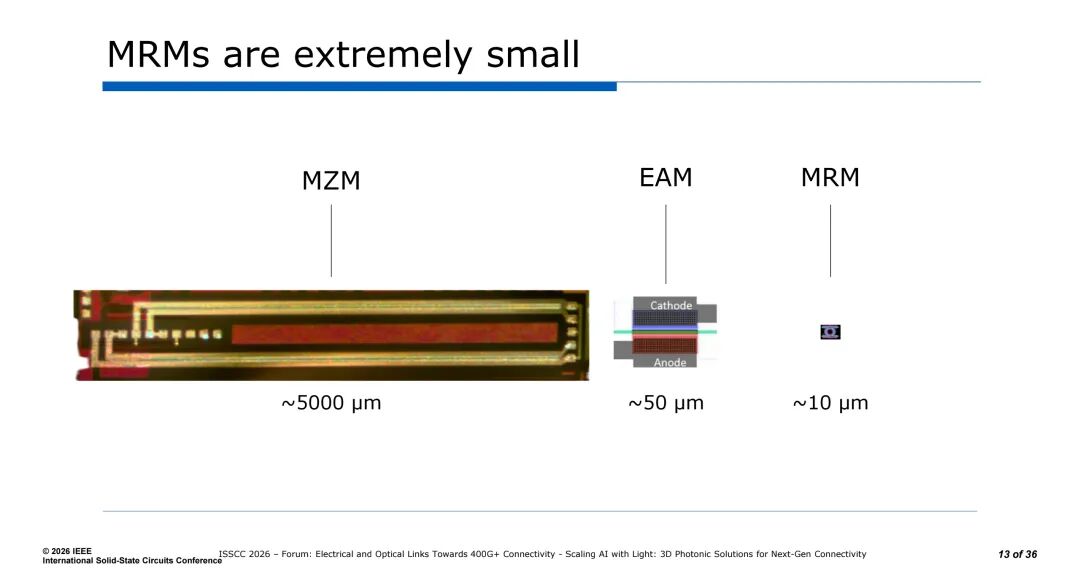

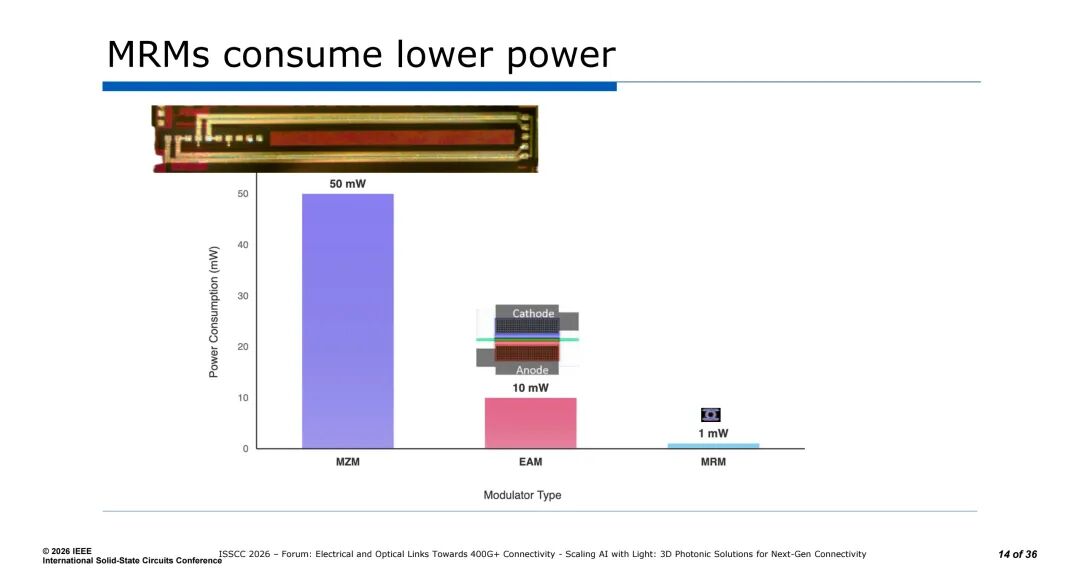

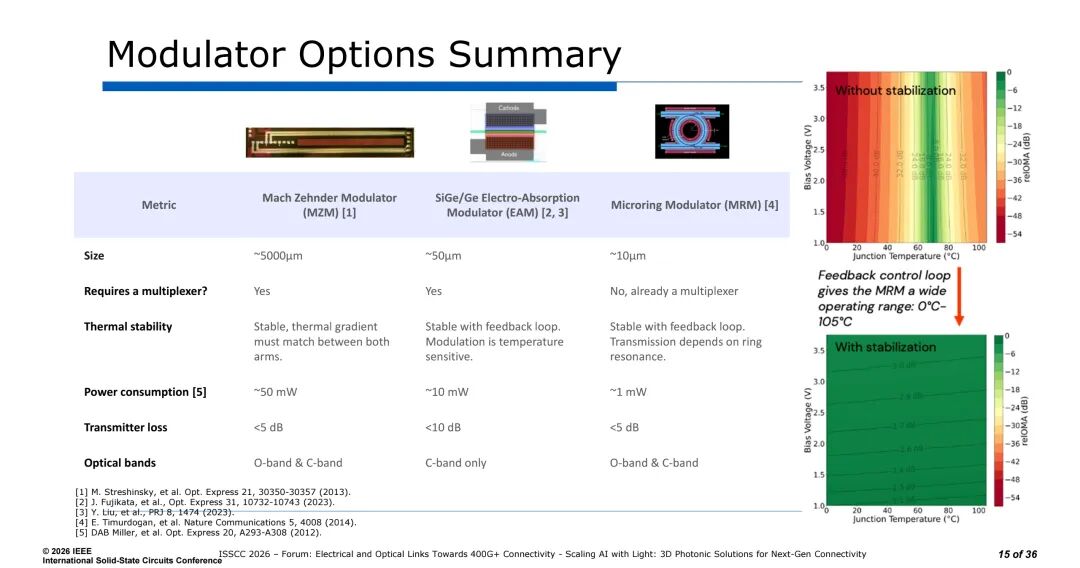

当前主流的光调制器分为三类:马赫曾德调制器(MZM)、SiGe/Ge电吸收调制器(EAM)与微环调制器(MRM),其中MRM凭借超紧凑尺寸、超低功耗与WDM友好的特性,成为3D硅光子学的核心器件。

在尺寸方面,MZM的典型尺寸约为5000μm,EAM的典型尺寸约为50μm,而MRM的典型尺寸仅约10μm,仅为MZM的1/500,为超高密度集成提供了核心基础。在功耗方面,MZM的典型功耗约为50mW,EAM的典型功耗约为10mW,而MRM的典型功耗仅约1mW,仅为MZM的1/50,可大幅缓解互连系统的功率墙压力。

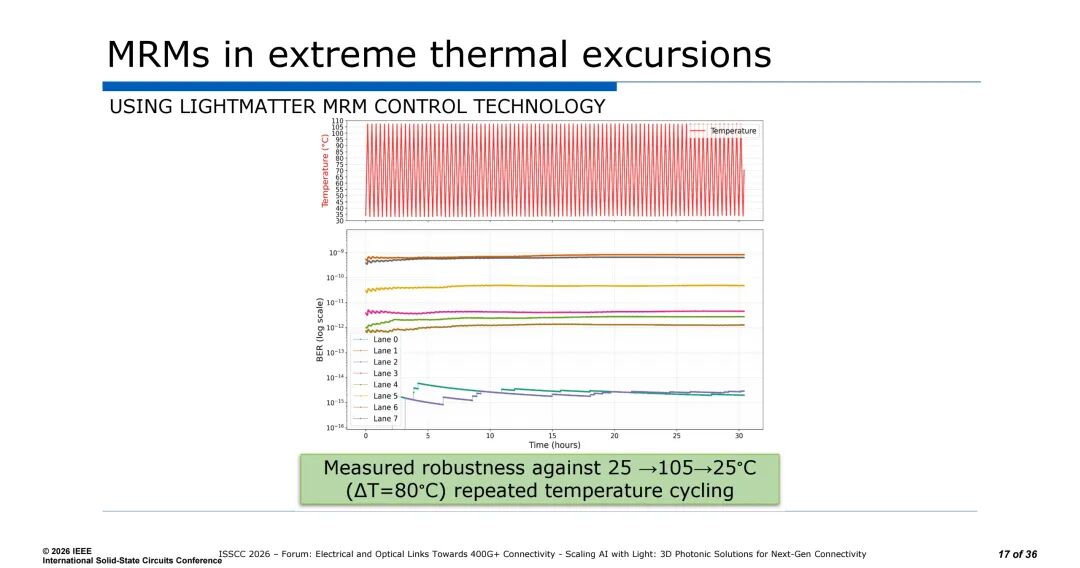

在功能特性方面,MZM与EAM需要额外配置复用器,而MRM本身就具备复用能力,无需额外器件;在光学波段支持上,MZM与MRM可支持O波段与C波段,而EAM仅支持C波段;在热稳定性方面,MZM需要保证两臂的热梯度匹配,EAM与MRM均可通过反馈环路实现稳定,其中MRM通过配套的反馈控制环路,可实现0℃至105℃的宽工作温度范围。

针对MRM的热稳定性,相关技术方案完成了极端工况下的鲁棒性验证:在25℃至105℃再回到25℃、温差达80℃的反复温度循环测试中,MRM的8个通道均保持了1E-12以下的稳定误码率;同时,该方案可抵御超过2000℃/s的快速温度变化,在极端热冲击下仍可保持稳定工作。

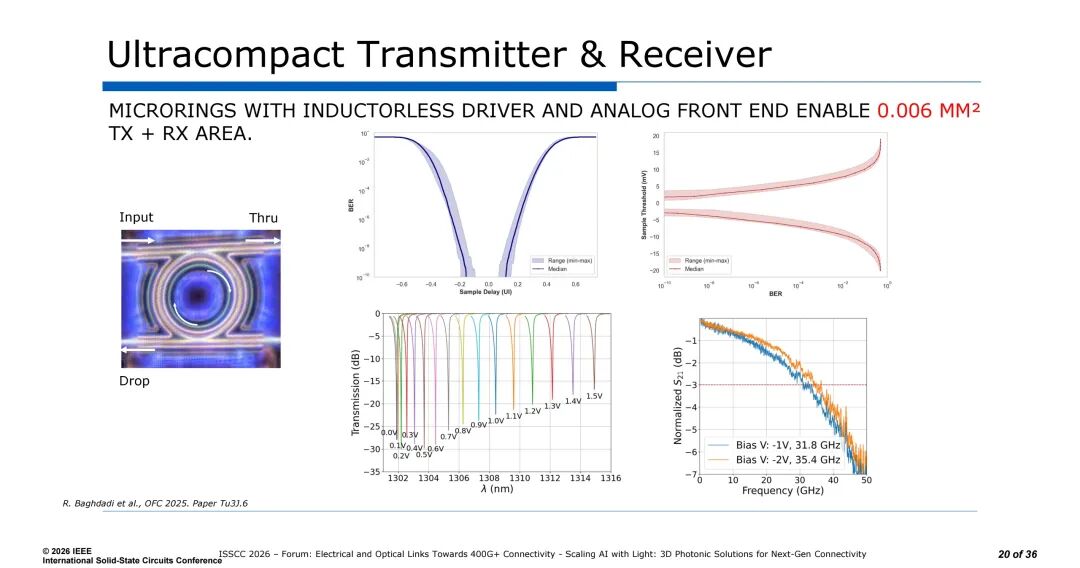

MRM的核心优势还在于其超紧凑、高速、WDM友好的特性:在发射端,MRM可同时完成调制与波分复用(WDM)功能,通过连续波激光器输入,实现多波长WDM数据输出;在接收端,可完成波分解复用功能,配套光电探测器实现光信号的接收与转换。同时,通过集成无电感驱动器与模拟前端,基于MRM的收发机可实现仅0.006 mm²的收发总面积,为3D高密度集成提供了关键支撑。

四、全链路协同的设计优化方法

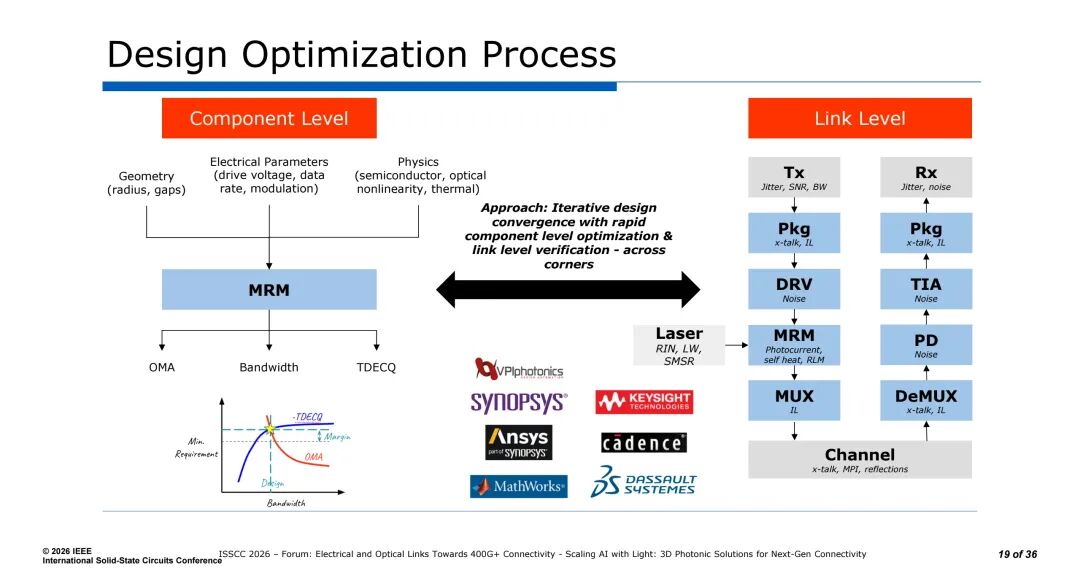

为保证光子链路的性能与良率,相关方案采用了组件级到链路级的迭代设计优化流程,实现跨工艺的设计收敛。

在组件级层面,设计覆盖了驱动电压、数据速率、调制特性等电参数,半径、间隙等几何参数,以及半导体特性、光学非线性、热特性等物理层面的优化,同步完成发射端的抖动、信噪比(SNR)、带宽,接收端的抖动、噪声,以及封装层面的串扰、插入损耗等性能的快速验证与优化。

在链路级层面,设计完成了通道串扰、多路径干涉、反射等全链路特性的验证,结合光调制幅度(OMA)、带宽、TDECQ余量等核心指标要求,实现全链路性能收敛。整个设计流程配套了完整的EDA工具链支撑,覆盖了光子仿真、电仿真、热仿真与链路验证全流程。

五、量产级超高速光子链路方案

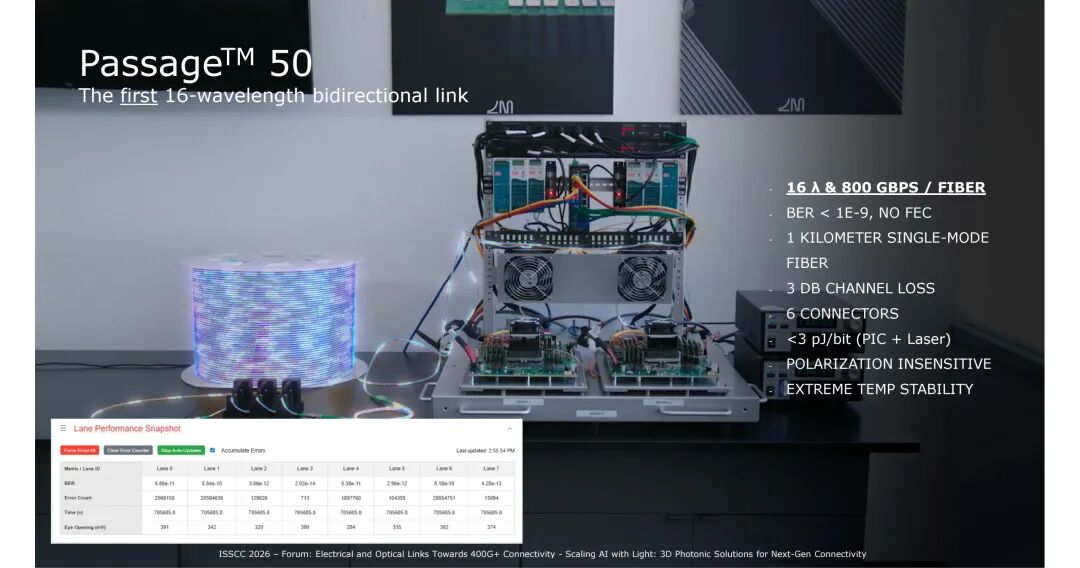

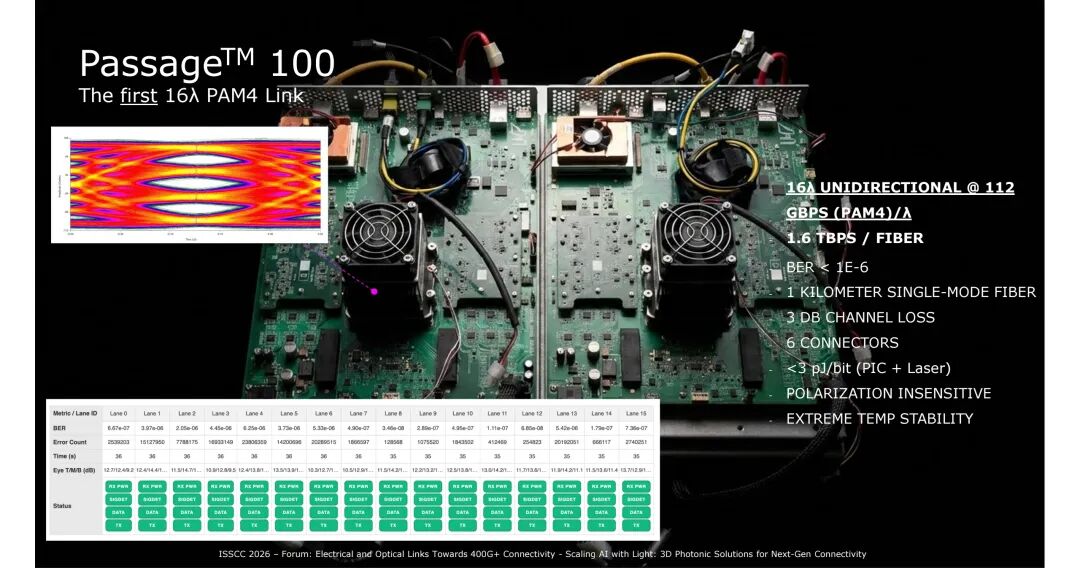

基于上述核心技术,已实现了两款量产级的光子链路产品,分别为PassageTM 50与PassageTM 100,均实现了业界领先的性能指标。

PassageTM 50是业界首个16波长双向链路,单光纤可实现800 Gbps的传输带宽,在无前向纠错(FEC)的情况下,误码率(BER)低于1E-9;该链路支持1公里的单模光纤传输,可承受3 dB的通道损耗与6个连接器的插入损耗,PIC与激光器的总功耗低于3 pJ/bit,同时具备偏振不敏感特性与极端温度稳定性。

PassageTM 100是业界首个16波长PAM4链路,单波长支持112 Gbps PAM4的传输速率,单光纤单向传输带宽可达1.6 Tbps,误码率(BER)低于1E-6;该链路同样支持1公里的单模光纤传输,可承受3 dB的通道损耗与6个连接器的插入损耗,PIC与激光器的总功耗低于3 pJ/bit,具备偏振不敏感特性与极端温度稳定性。

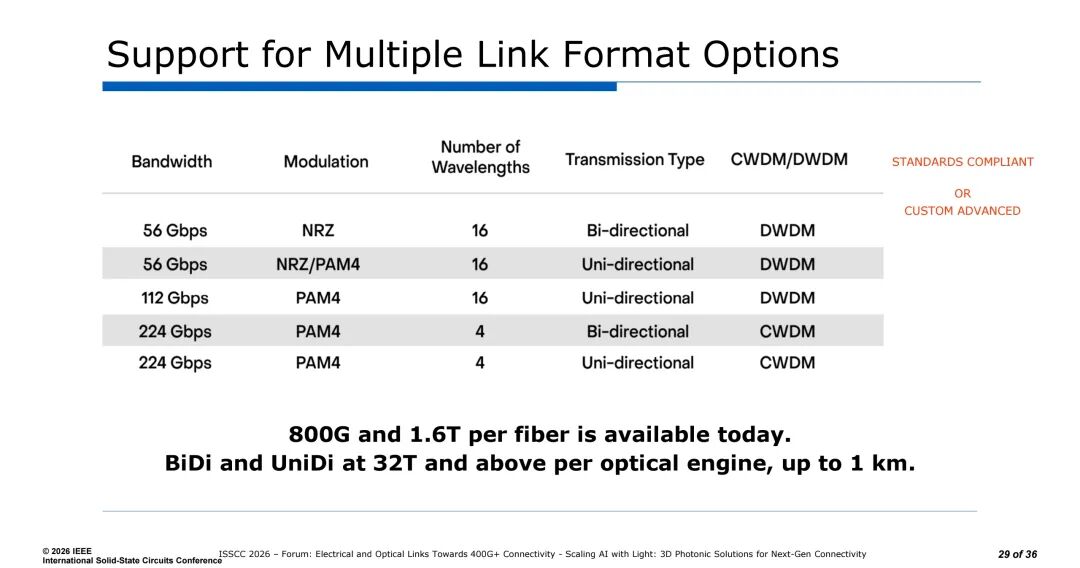

同时,该链路方案支持多种链路格式,可适配不同的应用需求,包括56 Gbps NRZ、56 Gbps NRZ/PAM4、112 Gbps PAM4、224 Gbps PAM4等多种速率与调制格式,支持双向与单向传输,适配CWDM与DWDM波长方案,既符合相关标准规范,也可支持定制化的先进方案。当前可实现单光纤800G与1.6T的带宽能力,单光学引擎可支持32T及以上的带宽,传输距离可达1公里。

六、3D堆叠技术突破带宽密度极限

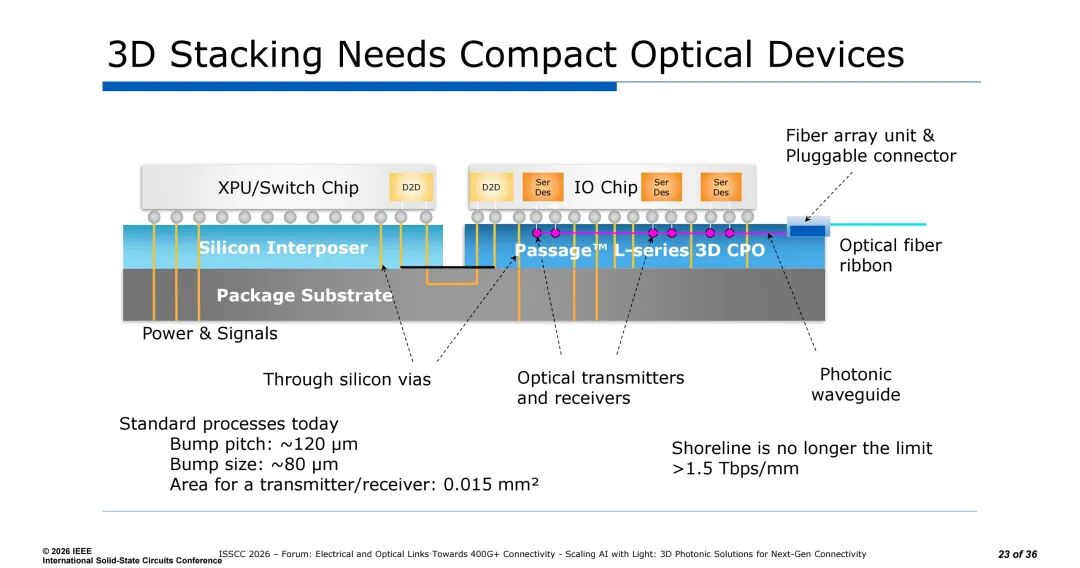

3D堆叠技术是突破传统二维集成岸线限制、实现超高带宽密度的核心,通过EIC与PIC的3D堆叠,以及3D中介层的集成方案,实现了带宽密度的量级提升。

基于MRM的超紧凑收发机,3D堆叠方案采用当前成熟的标准工艺,可实现约120μm的凸点间距、约80μm的凸点尺寸,单个收发机的面积仅为0.015 mm²,完全突破了芯片岸线的限制,实现了超过1.5 Tbps/mm的带宽密度。

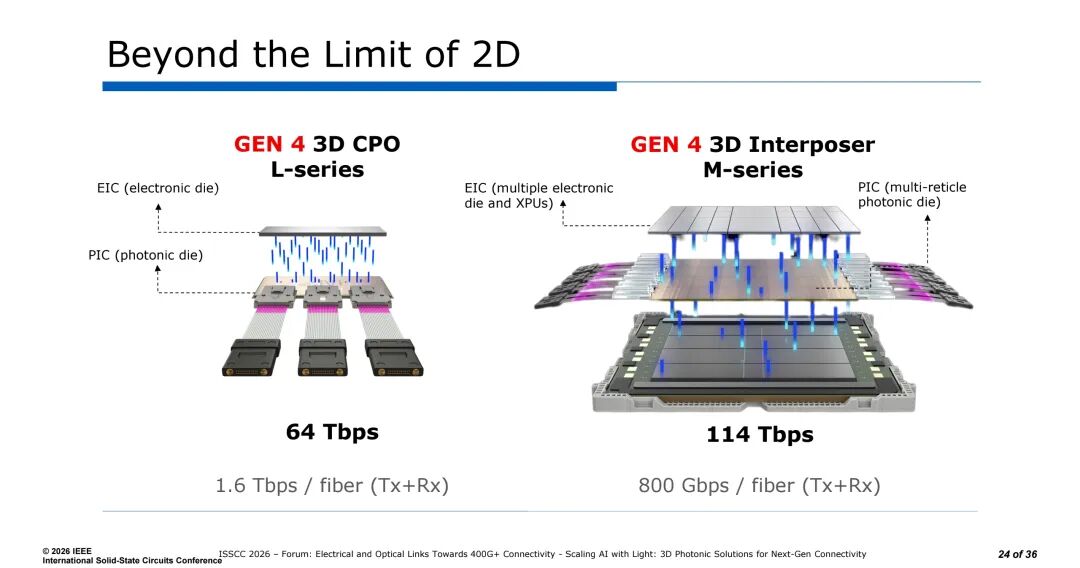

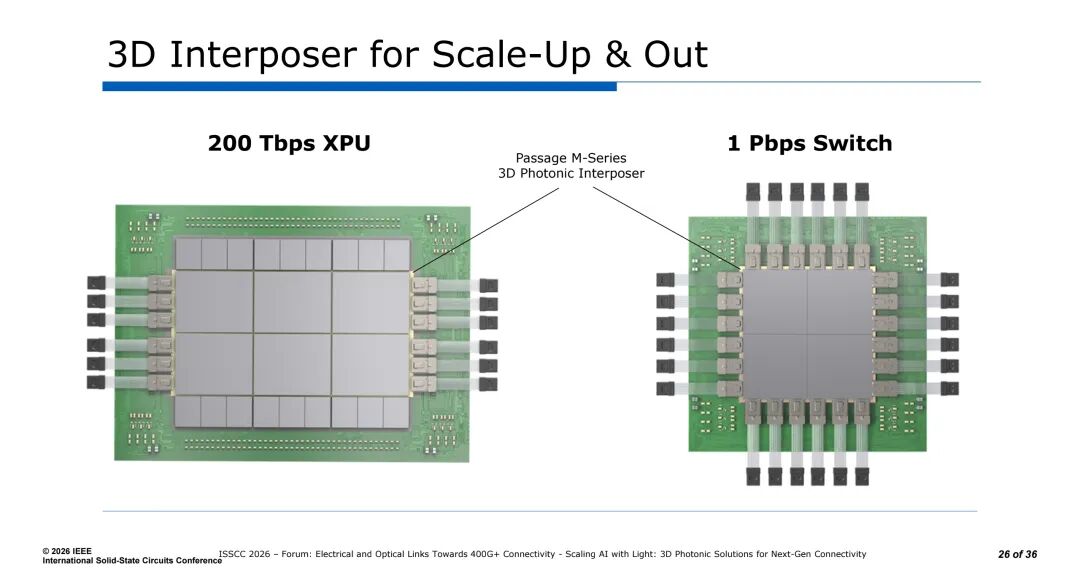

当前的3D集成方案分为两个系列,分别对应不同的应用场景:

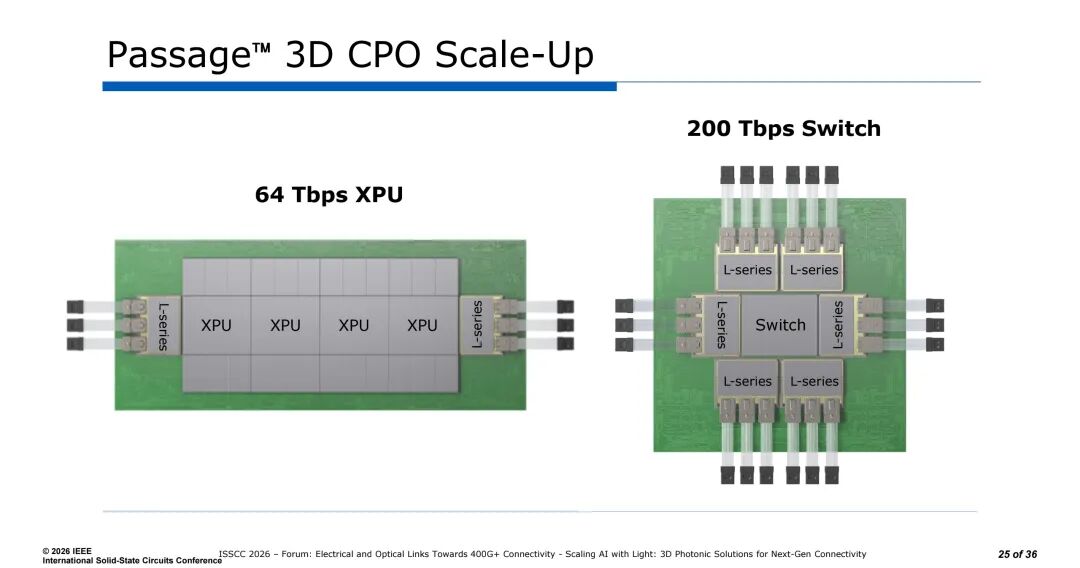

- L系列3D CPO方案,采用电子裸片(EIC)与光子裸片(PIC)的3D堆叠架构,单光纤可实现双向800 Gbps的传输带宽,单光学引擎的总带宽可达64 Tbps,可扩展支撑200 Tbps的交换机与64 Tbps的XPU;

- M系列3D中介层方案,可集成多个电子裸片与XPU、多标线的光子裸片(PIC),单光纤可实现双向1.6 Tbps的传输带宽,单光学引擎的总带宽可达114 Tbps,可扩展支撑200 Tbps的XPU与1 Pbps的交换机。

七、高量产能力、可靠性体系与配套光源技术

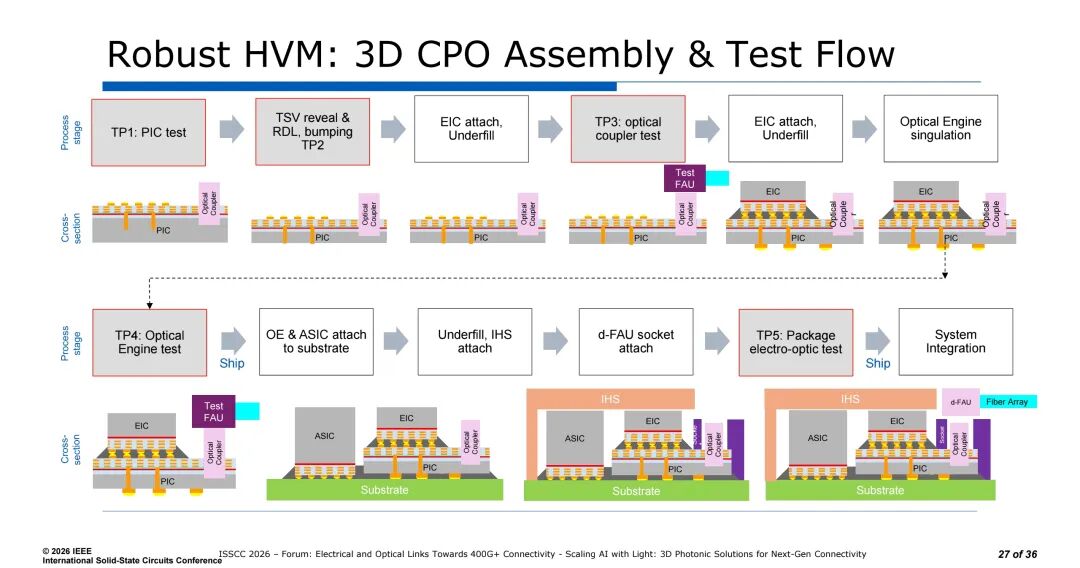

7.1 高量产装配与测试流程

相关3D CPO方案已具备成熟的高量产(HVM)装配与测试流程,全流程分为多个核心阶段:首先完成晶圆级PIC测试(TP1),随后进行RDL制作、凸点加工、TSV露出与TP2测试,完成EIC贴装与底部填充后,进行光学引擎的切割与TP3光学耦合器测试;之后完成光学引擎与ASIC向基板的贴装、底部填充与IHS贴装,进行TP4可拆卸FAU插座贴装与电光测试,再完成TP5封装级引擎测试,最终进入系统集成与出货环节,全流程实现了光学与电学性能的全节点测试管控。

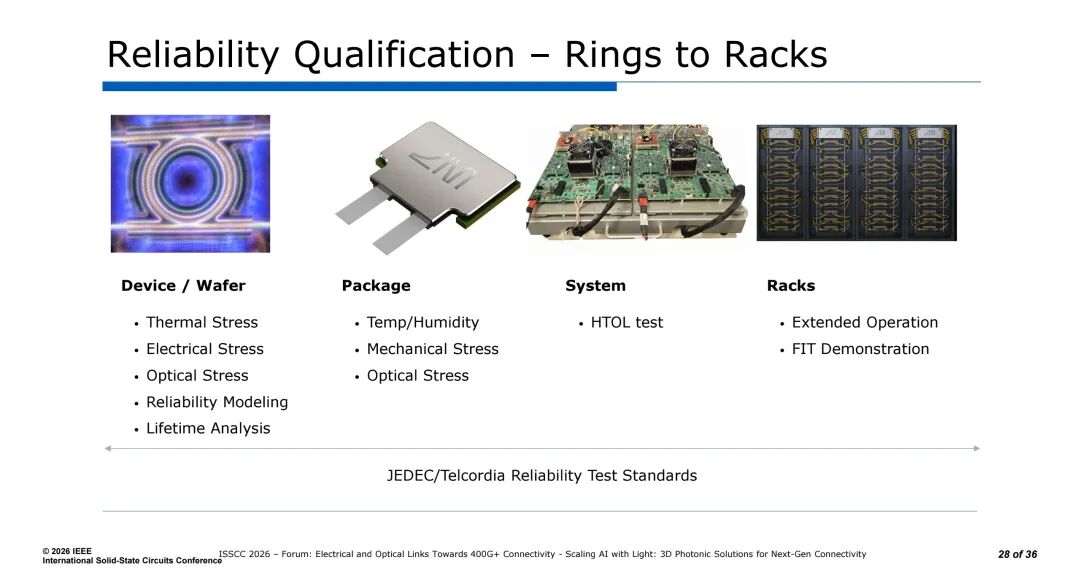

7.2 全层级可靠性认证体系

方案建立了从器件到机架的全层级可靠性认证体系,完全符合JEDEC与Telcordia可靠性测试标准:在器件/晶圆级,完成热应力、电应力、光应力测试,以及可靠性建模与寿命分析;在封装级,完成温湿度、机械应力、光应力测试;在系统级,完成高温工作寿命(HTOL)测试;在机架级,完成长期运行测试与FIT验证,全流程保障产品的长期可靠性。

7.3 配套光源技术

为匹配超高速光子链路的需求,方案配套了两大核心光源技术:

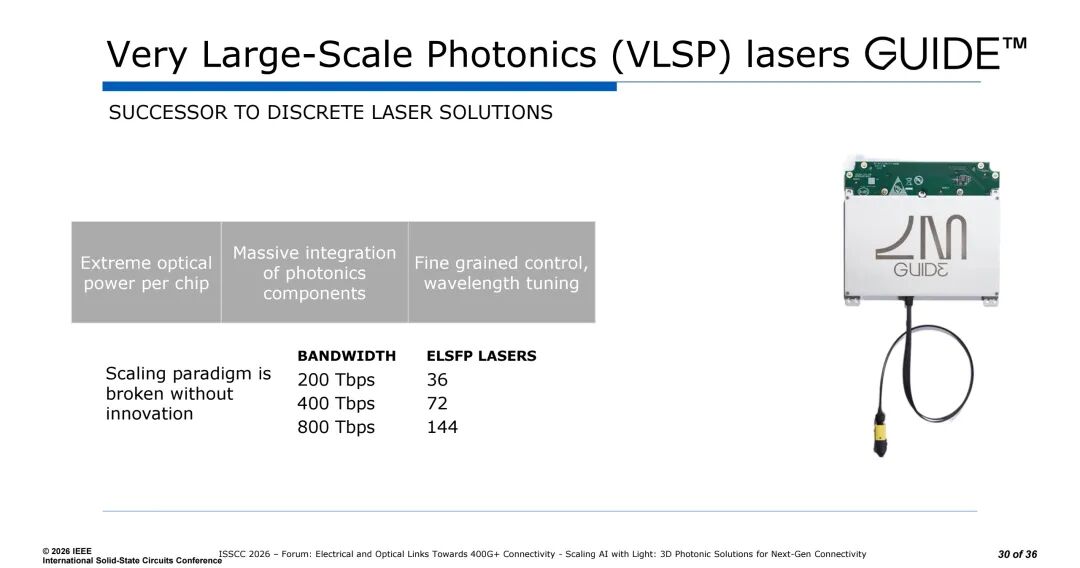

其一为超大规模光子学(VLSP)激光器,作为分立激光方案的替代方案,具备单芯片超高光功率、光子器件大规模集成、细粒度控制与波长调谐的核心优势,可支撑200 Tbps至800 Tbps的带宽扩容需求;

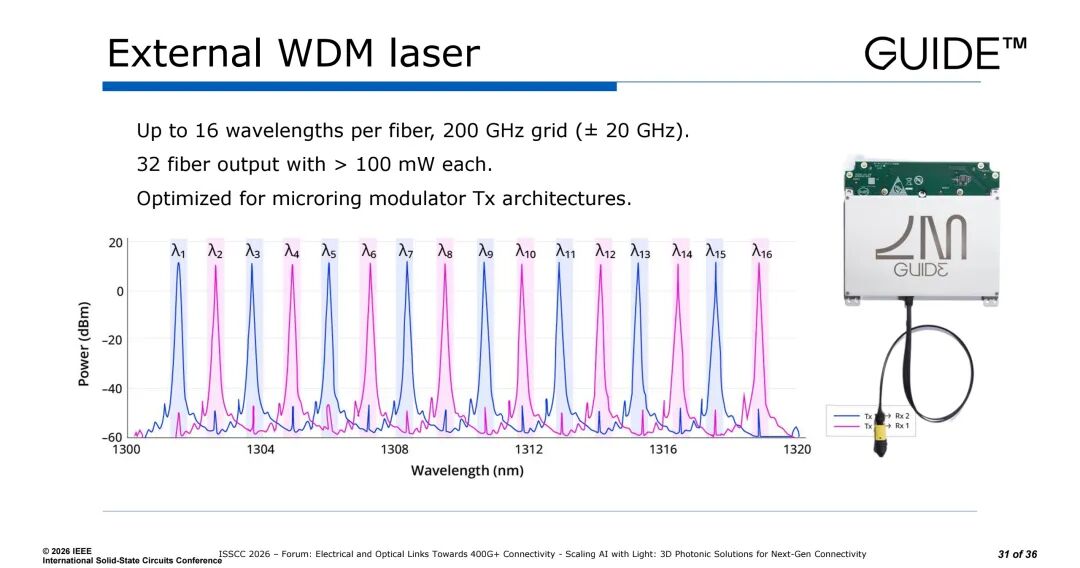

其二为外部WDM激光器,单光纤可支持最多16个波长,采用200 GHz间隔(±20 GHz),可实现32路光纤输出,每路输出功率超过100 mW,针对微环调制器的发射架构完成了优化。

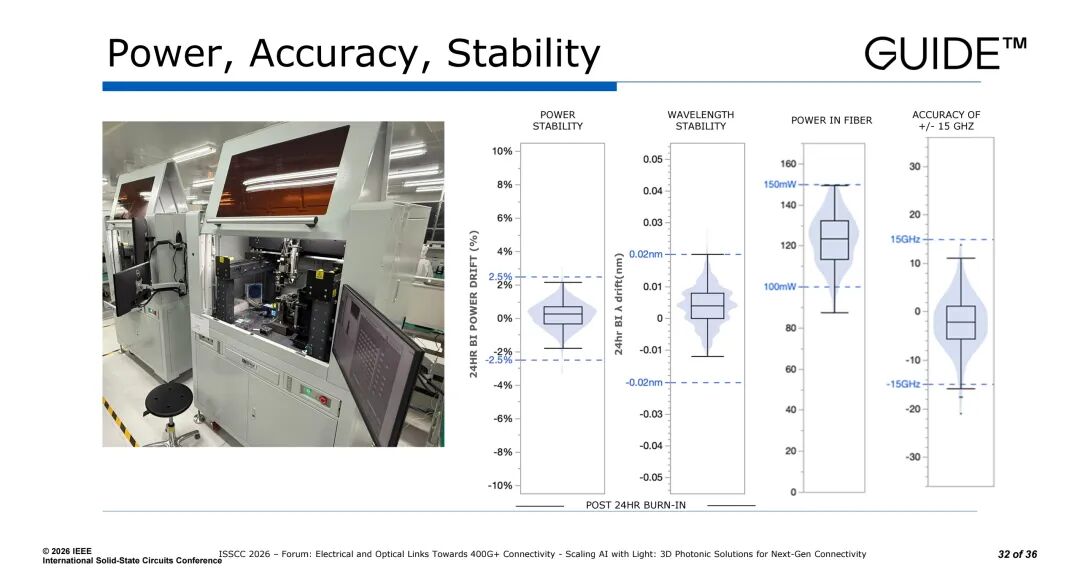

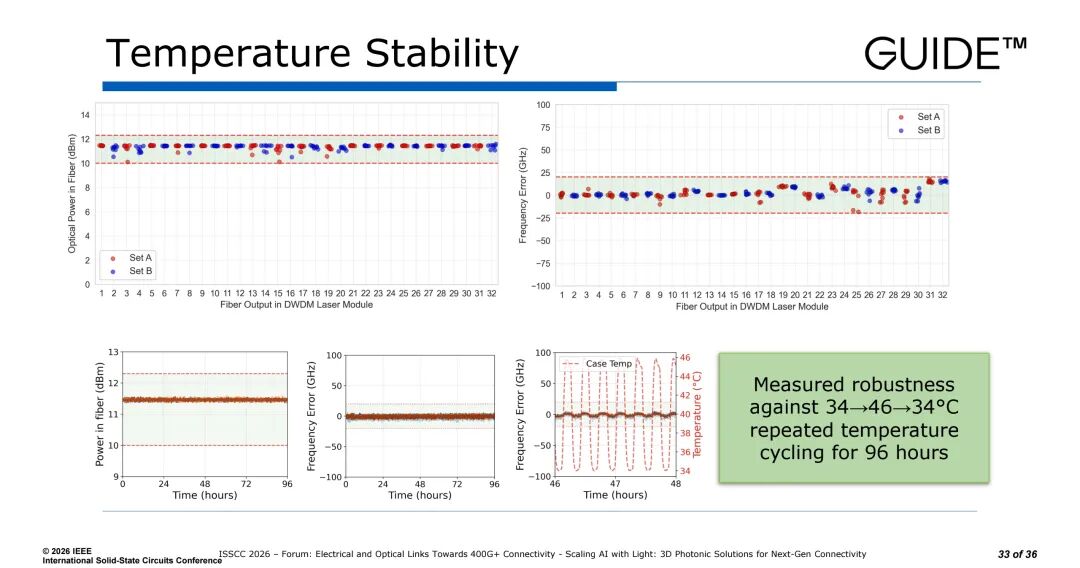

同时,配套的GUIDE技术实现了优异的功率与波长控制能力,可实现±15 GHz的波长精度,24小时老化后波长漂移低于0.05 nm,功率漂移低于10%;在34℃至46℃的96小时反复温度循环测试中,32路光纤输出均保持了优异的功率与波长稳定性,为光子链路的稳定工作提供了光源保障。

八、产业生态与技术总结

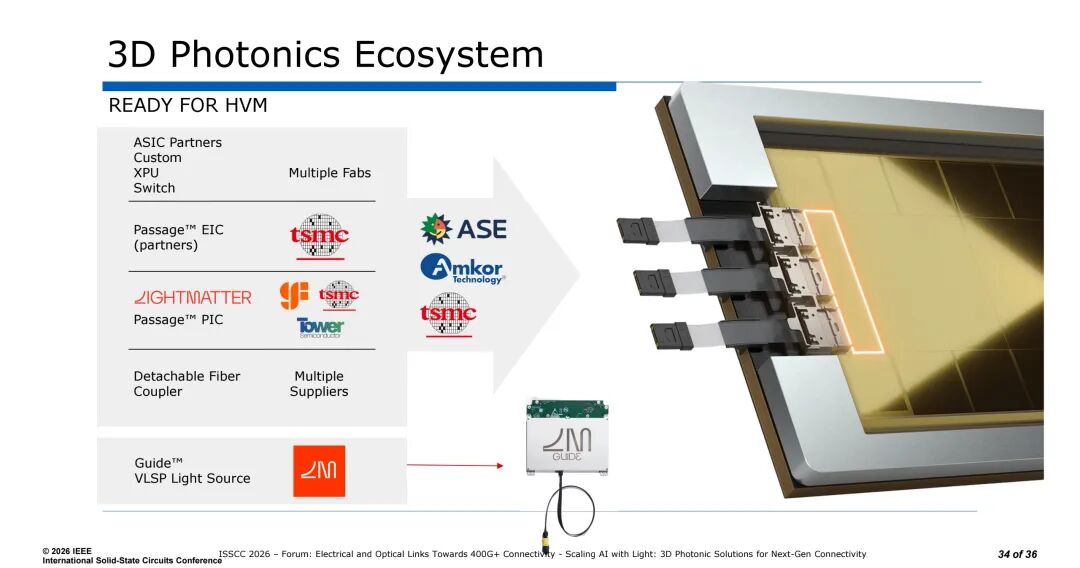

当前3D硅光子学方案已建立了成熟的产业生态,具备高量产能力,合作方覆盖了TSMC、ASE、Tower Semiconductor等多家主流晶圆厂与封测厂商,以及ASIC定制、XPU、交换芯片领域的合作伙伴,还有核心光学器件的供应商,形成了从芯片设计、制造、封测到系统集成的完整产业体系。

经过8年以上的技术创新、系统开发与优化,3D硅光子学方案已实现了技术与量产的双重突破,引领了AI数据中心的3D光子学革命,通过无岸线限制的带宽与高基数优势,为AI算力的下一个1000倍提升提供了核心的互连支撑,成为400G+下一代超高速互连的核心解决方案之一。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-03-06,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读