突破电互连极限:台积电ISSCC 2026硅光子学平台与400G+光链路技术全解析

突破电互连极限:台积电ISSCC 2026硅光子学平台与400G+光链路技术全解析

光芯

发布于 2026-03-05 13:03:13

发布于 2026-03-05 13:03:13

随着高性能计算(HPC)与人工智能(AI)网络的数据速率持续攀升,传统电互连的物理瓶颈日益凸显,成为制约系统算力与能效提升的核心障碍。在2026年IEEE国际固态电路会议(ISSCC)上,台积电发布了面向下一代HPC技术的硅光子学平台,系统阐述了光互连替代电互连的技术路径、核心器件体系、量产化平台能力与波分复用(WDM)使能技术,为400Gbps及以上的高速光链路提供了全栈解决方案。

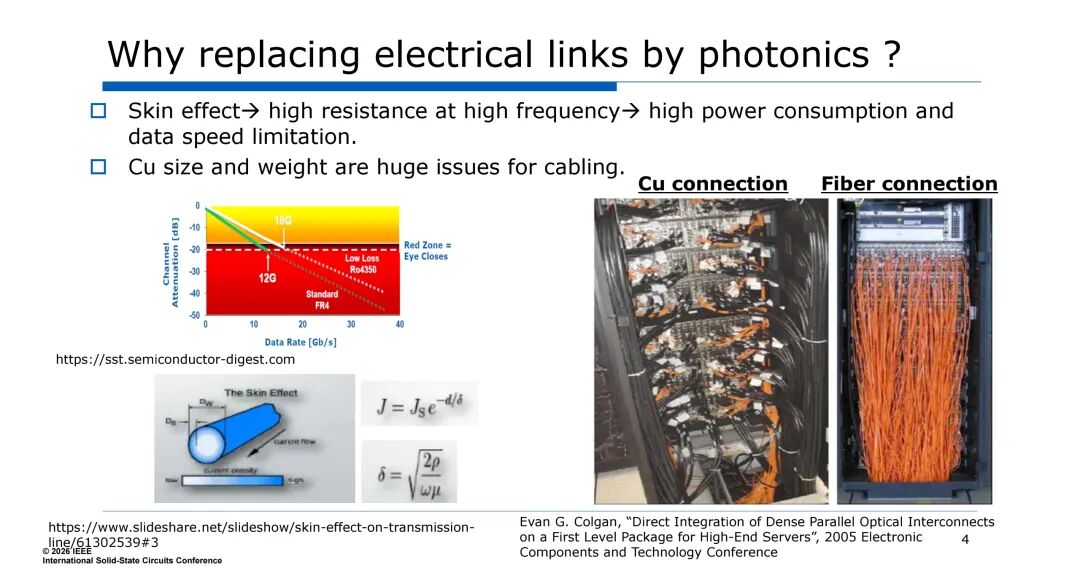

传统铜互连的核心局限来自趋肤效应,高频信号下,电流会集中在导体表面极薄的区域,导致导体等效电阻随频率升高显著增大,带来严重的功耗开销与数据速率上限,同时铜缆的尺寸与重量也成为大规模系统布线的核心挑战。趋肤深度与信号角频率的平方根成反比,高频下铜互连性能退化。与之相对,光互连凭借极低的传输损耗、超高的带宽密度与抗电磁干扰能力,成为突破电互连瓶颈的核心方案。

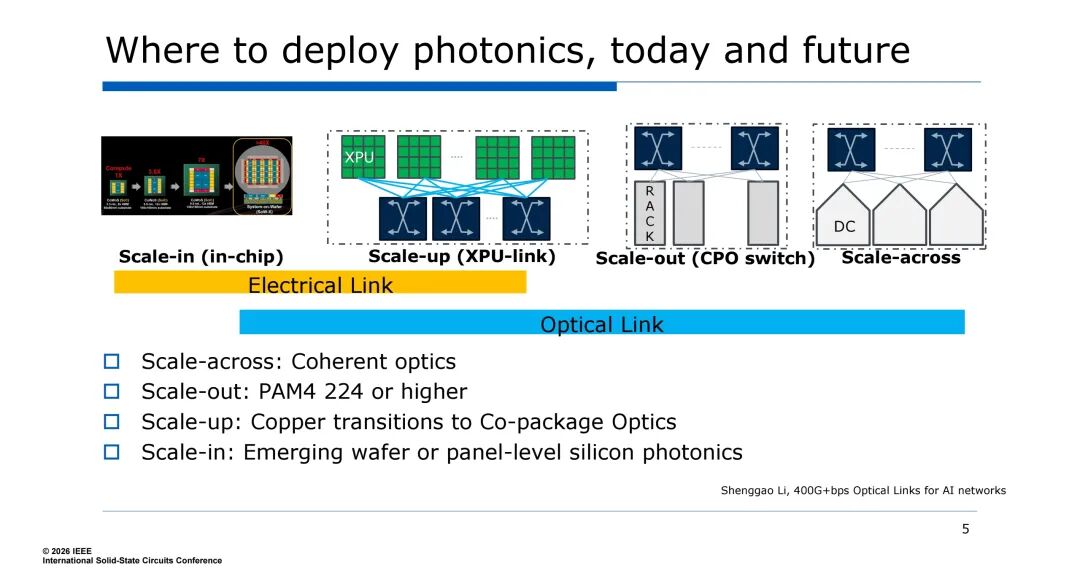

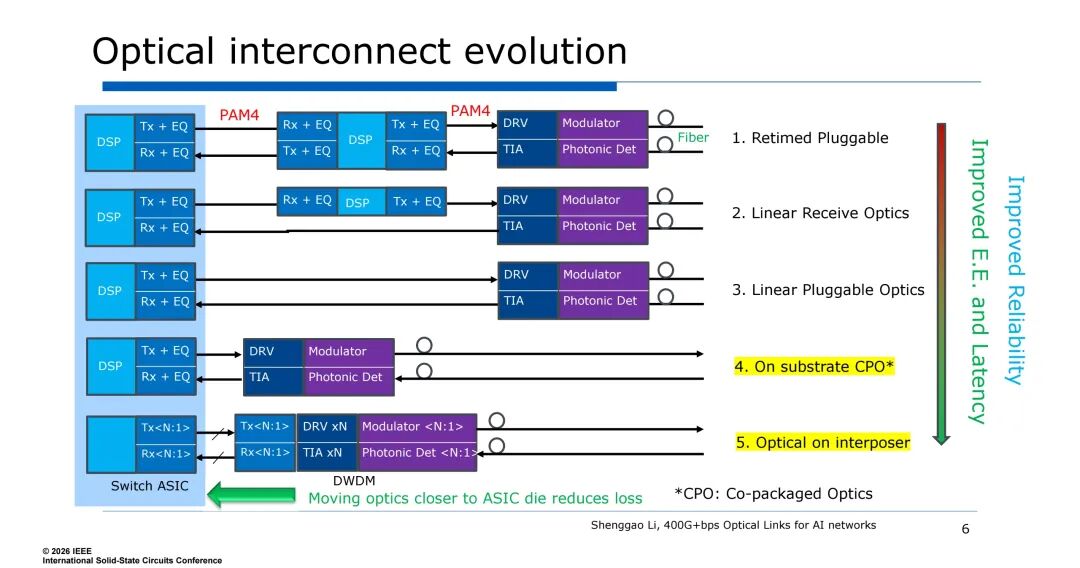

光互连的应用覆盖从当前到未来的全场景算力互联需求,包括跨数据中心的Scale-across场景(采用相干光技术)、数据中心内交换机的Scale-out场景(采用224Gbps及以上速率的PAM4信号与共封装光学CPO架构)、多XPU间的Scale-up场景(铜互连逐步向CPO过渡),以及未来的Scale-in场景(片内互联,采用新兴的晶圆或面板级硅光子技术)。光互连的技术演进核心逻辑是将光学引擎逐步向ASIC芯片靠近,以此降低传输损耗、提升能效与降低延迟,从最初的重定时可插拔光模块、线性接收光模块、线性可插拔光模块,逐步发展到基板上集成的CPO、中介层上集成的光学方案,同步实现了系统可靠性的持续提升。

◆ 硅光子学的核心物理基础

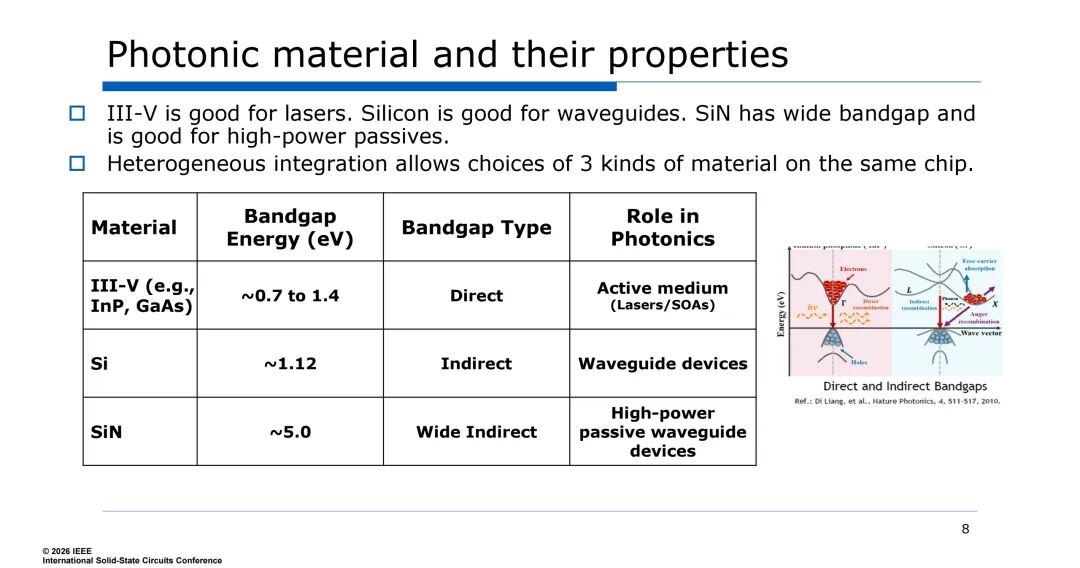

硅光子学的核心是在硅基平台上实现光的产生、调制、传输与探测,其器件性能的核心来自材料体系与光学结构的协同优化。在材料体系上,不同材料凭借其能带特性承担不同的光子学功能:III-V族化合物(如InP、GaAs)具有~0.7-1.4eV的直接带隙,是实现激光器、半导体光放大器(SOA)等有源器件的核心介质;硅(Si)具有~1.12eV的间接带隙,是实现高性能波导器件的核心材料;氮化硅(SiN)具有~5.0eV的宽间接带隙,适用于高功率无源波导器件。通过异质集成技术,可在同一芯片上整合三类材料,兼顾有源与无源器件的性能需求。

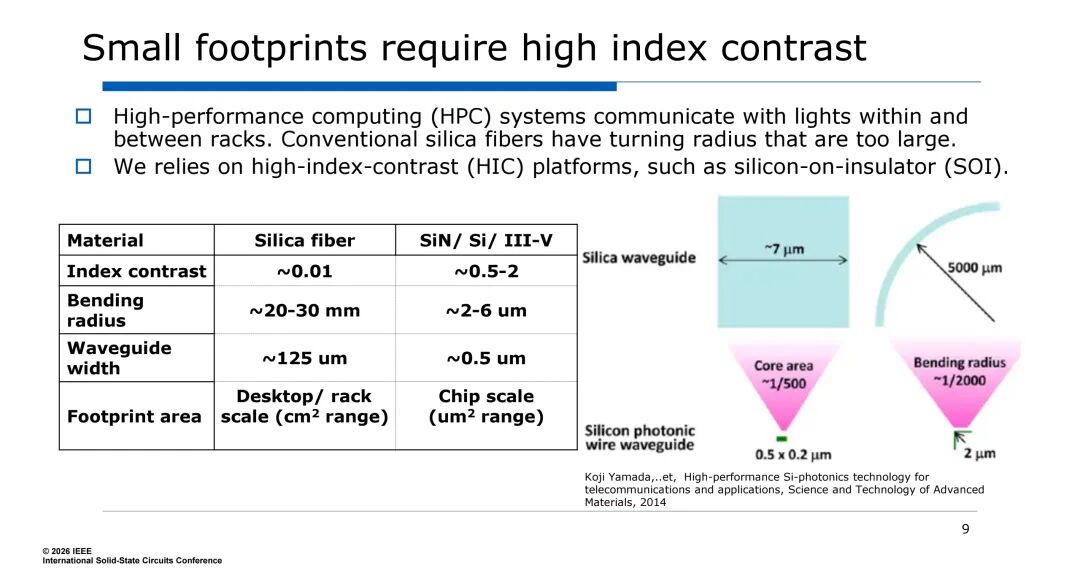

片上光集成的核心前提是实现极小尺寸的光场约束,这依赖于高折射率对比(HIC)平台。传统二氧化硅光纤的折射率对比仅约0.01,对应弯曲半径需达到20-30mm,波导宽度约125μm,占用面积为桌面或机架级;而硅基绝缘体(SOI)等高折射率差平台的折射率对比可达~0.5-2,对应弯曲半径仅2-6μm,波导宽度约0.5μm,核心面积仅为二氧化硅波导的1/500,弯曲半径仅为1/2000,将光器件的占用规模降到了芯片级,为大规模片上光子集成提供了可能。

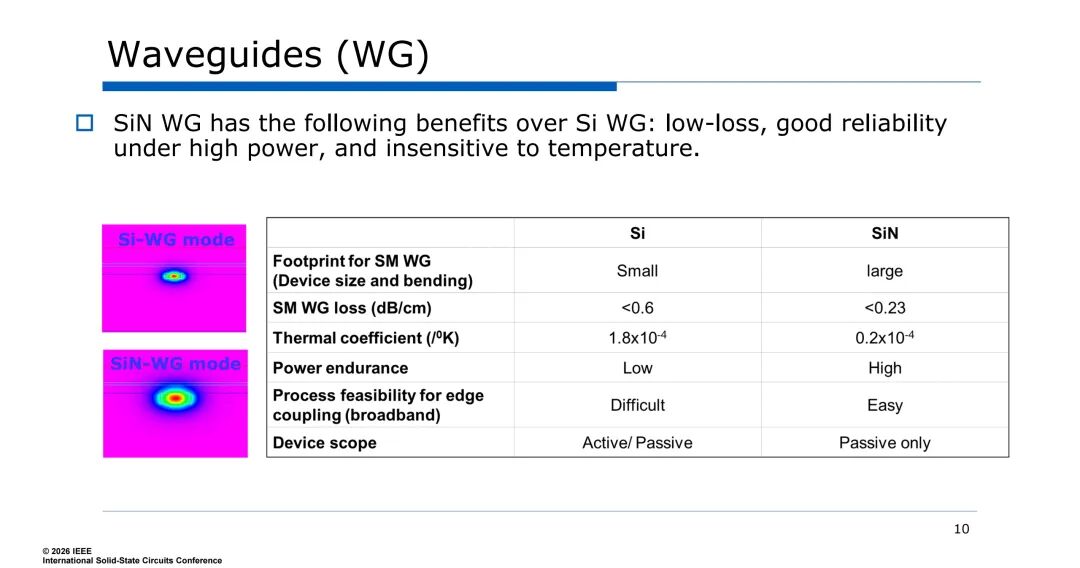

硅波导与氮化硅波导是片上光传输的核心载体,二者具有互补的性能特性。硅波导可实现单模波导的极小占用面积,覆盖有源与无源器件场景,单模传输损耗低于0.6dB/cm;氮化硅波导则具备更优异的综合性能,单模传输损耗低于0.23dB/cm,热光系数仅为0.2×10^-4 /K,远低于硅波导的1.8×10^-4 /K,对温度变化不敏感,同时具备更高的高功率耐受能力,边缘耦合的宽带工艺可行性更高,仅适用于无源器件场景。

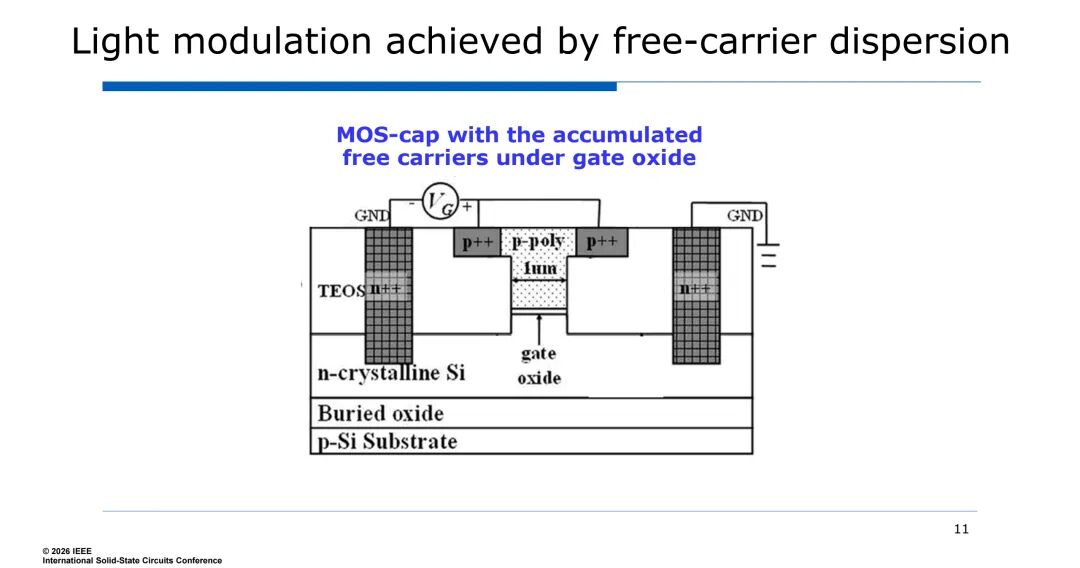

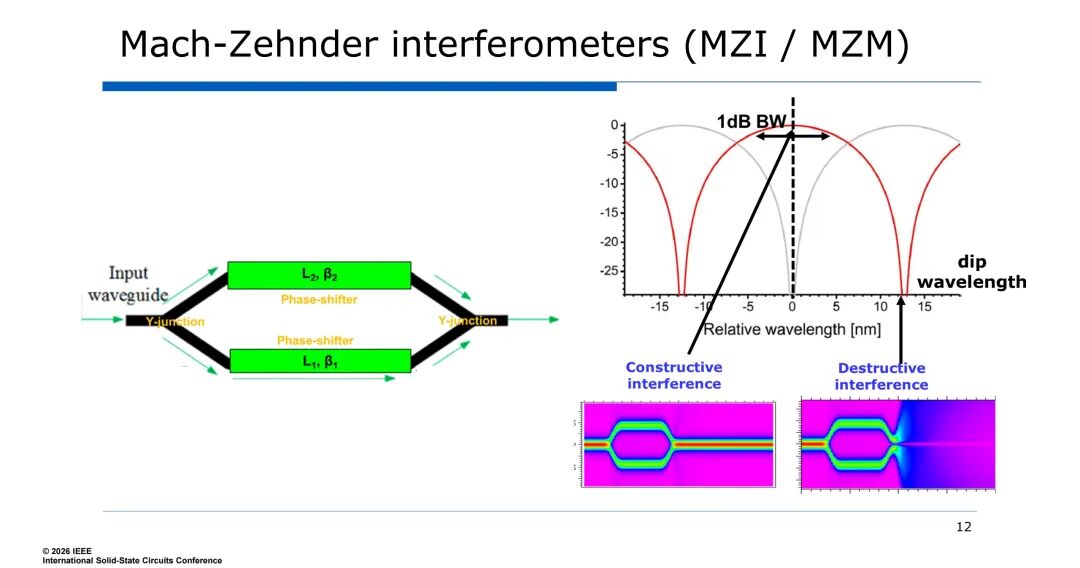

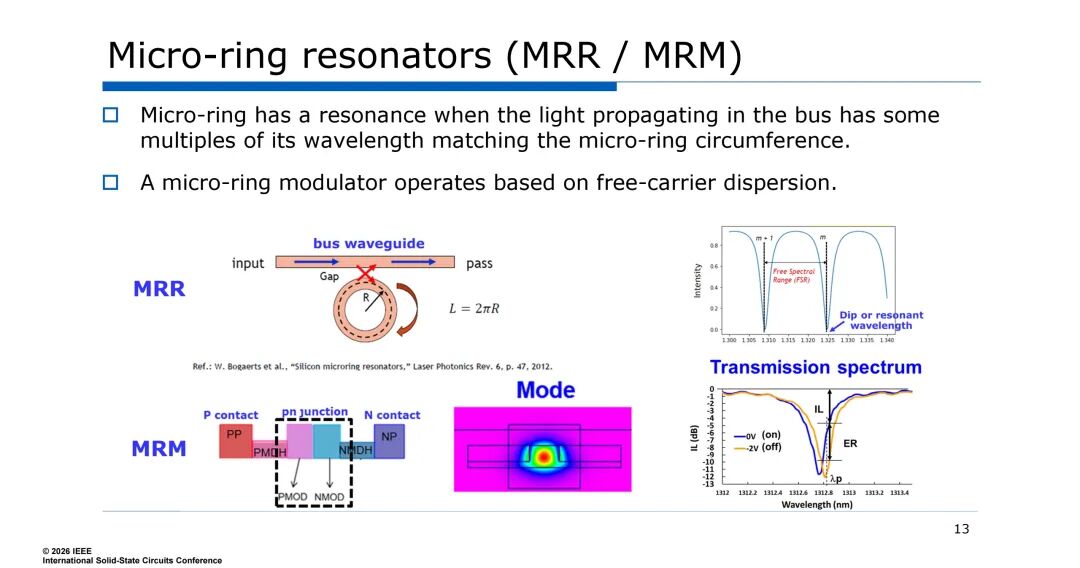

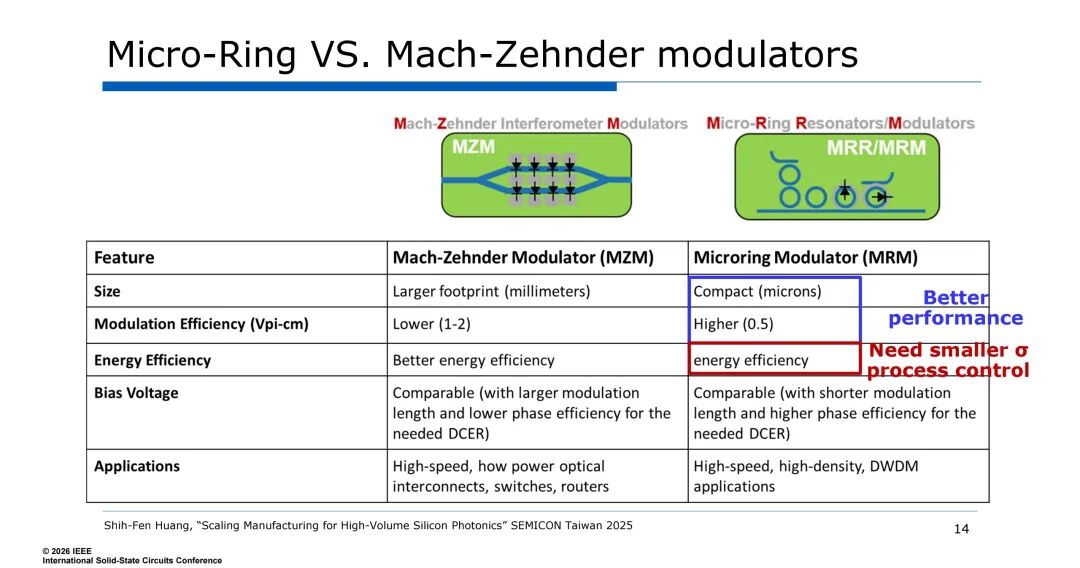

片上光调制基于自由载流子色散效应实现,核心分为两类架构:马赫曾德尔干涉调制器(MZM)与微环调制器(MRM)。MZM基于马赫曾德干涉结构,通过两个干涉臂的相位调制实现光信号的相长与相消干涉,完成电光转换,具备更优异的线性性能与宽带特性;MRM基于微环谐振结构,当总线波导中传输的光波长满足微环周长的整数倍谐振条件时,光场会被限制在微环内,通过自由载流子色散效应调控微环的谐振波长,实现光信号的调制,相比MZM具备更小的器件尺寸,但对工艺控制的精度要求更高。

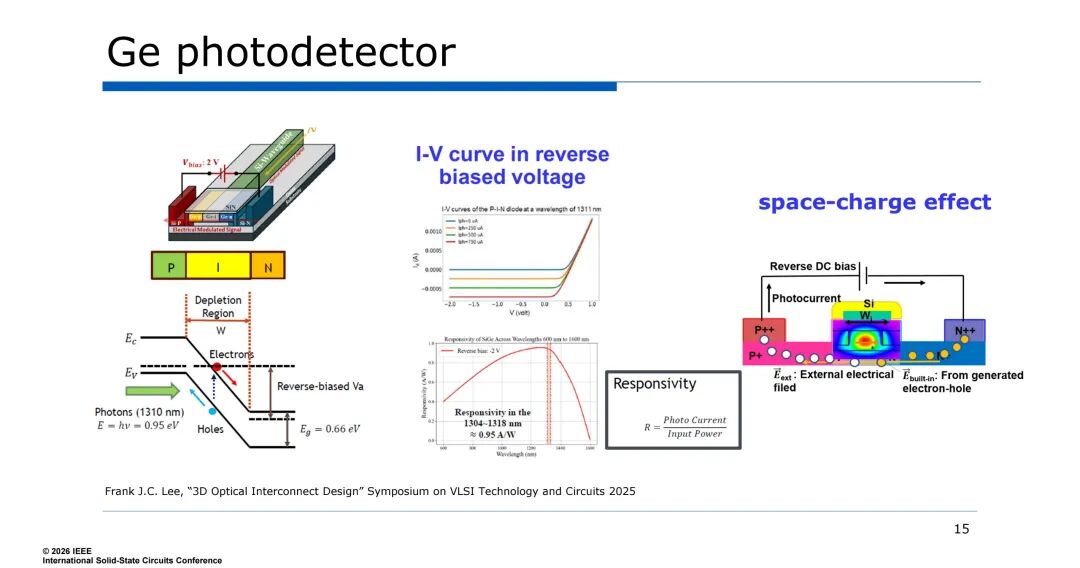

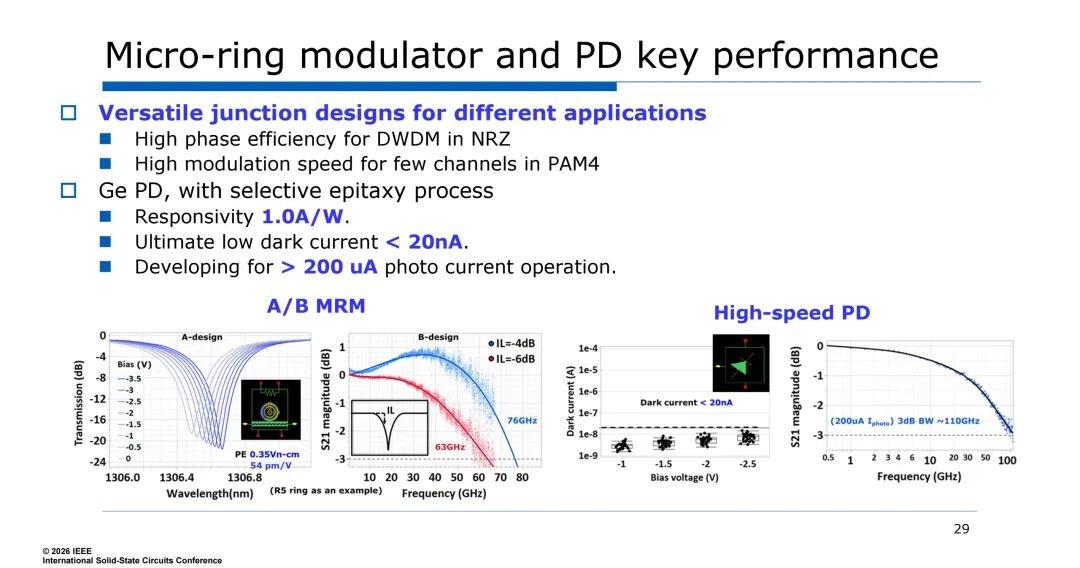

光电探测采用锗(Ge)光电探测器,基于反向偏置的PIN结构实现光电转换。1310nm波长的光子能量为0.95eV,大于锗的0.66eV禁带宽度,可在耗尽区激发产生电子-空穴对,在外加电场作用下形成光电流,响应度定义为光电流与输入光功率的比值。Ge光电探测器采用选择外延工艺制备,在1304-1318nm波段的响应度可达0.95-1.0A/W,暗电流可控制在20nA以下,可支持超过200μA的光电流工作,3dB带宽可达约110GHz,完全满足超高速率光链路的需求。

◆ 台积电硅光子学平台核心架构

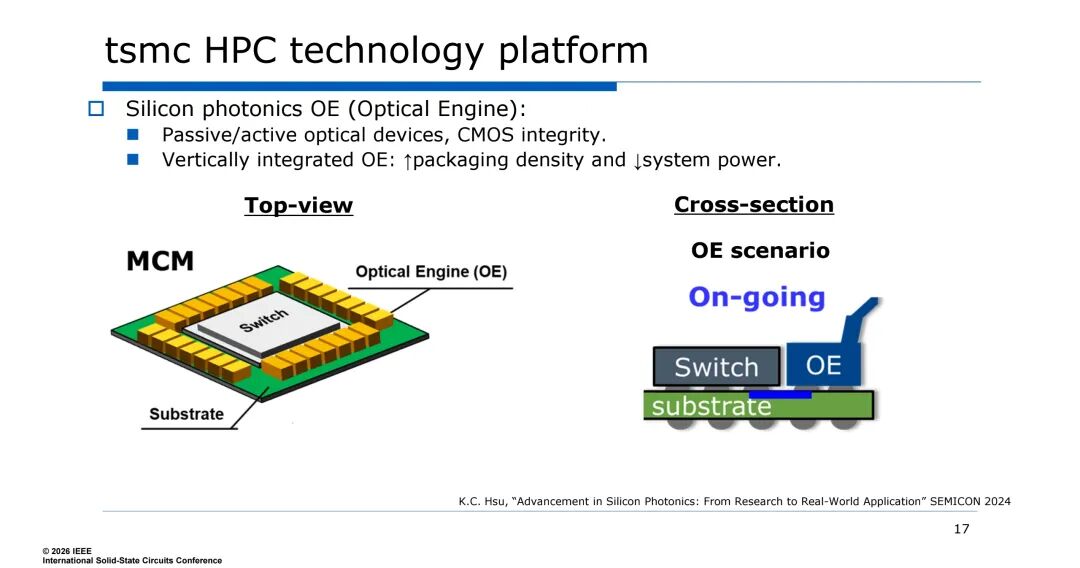

台积电面向下一代HPC与AI场景,推出了完整的硅光子学(SiPH)技术平台,核心是垂直集成的光引擎(OE),整合了无源/有源光器件与CMOS电路,通过垂直集成提升封装密度,降低系统功耗。

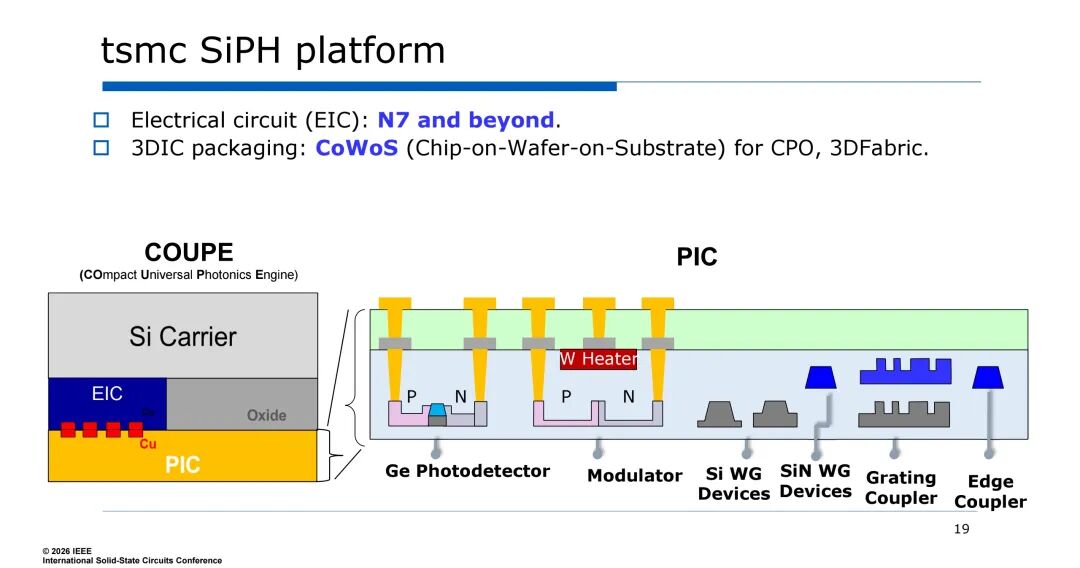

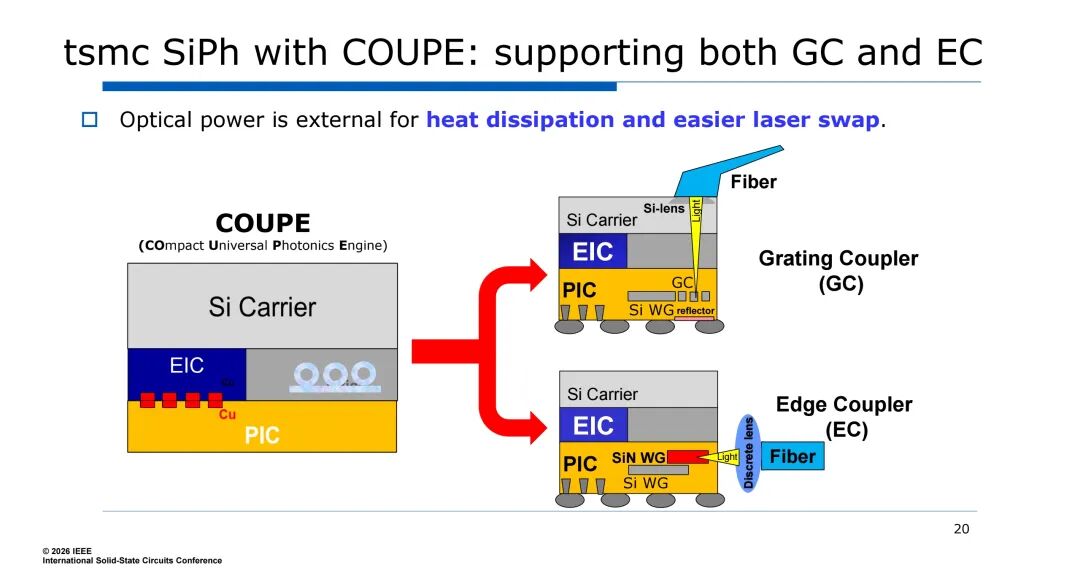

平台的核心是COUPE(Compact Universal Photonics Engine)紧凑型通用光子引擎架构,支持N7及更先进工艺节点的电芯片(EIC),配套台积电3DIC封装技术,包括面向CPO场景的CoWoS(Chip-on-Wafer-on-Substrate)封装与3DFabric技术,实现EIC与光子集成电路(PIC)的堆叠集成,其中EIC位于上层,PIC位于下层,实现了电与光的高密度协同集成。

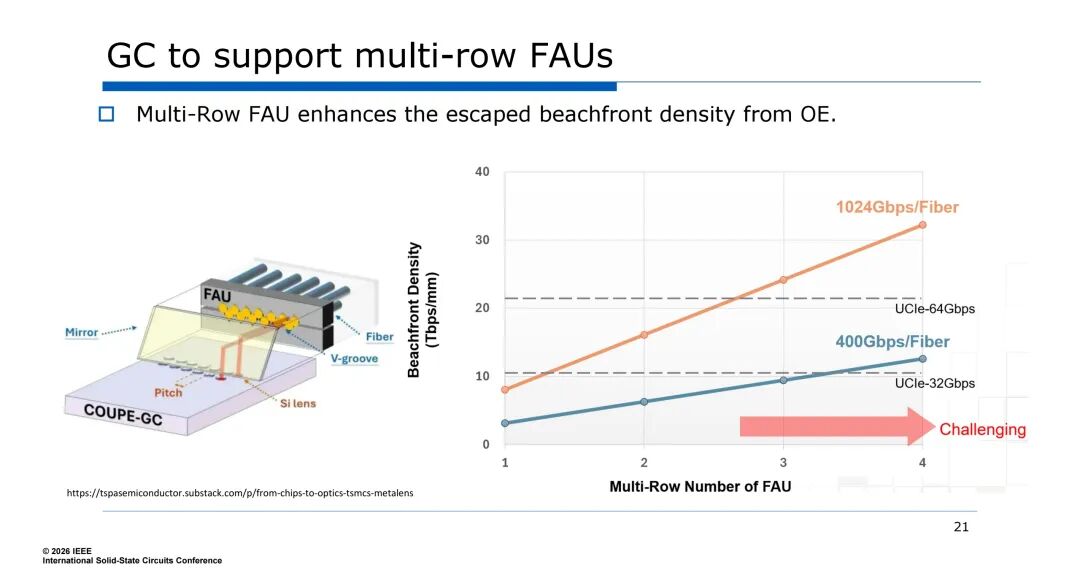

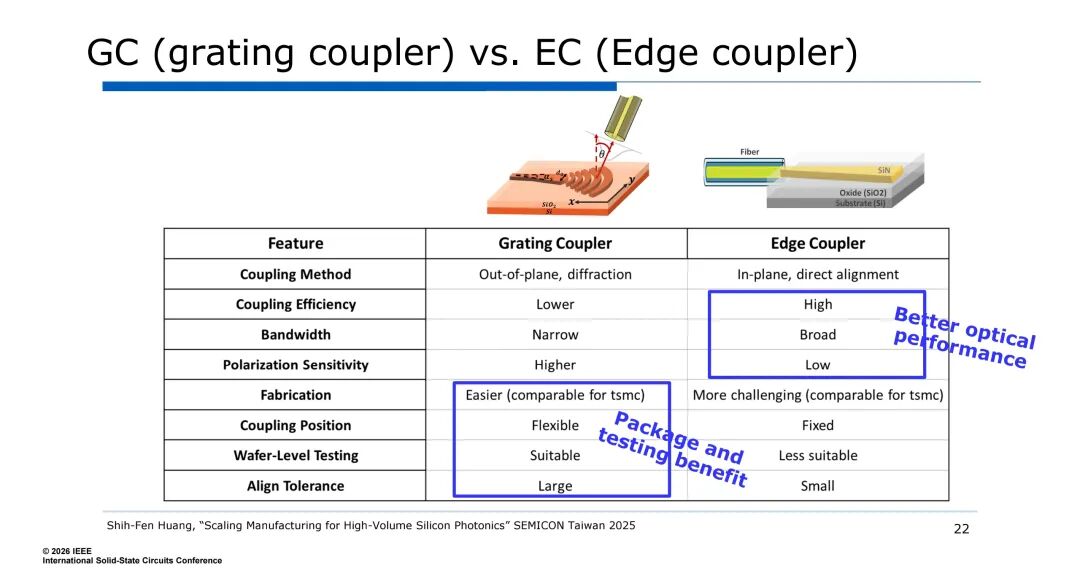

COUPE平台同时支持光栅耦合器(GC)与边缘耦合器(EC)两种光学耦合方案,光学功率采用外置设计,优化了系统散热性能,同时简化了激光器的更换与维护。光栅耦合器采用面外衍射的耦合方式,支持晶圆级测试,对准容差大,耦合位置灵活,可支持多排光纤阵列单元(FAU),大幅提升光引擎的端口密度,单光纤速率有望支持到1024Gbps(4列光纤)以及30Tbps/mm的边缘带宽密度,远超当时最先进的基于UCIe 64Gbps接口实现的21Tbps/mm;端面耦合器采用平面内直接对准的耦合方式,具备更高的耦合效率、更宽的工作带宽与更低的偏振敏感性,台积电的工艺优化使得两种耦合方案的制造难度差距显著缩小。

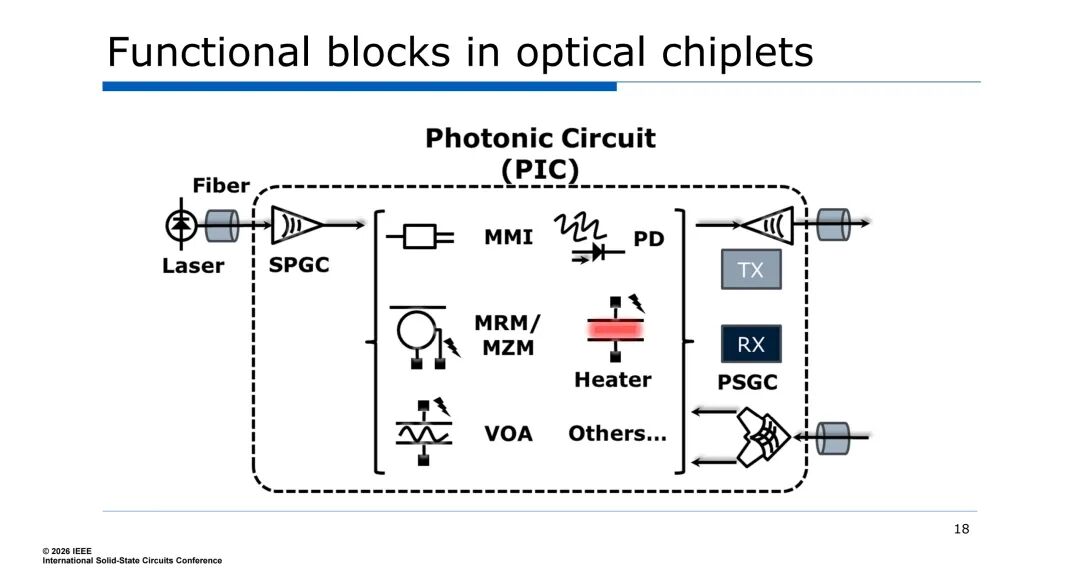

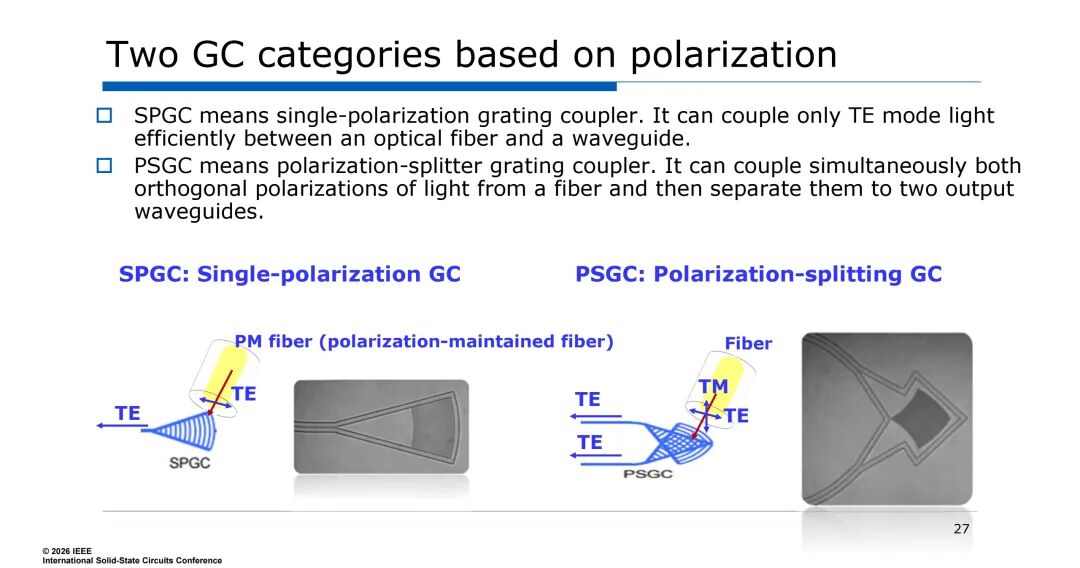

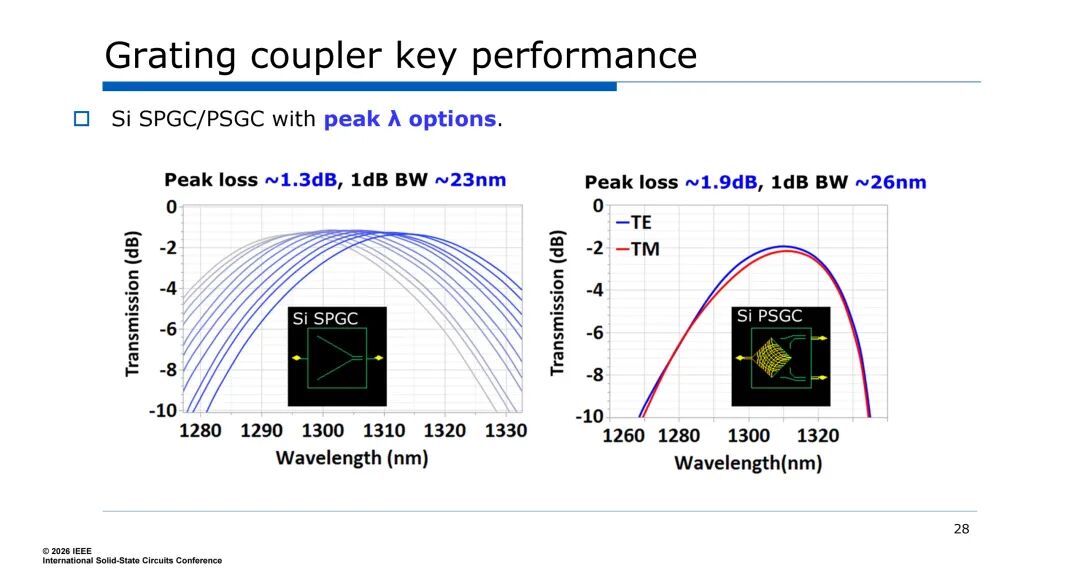

光栅耦合器分为两类核心架构:单偏振光栅耦合器(SPGC)与偏振分束光栅耦合器(PSGC)。SPGC仅能对TE模式的光实现光纤与波导间的高效耦合,适配保偏光纤应用场景;PSGC可同时耦合光纤中两个正交的偏振态,并将其分离到两个独立的输出波导,适配单模光纤的宽带应用场景。

◆ 量产化支撑:硅光子PDK与工艺优化

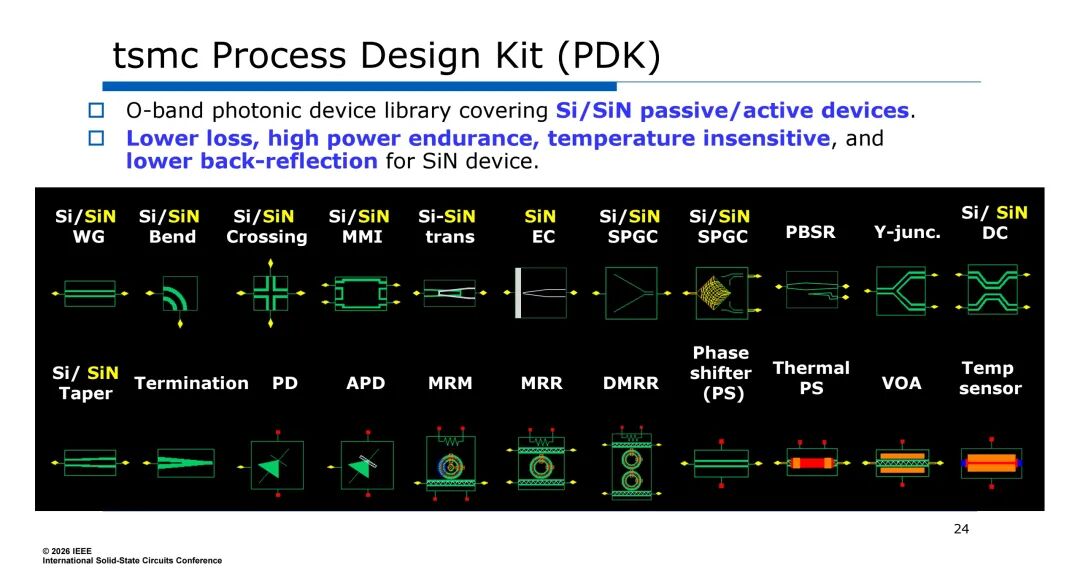

量产化硅光子技术的核心是成熟的工艺设计套件(PDK),台积电的SiPH PDK提供了覆盖O波段的完整Si/SiN无源与有源光器件库,其中SiN器件具备低损耗、高功率耐受、温度不敏感、低背向反射的核心优势。器件库涵盖了波导、弯曲结构、交叉结构、多模干涉耦合器(MMI)、光栅耦合器、边缘耦合器、偏振分束旋转器、热移相器、可调光衰减器(VOA)、微环调制器、微环谐振器、Ge光电探测器、雪崩光电二极管(APD)、温度传感器等全系列光子器件,为光子芯片设计提供了完整的基础模块。

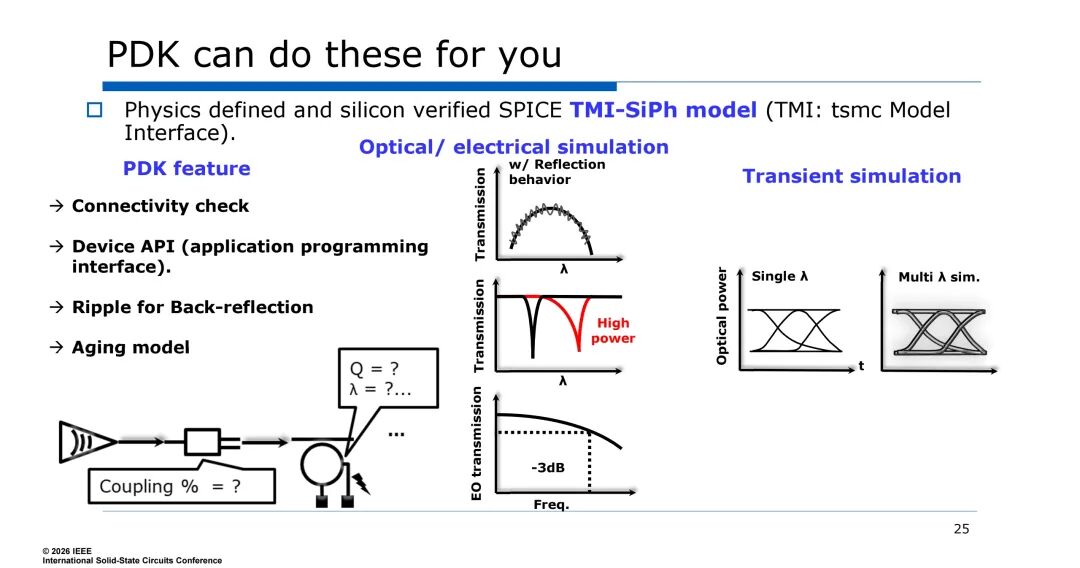

PDK的核心能力包括经过物理定义与硅验证的SPICE TMI-SiPh模型(台积电模型接口),支持完整的光电联合仿真、原理图连通性检查、器件API调用、背向反射导致的输出纹波分析、器件老化模型仿真,同时支持单波长与多波长的瞬态仿真,可完整模拟光传输中的反射行为,还可通过多波长瞬态眼图仿真完成链路串扰的评估,为光子芯片的设计、仿真与验证提供了全流程的支撑。

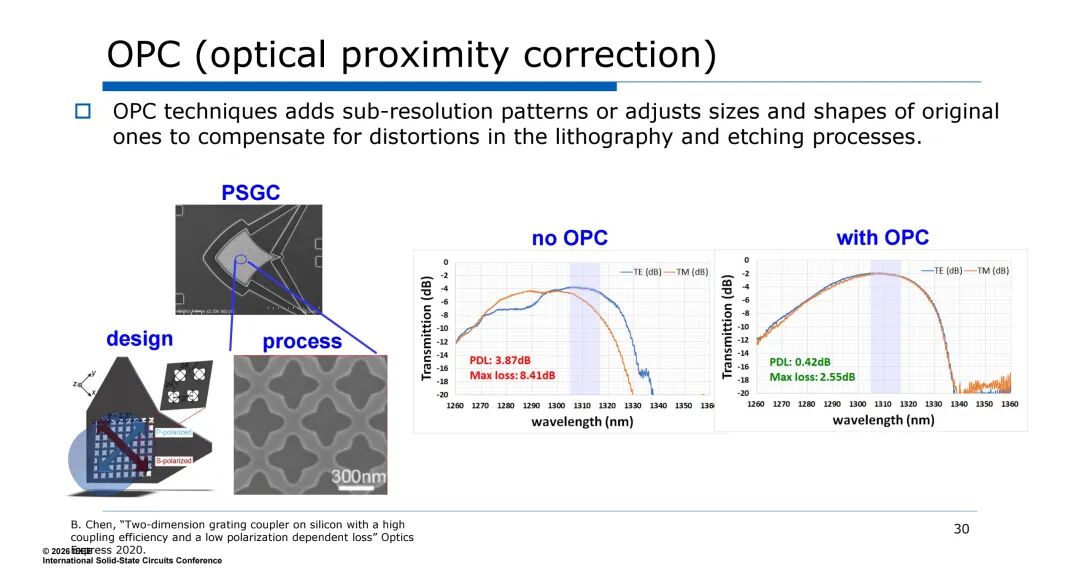

在工艺优化层面,台积电采用光学邻近校正(OPC)技术,通过添加亚分辨率的辅助图形,或调整原始图形的尺寸与形状,补偿光刻与刻蚀过程中产生的图形畸变,大幅提升了器件的性能一致性与良率。以PSGC为例,未经OPC优化的器件偏振相关损耗(PDL)达3.87dB,最大损耗8.41dB;经过OPC优化后,PDL降至0.42dB,最大损耗仅2.55dB,性能提升显著。

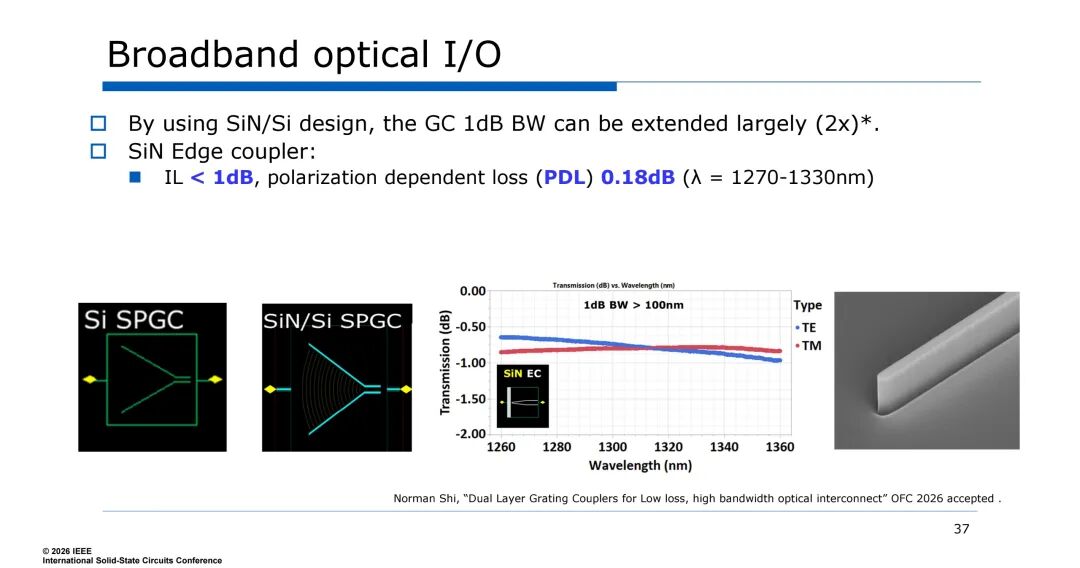

◆ 核心器件性能与光路实现

台积电SiPH平台的核心器件实现了业界领先的性能指标。在光栅耦合器方面,纯硅SPGC的峰值损耗约1.3dB,1dB带宽约23nm;纯硅PSGC的TE与TM模式峰值损耗约1.9dB,1dB带宽约26nm;基于SiN/Si复合结构的SPGC,1dB带宽可扩展至100nm以上,达到纯硅方案的2倍;SiN边缘耦合器在1270-1330nm的宽波段范围内,插入损耗低于1dB,偏振相关损耗仅0.18dB,具备优异的宽带性能。

在调制器与探测器方面,MRM提供了多种结型设计,适配不同的应用场景:面向DWDM NRZ应用的方案实现了54pm/V和0.35Vcm的高调制效率,面向少通道高速PAM4应用的高速方案实现了76GHz的3dB带宽;Ge光电探测器采用选择性外延工艺,响应度达1.0A/W,暗电流低于20nA,可支持超过200μA的光电流工作,3dB带宽可达约110GHz,满足超高速率链路的需求。

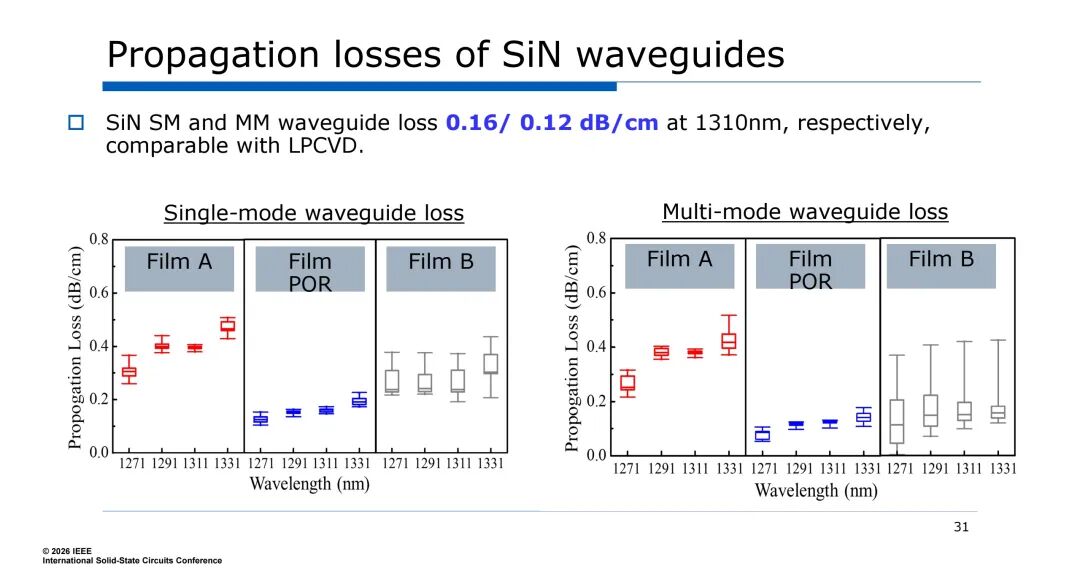

在波导与无源器件方面,PECVD SiN波导实现了业界领先的低损耗性能,在1310nm波长下,单模波导损耗低至0.16dB/cm,多模波导损耗低至0.12dB/cm,与LPCVD工艺的性能水平相当。

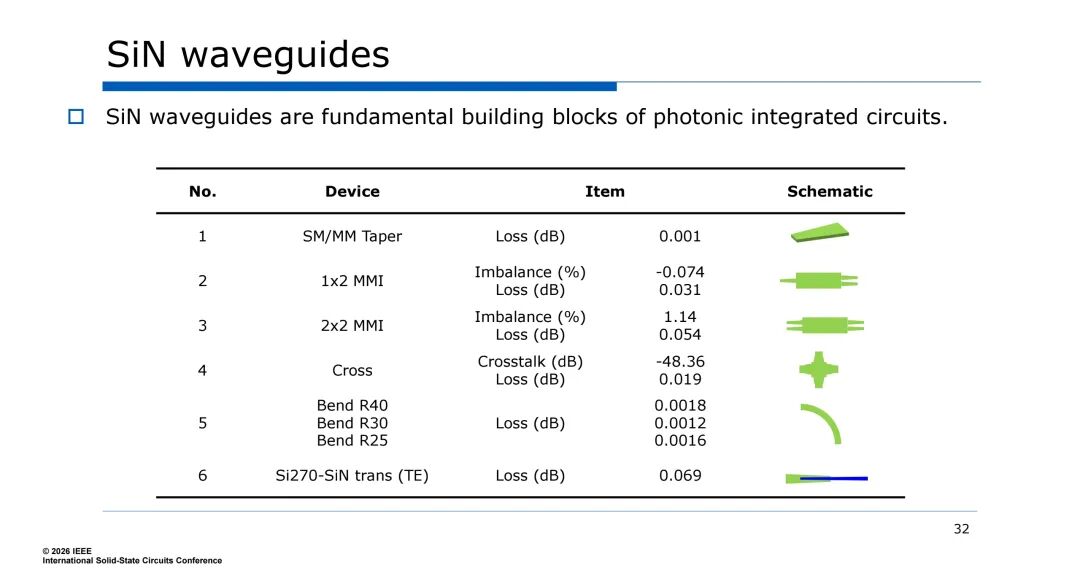

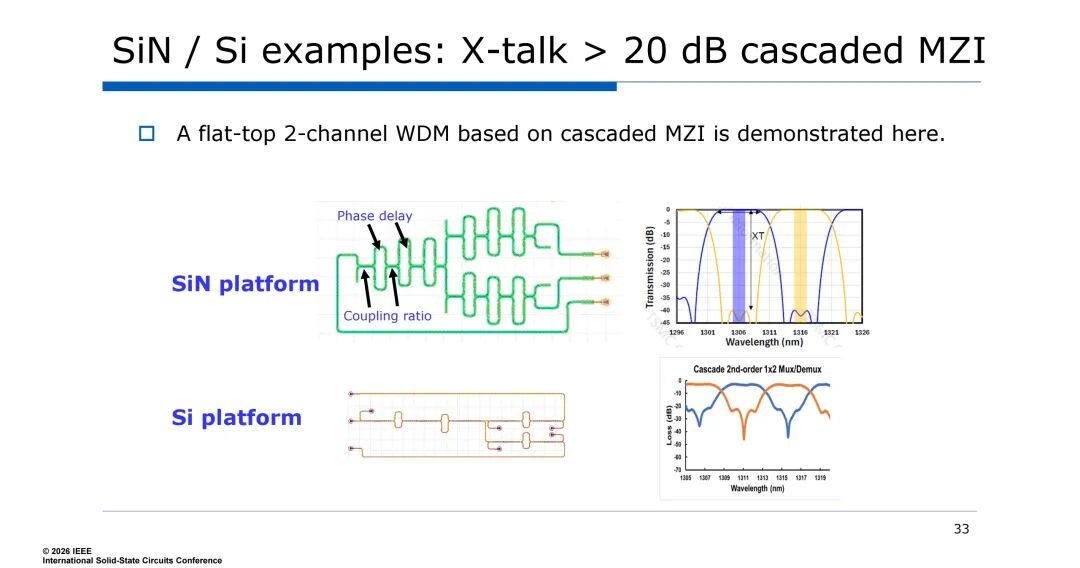

配套的无源器件也实现了极低的损耗与串扰:单模/多模taper结构的损耗仅0.001dB,1×2 MMI的损耗为0.031dB,不平衡度仅-0.074%;2×2 MMI的损耗为0.054dB,不平衡度1.14%;波导交叉结构的串扰低于-48.36dB,损耗仅0.019dB;不同半径的弯曲结构损耗最低可达0.0012dB;硅到氮化硅的模式转换结构损耗仅0.069dB。同时,基于SiN与Si平台,实现了串扰优于20dB的级联MZI结构,完成了平顶响应的2通道WDM器件验证。无源器件的性能相比去年OFC的报道有了一些提升。

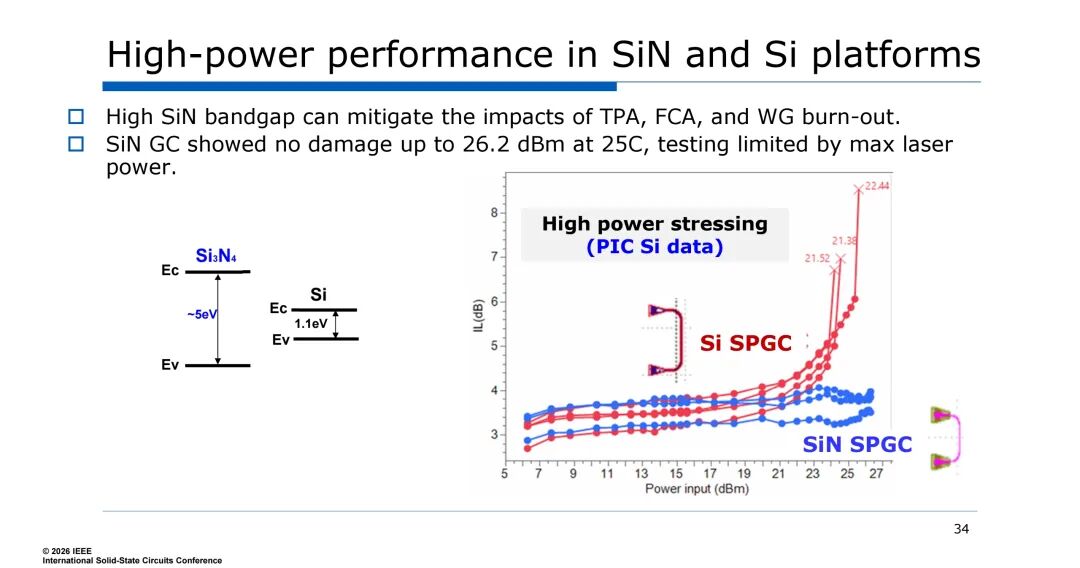

在高功率性能方面,SiN的宽禁带特性可有效缓解双光子吸收(TPA)、自由载流子吸收(FCA)与波导烧毁的问题,大幅提升了器件的高功率耐受能力。测试结果显示,SiN SPGC在25℃环境下,输入光功率高达26.2dBm时仍未出现损伤,测试上限受限于激光器的最大输出功率,远优于硅基SPGC的高功率耐受性能。

◆ WDM使能技术与容量扩展路径

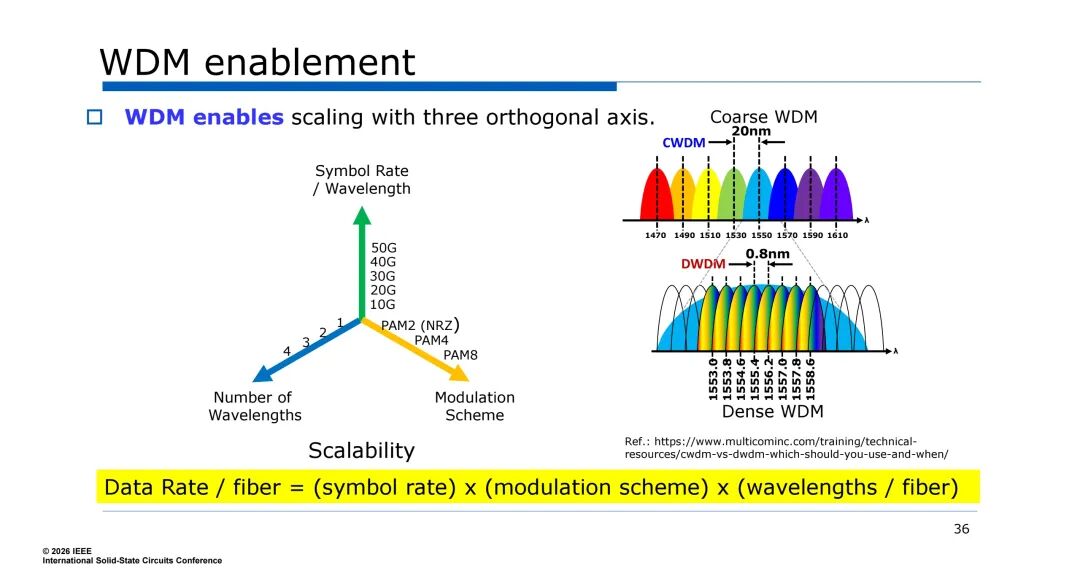

波分复用(WDM)是实现单光纤速率持续缩放的核心技术,通过符号率、调制格式、波长数量三个正交维度的扩展,实现单光纤容量的提升,其核心关系为:单光纤数据速率=符号率×调制阶数×单光纤波长数。根据通道间隔的不同,WDM可分为粗波分复用(CWDM)与密集波分复用(DWDM),其中CWDM的通道间隔为20nm,DWDM的通道间隔可低至0.8nm,可实现单光纤数十甚至上百个波长的复用。

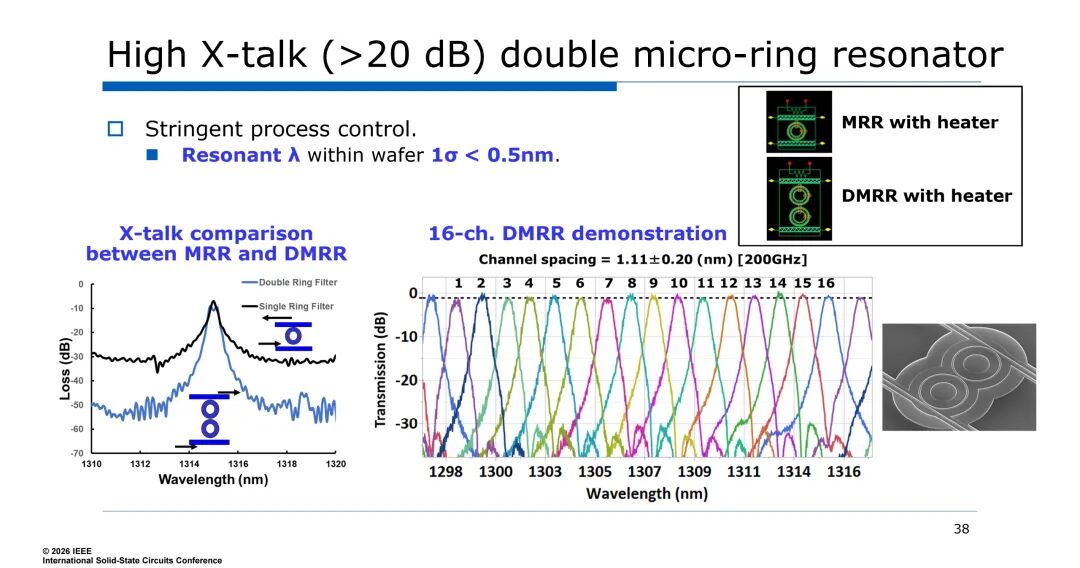

台积电为WDM系统提供了完整的器件与技术支撑,除了前述的宽带光I/O器件外,还实现了高性能的WDM滤波器件。针对DWDM场景,开发了双微环谐振器(DMRR)滤波器,相比传统的单微环谐振器(MRR),DMRR实现了更优异的带外抑制性能,串扰水平大幅优化;通过严苛的工艺控制,晶圆内谐振波长的1σ偏差小于0.5nm,成功验证了通道间隔1.11±0.20nm(对应200GHz频率间隔)的16通道DMRR器件,通道串扰优于20dB,为高密度DWDM系统提供了核心的滤波器件支撑。

◆ 结论

台积电的COUPE硅光子学平台,提供了完整的光芯粒设计与封装服务,实现了N7及更先进工艺节点EIC与基于硅、氮化硅波导的PIC的堆叠集成,配套的PDK提供了全面的设计与仿真能力,包括原理图连通性检查、器件API、可靠性数据、背向反射纹波分析、多波长瞬态眼图仿真等全流程功能。

通过在PDK、器件性能、工艺均匀性方面的持续创新,台积电的硅光子学平台正在支撑下一代高速、高能效光通信系统的发展,其应用场景覆盖了当前AI服务器的scale-out、scale-up互联,以及未来的片内光通信,为突破电互连的物理极限、支撑HPC与AI算力的持续增长提供了核心技术路径。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-03-04,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读