Chiplet通信桥接技术介绍及大厂方案分析(一)

今天接着翻译Flip Chip, Hybrid Bonding, Fan-In, and Fan-Out Technology这本书第五章Chiplet Communication(Bridge),篇幅比较长,分为上下两篇,上半部分翻译背景和技术细节,下半部分翻译Intel、IBM、AMD、TSMC等大厂的一些Chiplet技术方案。

5.1 引言

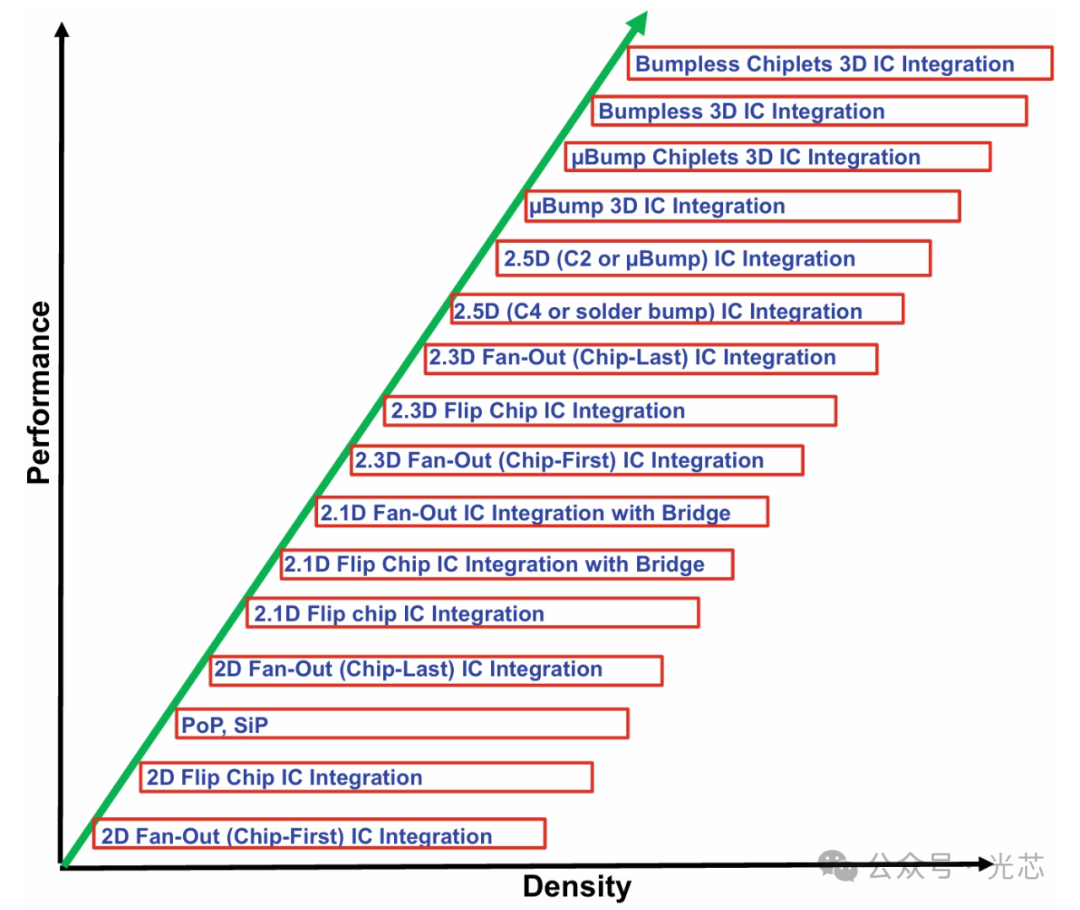

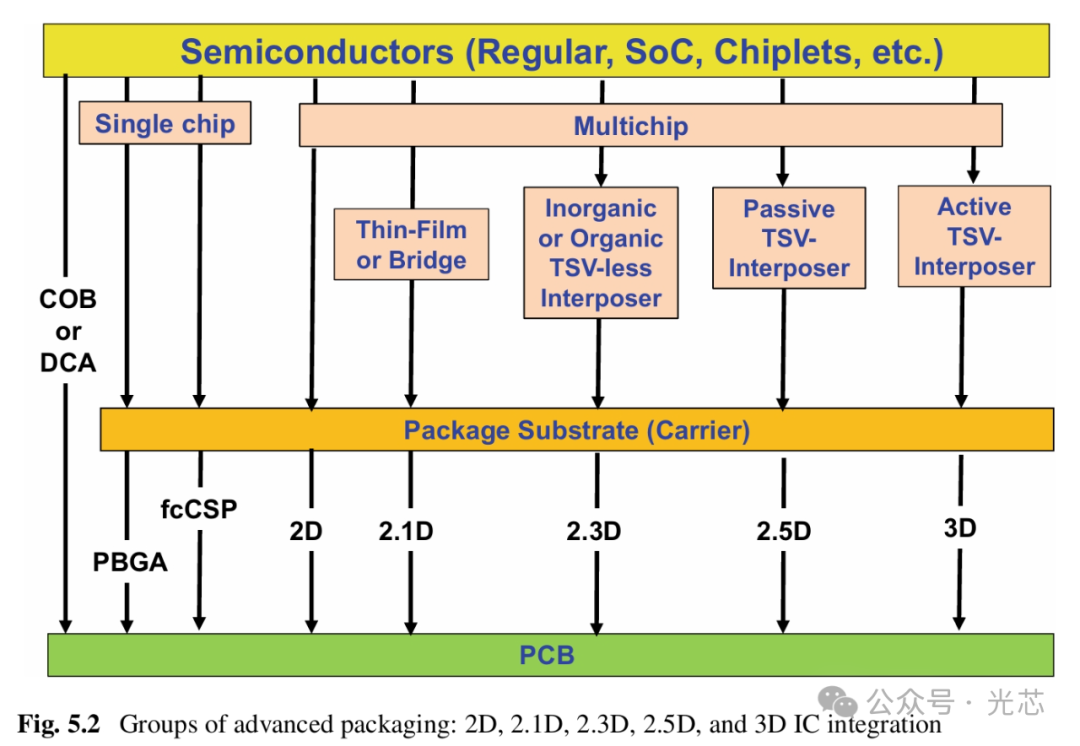

上图5.1展示了各种先进的封装技术以及它们的性能和密度排名。图5.2展示了包括2D、2.1D、2.3D、2.5D和3D IC集成在内的先进封装技术分类。本章的重点在于chiplet和异构集成,尤其是chiplet通信。chiplet和异构集成的主要区别在于,“chiplet”是一种芯片设计方法,而“异构集成”是一种芯片封装方法。

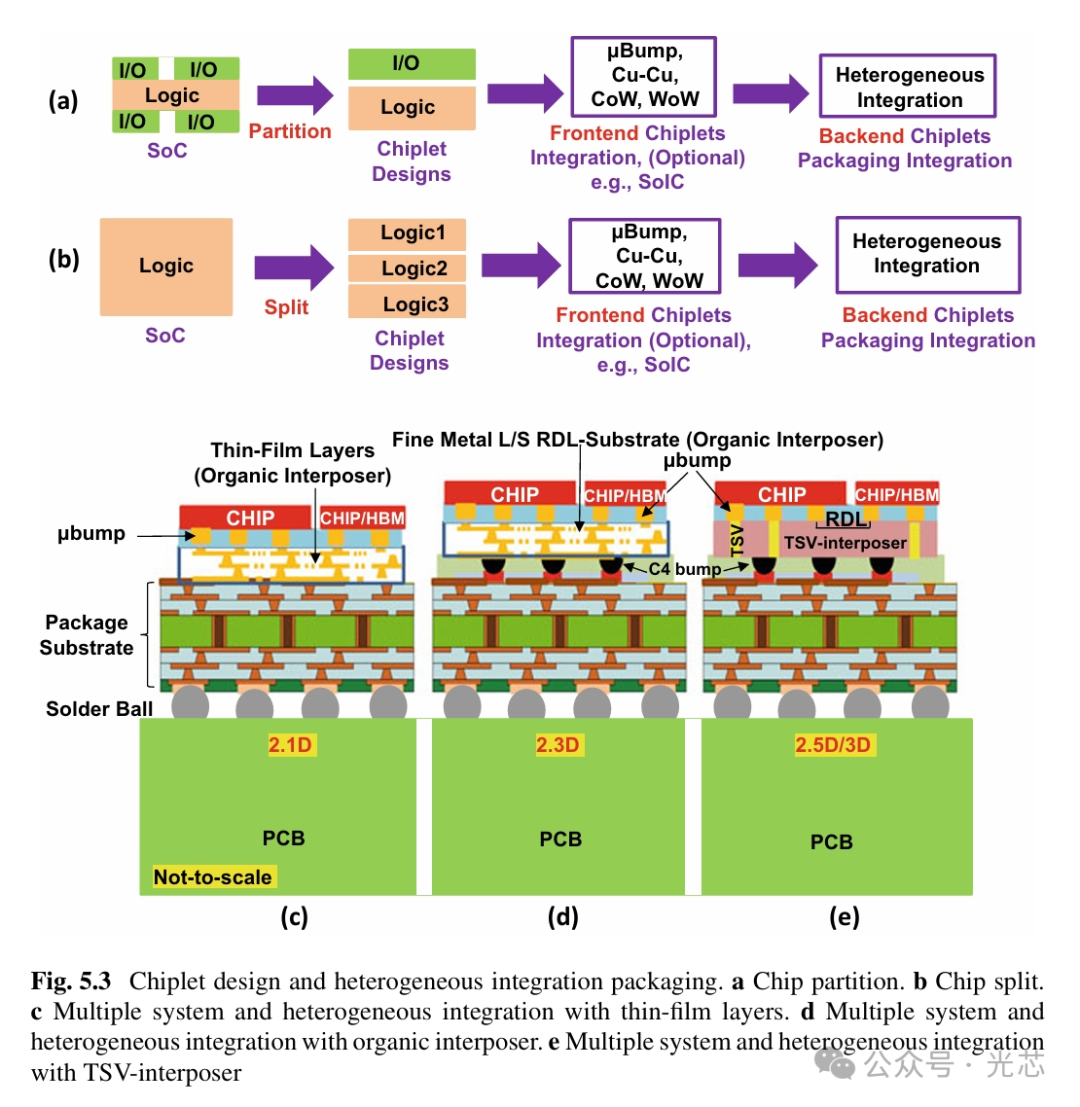

当前至少有5种不同的chiplet设计和异构集成封装方法,如图5.3所示,即:

(1)芯片分割(chip partition)和异构集成(由成本和技术优化驱动),图5.3a;

(2)芯片分片(split)和异构集成(由成本和半导体制造产量驱动),图5.3b;

(3)多个系统与薄膜层直接异构集成在积层(build -up)基板顶部(2.1D IC集成),图5.3c;

(4)多个系统与无TSV interposer中介层异构集成(2.3D IC集成),图5.3d;

(5)多个系统与带TSV中介层异构集成(2.5D和3D IC集成),图5.3e。

(3)-(5)由封装形态form factor和性能驱动。

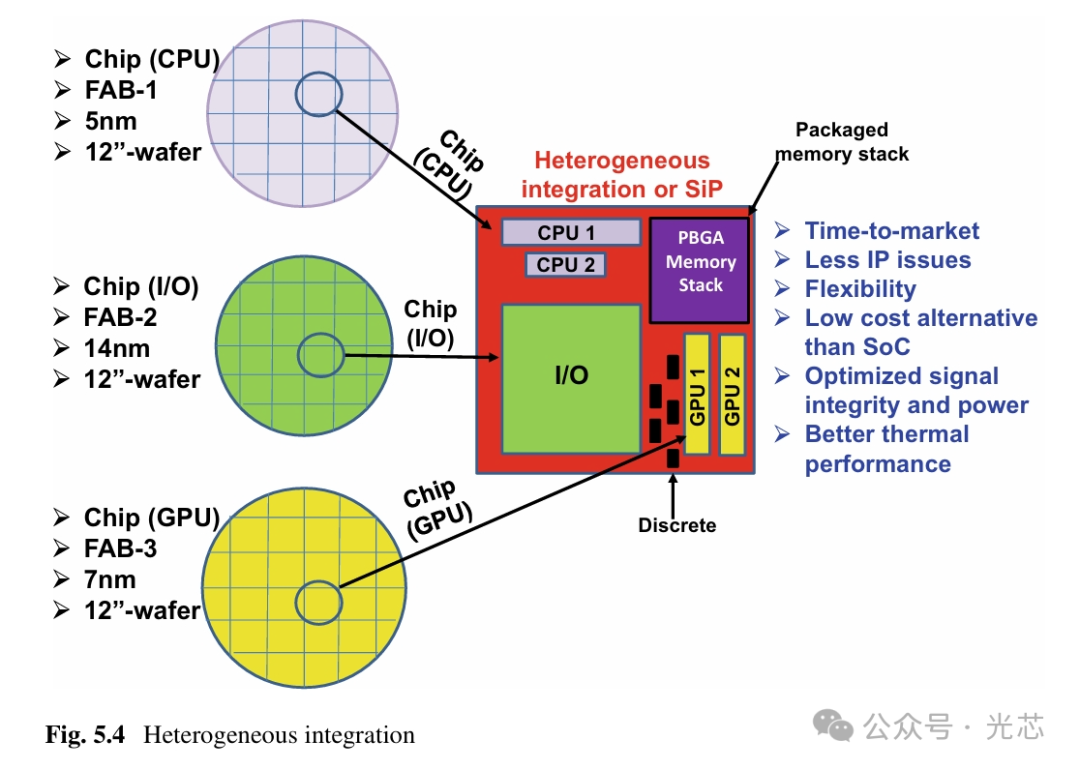

在芯片分割partition和异构集成中,图5.3a,SoC大芯片(例如逻辑和I/O)按功能分割成小芯片chiplet:逻辑和I/O。这些芯片可以通过前端CoW(chip-on-wafer)或WoW(wafer-to-wafer)方法堆叠集成,然后使用异构集成技术组装在同一封装基板上,如图5.4所示。需要强调的是,前端芯片的集成可以获得更小的封装面积和更好的电气性能。

在芯片分片split和异构集成中,图5.3b,SoC(例如逻辑)大芯片被分割成更小的芯片,例如logic1、logic2和logic3。这些芯片可以通过前端CoW或WoW方法堆叠,然后使用异构集成技术组装在同一基板上,如图5.4所示。同样,芯片前端的集成是可选的。

在多个系统与薄膜层直接在积层(build-up)封装基板顶部异质集成的情况下,图5.3c,SoC(例如CPU、逻辑和HBM)由带有薄膜层的积层基板支持。这是由性能和封装形态驱动的,适用于高密度和高性能应用。由于积层基板的平整性有难度,这种集成方式的产量损失非常高,目前尚未大规模生产。

在无TSV中介层异构集成的方案中,图5.3d,SoC(例如CPU、逻辑和HBM)由带有精细金属RDL层的有机interposer支撑,然后封装到积层基板上。这是由性能和封装形态因素驱动的,适用于高密度和性能应用。这种集成目前正处于小批量生产中。

在TSV中介层异构集成的方案中,图5.3e,SoC(例如CPU、逻辑和HBM)由无源(2.5D)或有源(3D)TSV中介层和积层基板封装。这同样是由性能和封装形态因素驱动的,适用于极高密度和高性能应用。这种集成目前已在大规模生产中。

chiplet设计和异构集成封装的优势包括:(a)在半导体制造过程中提高产量(降低成本);(b)快速推向市场;(c)在设计过程中降低成本;(d)更好的热性能;(e)可重用的知识产权(IP);以及(f)模块化。

挑战包括:(a)接口区域增加;(b)封装成本更高;(c)封装复杂性和设计工作量增加;以及(d)过去的方法不太适用。因此,封装技术专家的主要关注点之一是减少芯片之间通信的接口区域和封装成本。

本章将系统介绍和讨论各种用于chiplet设计和异构集成封装通信的桥接技术,例如(a)嵌入在有机基板顶部的桥接,(b)嵌入在扇出环氧模塑化合物(EMC)中RDLs的桥接,以及(c)柔性桥接技术,还将提供一些挑战和建议。

5.2 背景

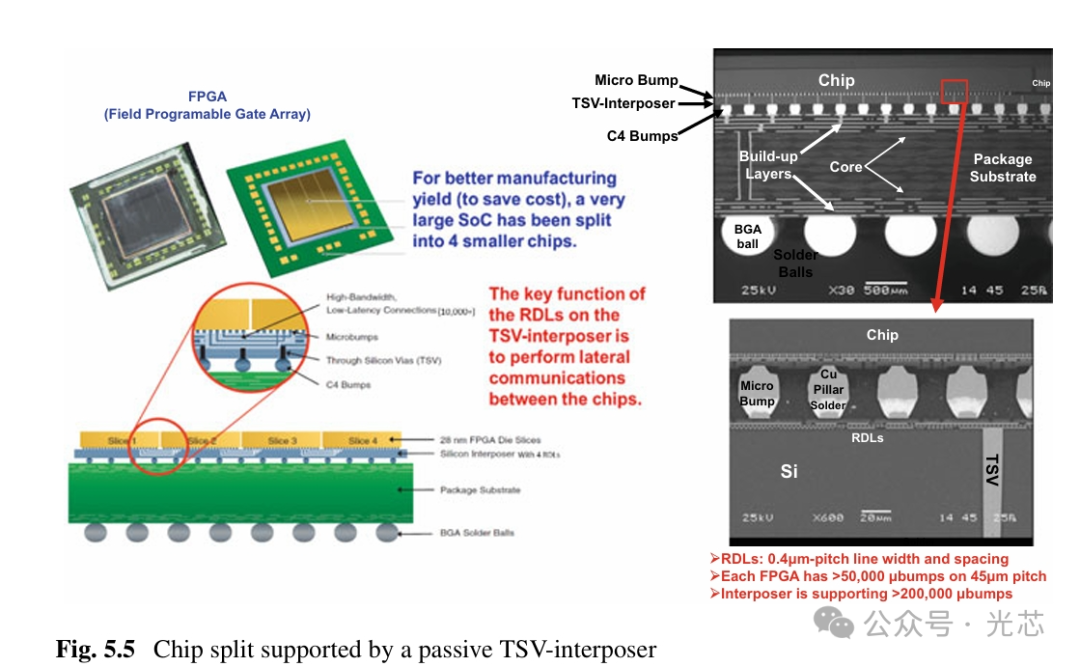

过去,chiplet设计和异构集成封装的通信是通过带精细金属导线的TSV-interposer、积层高密度有机基板和扇出RDL来实现的。图5.5展示了Xilinx在2013年推出的Virtex-7 HT系列。2011年,Xilinx要求TSMC使用28nm工艺技术制造其FPGA SoC芯片。由于芯片尺寸较大,良率非常差。然后,Xilinx重新设计并将大型FPGA分割成四个较小的芯片,如图5.5所示,TSMC以高良率的28nm工艺制造了这些小芯片,并用CoWoS技术进行封装。CoWoS是一种2.5D IC集成,是实现这四个芯片横向通信的关键基板。TSV-interposer上的四个重分布层(RDLs)的最小节距为0.4um。TSV-interposer因其制造良率损失(TSV-interposer的尺寸非常大,即使是64nm工艺)而成本非常高。

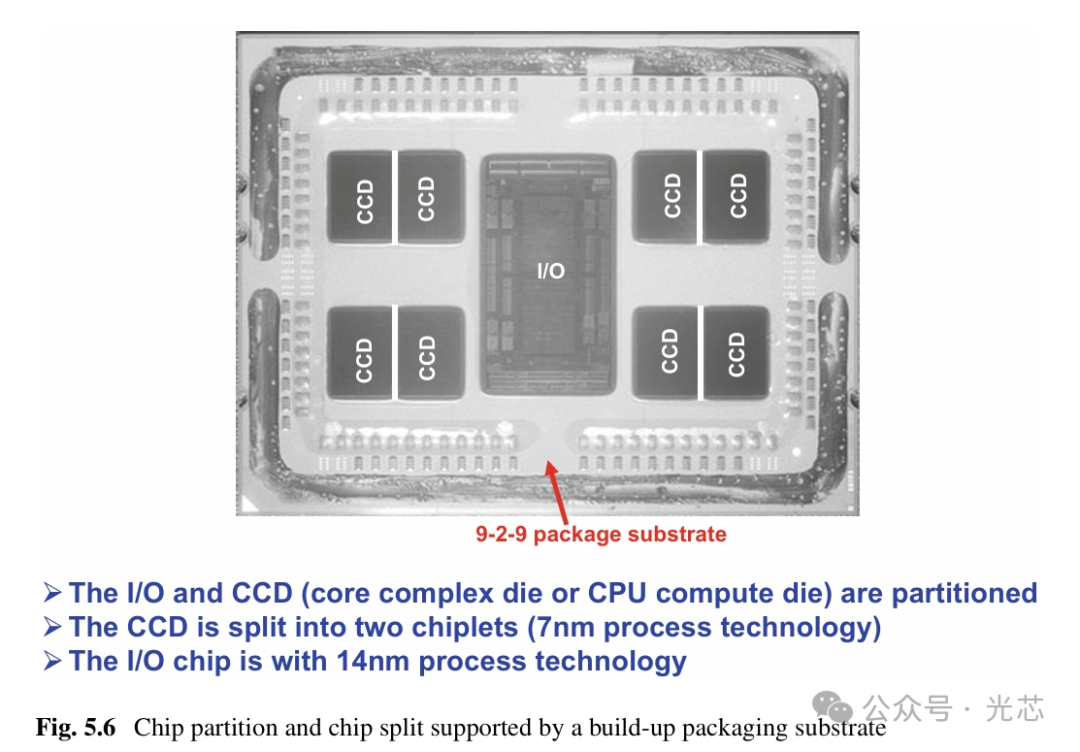

图5.6展示了AMD在2019年中期推出的第二代高性能(EPYC)服务器处理器,7002系列。AMD的解决方案之一是将SoC分割成小芯片chiplet,用最先进的CMOS工艺加工CPU,而将I/O和存储器则用了n-1代的工艺加工。

另一种解决方案是将CPU核心分片成更小的芯片。在这种情况下,每个核心复合芯片单元(CCD)或CPU计算芯片被分割成两个较小的芯片。2019年初,AMD使用了台积电(TSMC)昂贵的7nm工艺技术用于核心CCD芯片,并将DRAM和逻辑芯片转移到GlobalFoundries 14nm工艺进行加工。第二代EPYC芯片是一种2D芯片IC集成技术,即所有芯片并排放置在一个9-2-9积层封装基板上,这种20层带细金属导线的有机基板并不便宜。

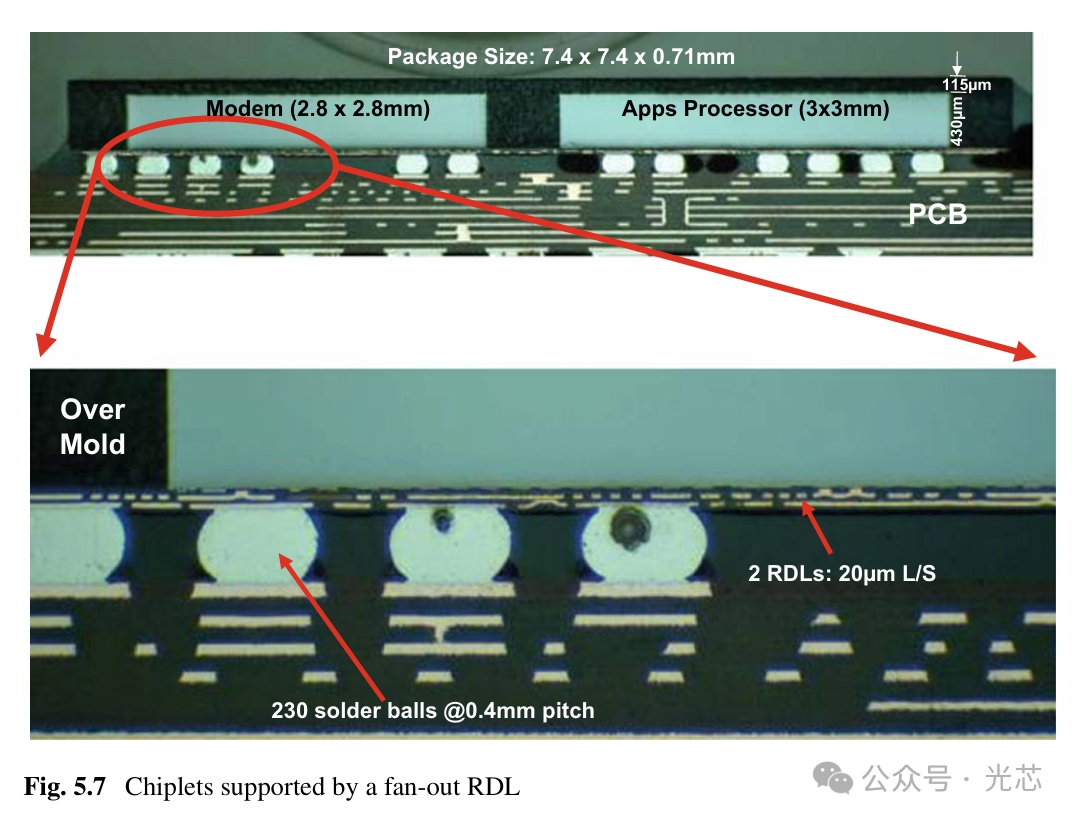

图5.7展示了2013年推出的HTC(Desire 606 W)智能手机中的应用处理器芯片组。应用处理器芯片组是SPREADTRUM SC8502,这是通过扇出芯片优先chip-first工艺异构集成的modem和应用处理器。这些芯片由扇出2层重分布层(RDLs)基板支持,然后在印刷电路板(PCB)上焊接。

需要注意的是,芯片之间的通信(RDLs)要求是精细金属导线L/S/H,并且只分布在chiplet的非常小和局部区域内,并不需要使用整个TSV-interposer、整个有机基板或整个扇出RDLs来支持芯片之间的通信。因此,业界提出了使用小面积的局部精细金属RDL桥接芯片以执行通信(以降低成本)的chiplet设计和异构集成封装的概念,这也是当今非常热门的话题。至少有两种不同的桥接设计,即刚性桥和柔性桥。

5.3 刚性桥与柔性桥

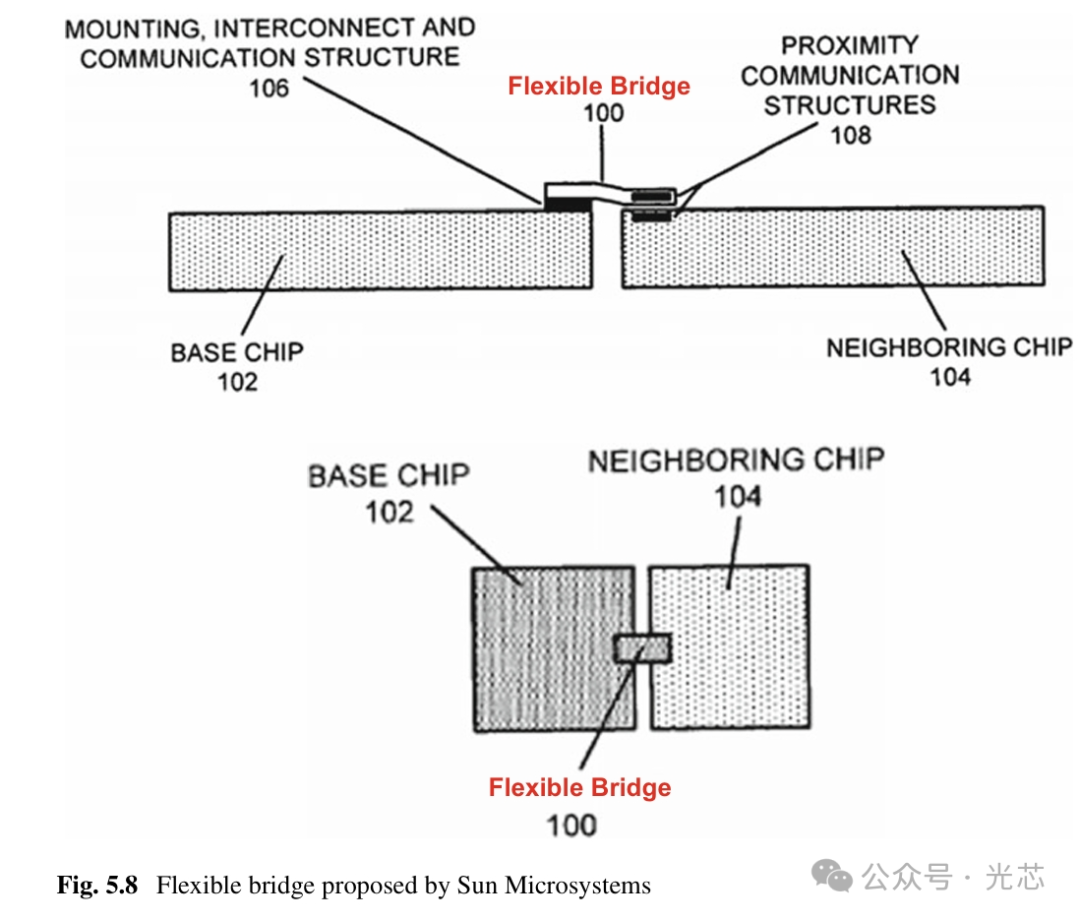

柔性桥其实就是RDL本身,它有精细金属L/S/H导线和介电聚合物如PI组成。第一个柔性桥专利申请US 2006/0095639 A1由SUN Microsystems(后来被甲骨文收购)于2004年11月2日提交(图5.8)。对于高速和高频应用,如毫米波频率,介电层也可以是液晶聚合物(LCP),称为LCP-柔性桥。柔性桥不在本书讨论范围内。

今天,大多数带有桥接的产品和文章都是刚性桥。刚性桥由RDLs和基板组成。大多数刚性桥都是用硅基板制成的,RDL是在硅晶圆上制造的。一些刚性桥甚至带有TSV。刚性桥有两类,即(1)带有积层基板的刚性桥和(2)带有扇出RDL基板的刚性桥。

5.4 如何制造带有TSV的硅桥?

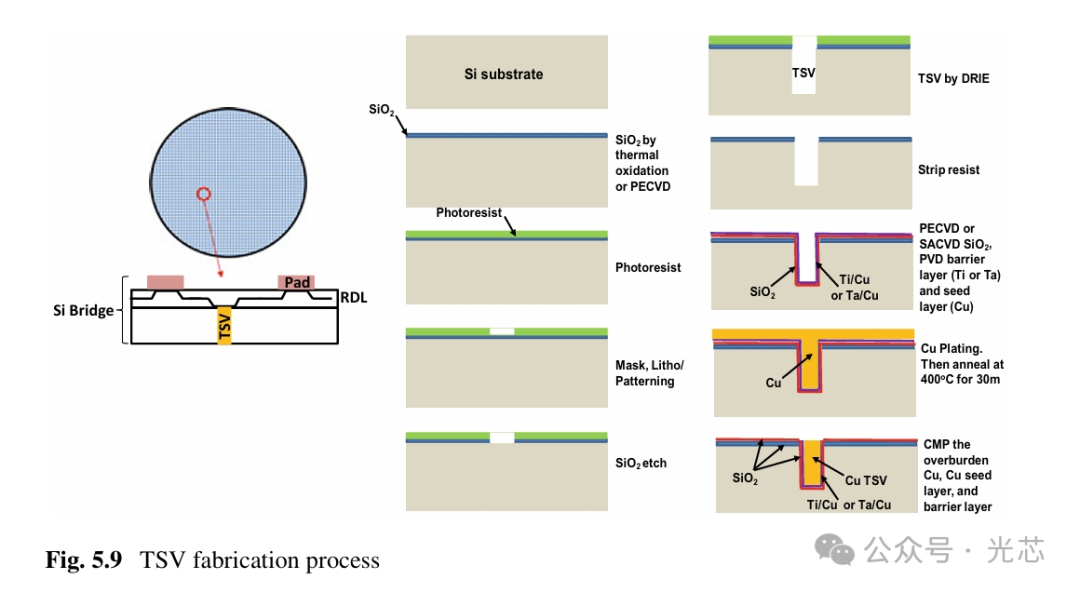

5.4.1 TSV的制造过程

TSV的制造过程如图5.9所示。该过程从通过热氧化或PECVD的SiNx/SiOx绝缘层开始,如图5.9所示。在光刻和TSV光刻之后,通过Bosch型DRIE(深反应离子蚀刻)将TSV蚀刻到Si基板中,形成高宽比10.5的通孔结构。然后,蚀刻后的TSV结构通过SACVD(亚大气压化学气相沉积)的SiOx衬里(liner)、Ta刻蚀阻挡层和PVD(物理气相沉积)的Cu种子层进行处理。随后使用Cu电镀填充TSV结构。最终的盲孔TSV顶部开口直径约为10um,深度约为105um,宽高比为10.5。在如此高的宽高比通孔结构中,采用自下而上的电镀机制,可以确保Cu厚度无需很厚就可以实现无缝通孔。

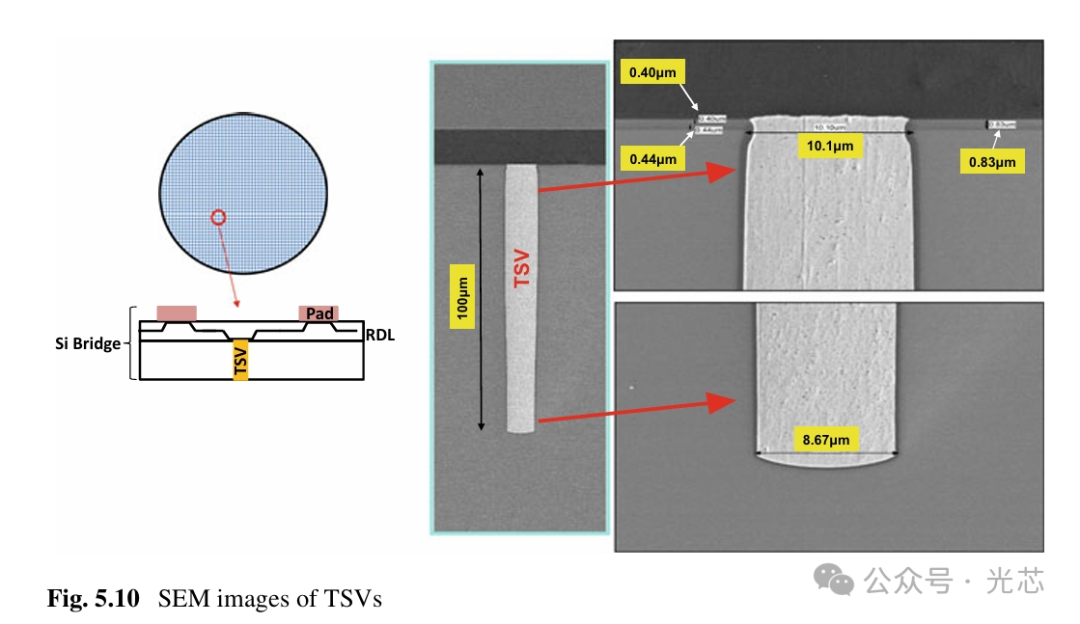

SEM横截面图像如图5.10所示。可以看出,TSV的直径在底部略微减小,这在蚀刻过程中是可以预见的。电镀后在400°C下进行30分钟退火,然后通过CMP(化学-机械抛光)去除表面多余的Cu。

5.4.2 在TSV上制造RDL

通常,RDL由介电层和金属导电层组成。至少有两种方法可以制造RDLs。

第一种方法是使用聚合物,如聚酰亚胺(PI)PWDC 1000(Dow Corning)、苯并环丁烯(BCB)cyclotene 4024-40(Dow Chemical)、聚苯并双噁唑(PBO)HD-8930(HD Micro Systems)和氟化芳香族AL-X 2010(Asahi Glass Corporation)制作介电层,通过电镀(如Cu)制作金属层。

第二种方法是Cu damascene方法,主要修改自传统的半导体后端线路以制作Cu金属RDL。通常,Cu damascene方法可以获得更薄的结构(介电层和Cu RDLs)、更细的节距、更小的线宽和线间距。首先介绍聚合物/Cu电镀方法。

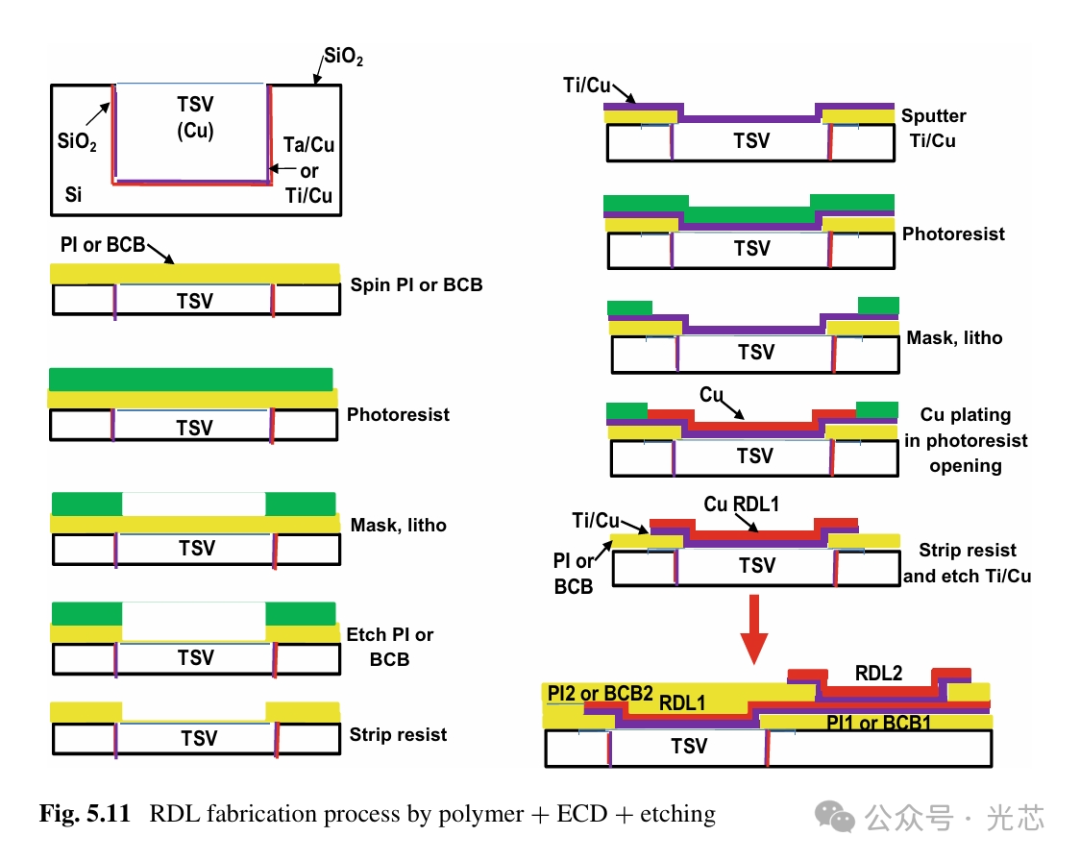

(A)制造RDLs:聚合物+Cu电镀和蚀刻方法

继续用图5.9和5.10中的晶圆加工,通过聚合物制造RDLs的制造过程如图5.11所示。

1. 在晶圆上旋转聚合物,如PI或BCB,并固化1小时,固化后的厚度为4-7um。

2. 光刻,在PI或BCB上打开通孔图形。

3. 蚀刻PI或BCB。

4. 去除光刻胶。

5. 在整个晶圆上溅射Ti和Cu。

6. 光刻,形成RDL窗口。

7. 在开窗区域电镀Cu。

8. 去除光刻胶。

9. 蚀刻Ti/Cu,完成RDL1。

10. 重复步骤1-9以制作RDL2,依此类推。

11. 重复步骤1(用于UBM)。

12. 光刻,在PI或BCB上打开所需焊盘的通孔,并RDL。

13. 在PI或BCB上蚀刻所需通孔。

14. 去除光刻胶。

15. 在整个晶圆上溅射Ti和Cu。

16. 光刻,开窗暴露UBM区域。

17. 电镀Cu核心层。

18. 去除光刻胶。

19. 蚀刻Ti/Cu。

20. 无电镀Ni和浸金。UBM完成。

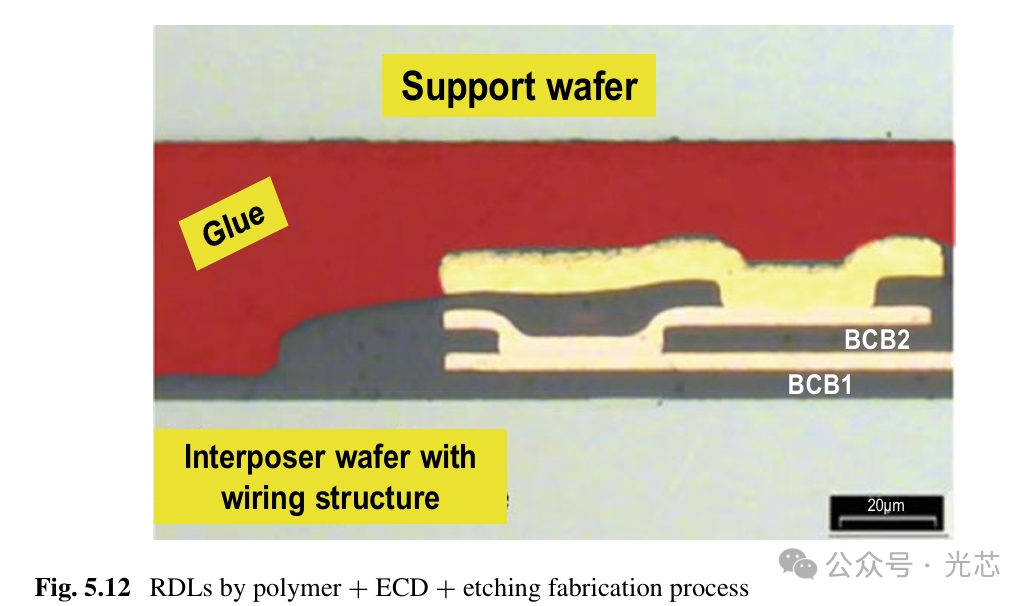

典型的带有聚合物(例如BCB)作为钝化层,Cu电镀作为金属层的RDL如图5.12所示。可以看出,钝化层BCB1和BCB2的厚度约为6-7微米,RDL约为4微米。应注意,光刻可以直接应用于PI或BCB以获得更大的尺寸。在这种情况下,不需要第一组光刻胶。

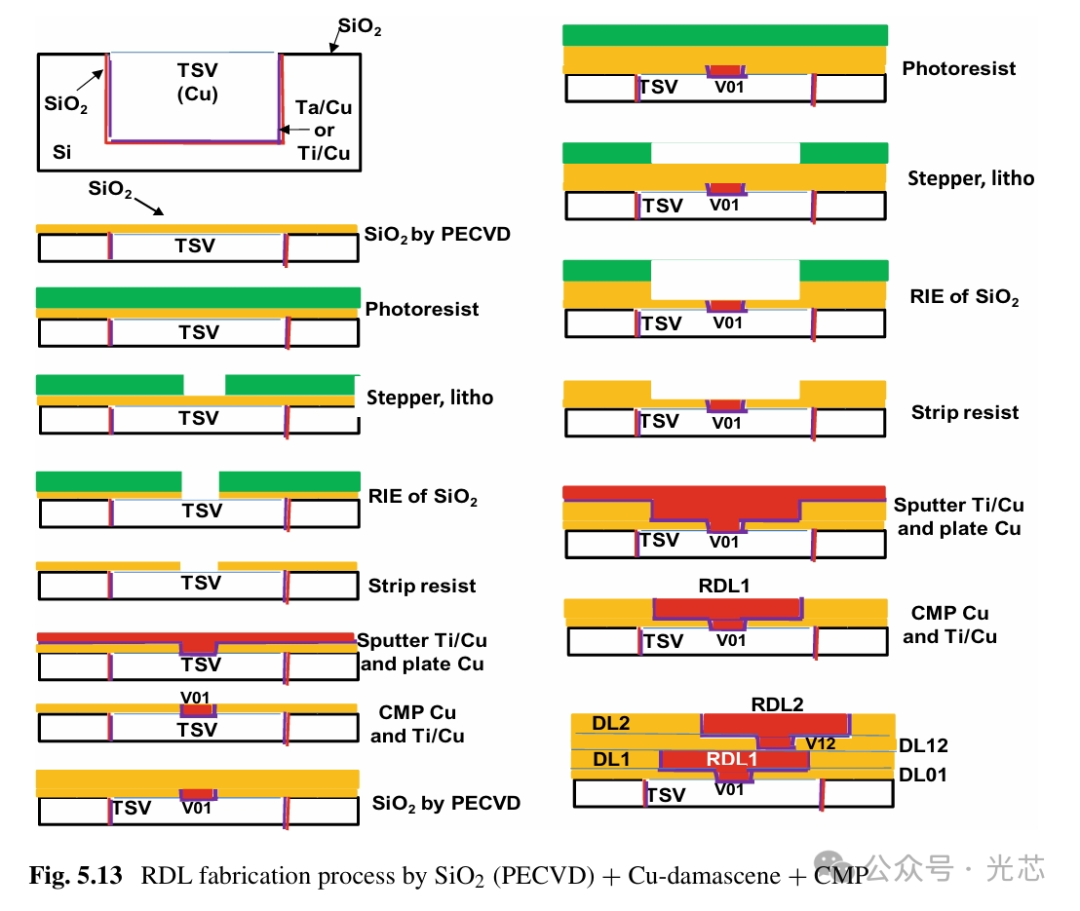

(B)制造RDL:SiO2 + Cu Damascene和CMP方法

另一种RDL制造方法是Cu damascene工艺。还是从图5.9和5.10中的晶圆开始,使用Cu damascene技术制造RDL的过程主要基于半导体后端线路过程。详细情况如图5.13所示。

1. 通过PECVD(等离子增强化学气相沉积)制作SiO2层。

2. 光刻,在SiO2上打开通孔。

3. RIE(反应离子蚀刻)SiO2。

4. 去除光刻胶。

5. 在整个晶圆上溅射Ti和Cu,并在晶圆上电化学沉积(ECD)Cu。

6. 通过CMP去除多余的Cu和Ti/Cu。V01(连接TSV到RDL1的通孔)完成。

7. 重复步骤1。

8. 应用光刻胶和掩模,然后使用光刻技术打开RDL位置。

9. 重复步骤3。

10. 重复步骤4。

11. 重复步骤5。通过CMP去除多余的Cu和Ti/Cu。RDL1完成。

12. 重复步骤1至步骤6以完成V12(连接RDL1到RDL2的通孔)。

13. 重复步骤7至步骤12以完成RDL2和任何额外层。

14. 重复步骤1用于UBM。

15. 光刻,在SiO2上打开所需焊盘的通孔,并覆盖RDL位置。

16. 在SiO2上蚀刻所需通孔。

17. 去除光刻胶。

18. 在整个晶圆上溅射Ti和Cu。

19. 光刻,暴露UBM区域。

20. 电镀Cu核心层。

21. 去除光刻胶。

22. 蚀刻Ti/Cu。

23. 无电镀Ni和浸金。UBM完成。

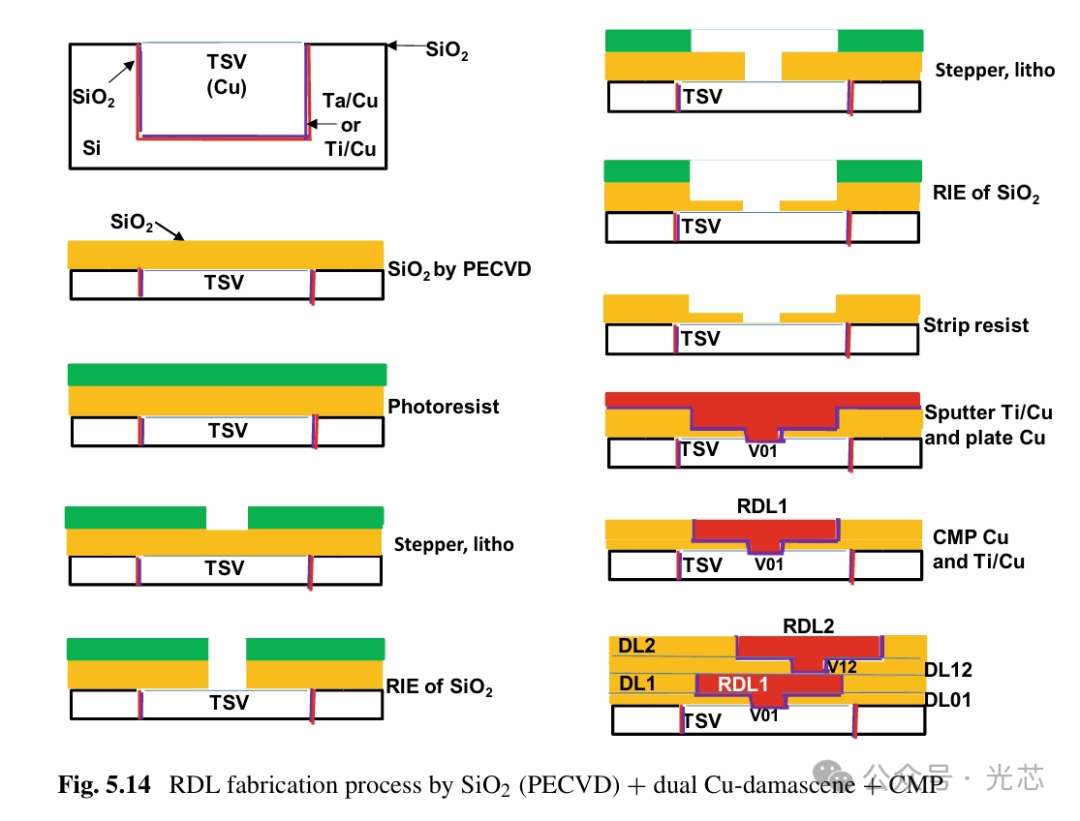

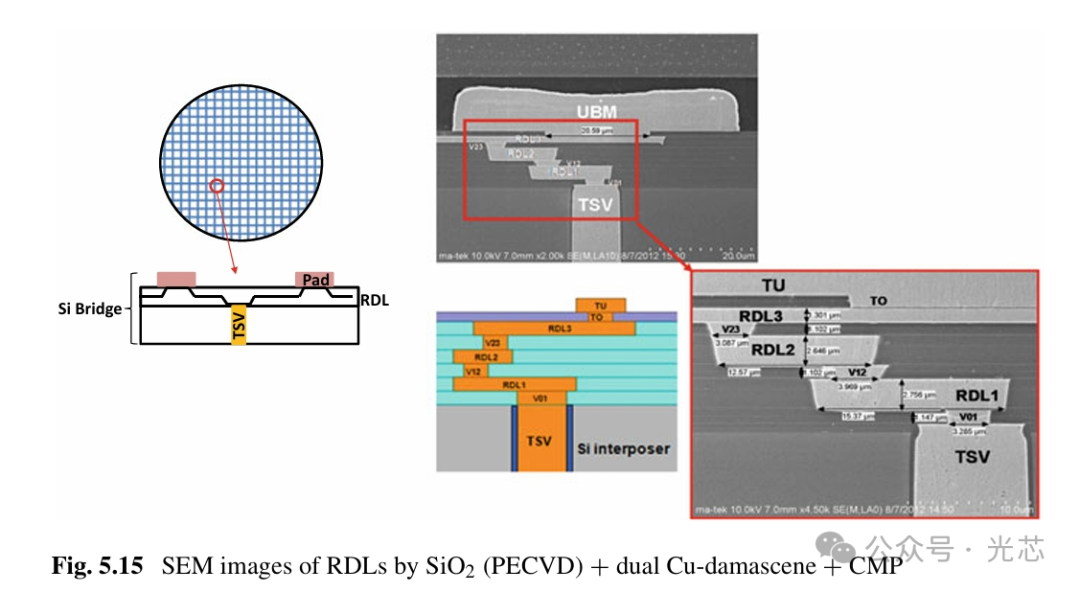

需要注意到,RDLs也可以通过双Cu damascene方法制造,如图5.14所示。使用Cu damascene技术制造的RDL横截面的SEM图像如图5.15所示。最小RDL线宽为3微米。RDL1和RDL2的厚度为2.6微米,RDL3为1.3微米。RDL之间的钝化厚度为1微米。

好了这里把技术细节介绍完了,下一篇基于介绍Intel、IBM、TSMC等大厂的chiplet方案。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2024-11-12,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读