七位半 100mV 档位,前端信号链噪声需要控制到多少?

DVM1107 还有很多可以挖掘的地方:

对七位半电压表内部两个滤波器级联建模(以 DM 7275 为例)

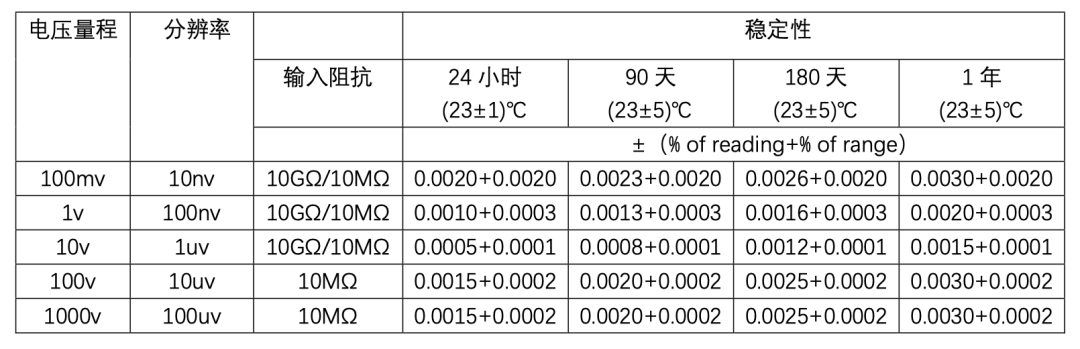

请看这个测试数据

请看这个测试数据

那问题来了,在 100 mV 量程下,前面整条采集信号链本身允许有多大噪声,才不会明显拉低这台表的测量效果?

那最直接的判断标准就是:

让前端链路的输入等效噪声,明显低于这台表在 100 mV 档自身的本底噪声。

而 DVM1107 规格书已经给了 100 mV 档的关键数字:分辨率10 nV,10 PLC、5 分钟标准方差0.6 ppm;另外峰值噪声0.7 μV p-p 。

先把 0.6 ppm 换算成电压

100 mV 量程下:

也就是说,这台表在这个档位、这个测试条件下,它自己的短时随机噪声量级大约就是:

而规格书同时给了峰值噪声:

这两个量级彼此是基本一致的,一个是统计标准差,一个是峰峰值。

所谓 “不影响采集效果”常用标准

如果前端信号链噪声和仪器本底噪声叠加,最终总噪声是平方和:

所以如果希望前端噪声几乎不拉高总噪声,通常有三档标准:

这一档很严格,几乎可忽略

让前端链路噪声只有仪器本底的 1/3 以下

这时总噪声变成:

只增加约 **5.4%**,基本可以认为“不影响”。

这一档比较合理,轻微影响

让前端链路噪声不超过仪器本底的 1/2

这时:

总噪声增加约 11.8%,已经能看见一点影响,但还不算严重。

勉强能接受

前端链路噪声和仪器本底差不多:

这时:

总噪声涨了 41%,这就明显影响采集效果了。

所以对 100 mV 档,如果希望前面采集链路基本不影响这台表的发挥,可以按下面这个目标看:

更宽松一点也最好别超过:

这里的“输入等效噪声”指的是:把整个前端放大器、分压、保护、走线、热电势波动、参考耦合等一切噪声,全部折算回 100 mV 输入端之后的总 rms 噪声。

用峰峰值表达,应该控制到什么水平?

我们知道仪器自身在 100 mV 档给的是 0.7 μV p-p,所以为了不明显劣化,一般前端链路的峰峰值噪声最好控制在它的 1/3 以下,也就是大约:

更宽松一点,上限大约:

如果链路自己就有 0.7 μV p-p,那整机峰峰值一定会明显变差;另外LHA5658-2 本身在低速高分辨模式下,ADC 芯片噪声其实并不差。比如在外部 5 V 参考、sinc5+sinc1、5 SPS 条件下,规格书给的是 0.07 μV rms,也就是 70 nV rms;更高一点 49.96 SPS 时是 0.18 μV rms。

但是这里还是要小心:这只是 ADC 输入端噪声,不一定等于 100 mV 量程的表输入端噪声,因为中间可能还有量程缩放+前端增益+缓冲+数字平均+校准补偿

所以从整机角度,DVM1107 自己给出的 100 mV 档噪声指标更可信,也就是刚才算出来的:

这两个数应该作为判断“前端是否会拖后腿”的基准。

但在 100 mV 档这种级别,真正讨厌的往往不是白噪声,而是这些:(我举例子)接插件热电势波动+铜-焊锡-镀层异种金属结点温差+漏电流乘以源阻抗+风吹导致的温差漂移(当然是壳子里面保护住了,可能少一些)

尤其 ADR1399 数据手册明确提醒,寄生热电势可以到 1 μV/°C 到 40 μV/°C 量级;对 100 mV 档来说,这非常可怕。因为:100 nV 已经是很小的变化了,一点点热梯度就能轻松产生数百 nV 到数 μV 的慢漂。

(在知道了这些以后),再问“采集信号链噪声允许多少”,严格说应该分成两类:

快噪声

目标控制在:

慢漂 / 热电势波动

最好控制到:

量级

否则虽然示波统计上 rms 不大,但读数会慢慢飘,采集效果同样会被破坏;如果有使用者准备给这台表前面加外部采集前端,或者在设计一个 100 mV 级精密测量链路,建议直接按我算出来这个目标做:

输入等效快噪声:

尽量不超过:

峰峰值噪声:

热漂 / 热电势波动:尽量压到 100 nV 量级以内

假如超过这些到 60 nV rms会有开始明显拉高总噪声,到 0.7 μV p-p基本已经和仪器本底同量级,会明显变差。

说回对 DVM1107 的 100 mV 档 ,前面采集信号链若想“基本不影响效果”,应把输入等效噪声控制在:

最好不要超过:

而且还要特别防热电势和慢漂,不然电子噪声合格,采集效果也一样会被破坏。

每一级可以分配多少噪声?

以上都是折合的总噪声,但是一个信号链是需要很多级的,也就是说噪声贡献还得分配下去,那接下来要回答:

前端采集链上的每一项噪声,分别最多能给多少?

前面已经从 DVM1107 的 100 mV 档规格得到:10 PLC、5 分钟标准方差0.6 ppm;100 mV 档对应约 60 nV rms,峰值噪声约 0.7 μV p-p;所以如果前端链路“不明显影响采集效果”,一个合理目标是:

更宽松一点:

下面按 20 nV rms 目标来做预算,因为这比较像“高质量前端不拖后腿”的设计标准;把前端链路等效到输入端,记总噪声为:

:源阻抗热噪声

:放大器电压噪声

:放大器电流噪声流过源阻抗产生的噪声

:前端电阻网络自身热噪声

:低频闪烁噪声

:热电势波动

:工频、电磁耦合、地回路残余,对 100 mV 档这种微小信号,真正最难的是后三项,不只是前两项。

带宽

噪声一定要和带宽一起说,DVM1107 本身是慢速精密读数,1–100 PLC 可调;LHA5658-2 也是 ΣΔ ADC,低速下噪声显著下降,并且有 sinc 滤波和工频抑制;所以如果我们讨论的是 100 mV 档精密 DC 采样,前端应该是一个很窄带的低频系统。工程上可先假设前端等效噪声带宽:

这已经算偏宽松了,如果系统最后实际有效带宽只有 1 Hz 或更低,噪声还会再降。

源阻抗热噪声

热噪声公式:

:源阻抗

:等效噪声带宽

在 300 K 下可简化为常用工程形式:

积分到带宽 后:

举几个数

当 ,

当

当

当

这已经超预算了。

如果想在 100 mV 档做到前端噪声不明显影响整机,那么源阻抗最好别太高,最好在几十欧到几百欧量级,一旦源阻抗到 kΩ 甚至更高,单是热噪声就已经逼近甚至超过目标。

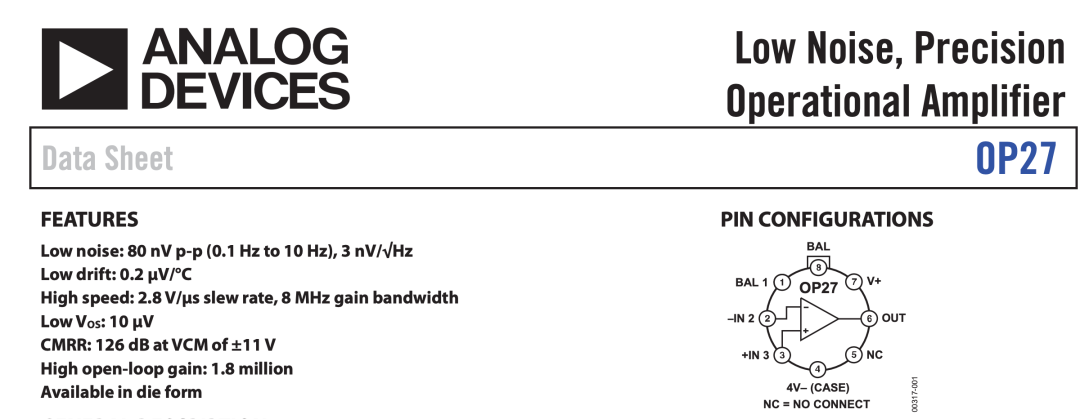

放大器电压噪声

如果前端有缓冲器或仪表放大器,输入电压噪声密度记为 ,则带宽内 rms 为:

这里 单位是 nV/。

若 ,

若

若

这时候已经几乎吃掉全部预算了,如果前端真的要给 100 mV 档做高质量缓冲,建议:

更理想:

否则光白噪声就太大。

放大器电流噪声

如果运放输入电流噪声密度是 ,流过源阻抗 后形成等效电压噪声:

积分后:

假设:

那么:

如果 ,就变成:

直接爆掉;还是之前的结论对低阻源,电流噪声往往不大;对高阻源,它马上变成主导项,所以:

100 mV 档高精度测量,前端不能只看电压噪声,也必须看电流噪声和源阻抗匹配。

很多人只看运放,却忘了保护电阻、限流电阻、RC 滤波电阻自己也会发噪声;如果前端串了一个 ,它自己的热噪声也是:

比如:100 Ω 串联电阻,10 Hz 带宽

1 kΩ 串联电阻

所以在 100 mV 档前端里:保护和滤波电阻不能乱加大;否则为了“读数更稳”,实际是在主动加噪声。

1/f 噪声和低频漂移

这是 100 mV 档最麻烦的一项;因为测的不是宽带交流,而是低频 / 近直流;这时运放的数据表里“1 kHz 噪声密度很好看”并没有完全说明问题,更关键的是0.1–10 Hz 噪声(零点漂移)

如果某运放规格写:

这个其实就已经很不错了。

如果是:

那在 100 mV 档精密测量里就很可疑了;对这类前端,可以把 0.1–10 Hz 输入噪声控制在:

再高的话,即使宽带白噪声不大,读数也会慢慢晃。

热电势波动

这项必须单独拎出来,因为它经常不是“随机白噪声”,而是慢漂;ADR1399 数据手册明确提醒,异种金属结点的热电势可能在:

到

这个量级,在 100 mV 档,如果希望它不影响效果,我们最好让热梯度引起的瞬时波动控制到:

或者慢漂峰峰值不超过:

这意味着什么?

假设某结点热电势系数是 ,那么要把热致误差压到 100 nV,允许温差变化只有:

这就是为什么这种系统里材质,接线,避风,预热这些重要。

另外因为整机本身有积分 / ΣΔ 滤波,后端会帮前面压一部分 50/60 Hz。而且DVM1107 支持 PLC,LHA5658-2 也有强工频抑制模式;但前端如果已经拾取了很大的工频共模 / 差模,再进 ADC 之前就可能产生:缓冲器非线性整流,共模转差模,保护网络调制;所以对前端来说,比较务实的目标是:

换句话说,前端不能把外界弄成“先污染,再靠数字滤波补救”。

(统计一下),目标是前端总输入等效噪声不超过 20 nV rms。

项目 | 目标值 |

|---|---|

源阻抗热噪声 | 5 nV rms |

放大器白噪声 | 6 nV rms |

电流噪声项 | 3 nV rms |

RC/保护电阻热噪声 | 4 nV rms |

热电势波动 | 8 nV rms |

工频/EMI残余 | 5 nV rms |

平方和:

这个就很理想,明显低于 20 nV 目标,然后给一个宽松的预算:

项目 | 值 |

|---|---|

源阻抗热噪声 | 8 nV |

放大器白噪声 | 10 nV |

电流噪声项 | 5 nV |

RC 电阻热噪声 | 8 nV |

热电势波动 | 12 nV |

工频残余 | 8 nV |

则:

这个已经接近前面说的“理想上限”,还能用,但开始会看见对整机表现有一点拖累。

反推元件指标

假设你目标仍然是 10 Hz 带宽下 ,则放大器白噪声密度需满足:

这就是为什么常用的低噪声精密运放,很多都落在:0.8 nV/√Hz,1.0 nV/√Hz,1.2 nV/√Hz,2 nV/√Hz这个档位。

同理,如果希望电流噪声项 < 3 nV rms,而源阻抗 ,则

所以一旦源阻抗到 kΩ 量级,输入电流噪声也必须进 pA/√Hz 甚至以下。

当然对任何一个前端,都可以用这三步快速判断:

第一步:先算源阻抗热噪声

第二步:再算运放白噪声

第三步:再看 0.1–10 Hz 噪声和热电势,如果这两项压不住,前两项算得再漂亮也没用;对 100 mV 档,如果想让前面采集链路基本不影响 DVM1107 的表现,建议按下面这个标准设计:

输入等效噪声目标

更理想目标

源阻抗热噪声:

运放白噪声:

电流噪声项:

保护/滤波电阻热噪声:

热电势波动:

工频/EMI残余:

后记

精密信号链的设计,第一奥义就是要知道系统底线在哪里;知道了底线,才能选拓扑,以至于在后续的各个环节中进行取舍;如果在这么多级中胡乱的使用元器件,无疑是和微弱信号无缘的;即使侥幸得到了信号,也可能是无关的噪声而已。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-04-24,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录