没有它就没有成功流片!硬件辅助验证40年进化史

没有它就没有成功流片!硬件辅助验证40年进化史

FPGA技术江湖

发布于 2026-03-23 21:23:21

发布于 2026-03-23 21:23:21

十多年来,硬件辅助验证(HAV)平台一直是验证工具链的核心。如今,任何正规的半导体项目在流片前,都离不开仿真或FPGA原型验证的核心支撑。HAV已深度嵌入开发流程,以至于人们很容易认为它本就如此。

但事实并非如此。

即便起点略有争议,今年大致也可算作硬件辅助验证诞生40周年,广义上包括硬件仿真与FPGA原型验证。四十年间,HAV从小众技术,演变为现代芯片开发不可或缺的支柱。它的历史,在很多方面也是半导体行业自身的缩影:随着芯片复杂度提升、软件主导、AI重塑一切,HAV不断重新定义自身价值。

在HAV成为公认品类之前,早已出现先驱技术。例如IBM通过约克镇仿真引擎、后续的工程验证引擎等系统尝试硬件加速。这些机器本质上是仿真加速器——专为加速运行硬件模型而设计的专用计算机,性能远超传统软件仿真器。它们是重要的进步,但仍从属于仿真范式:速度虽有提升,却远不足以让被测设计跑真实场景。

HAV平台属于另一类引擎。早期仿真器基于可重构硬件(通常是FPGA阵列),配置后可模拟被测设计(DUT)行为。工程师首次能在流片前以接近真实运行速度与芯片模型交互。PiE Design Systems、Quickturn、IKOS、Zycad等公司开创了这一全新验证方式,为日后半导体开发的核心支柱奠定基础。

HAV的演进大致可分为三个时代:

•早期:硬件复杂度催生仿真

•中期:软件主导,HAV走向虚拟化

•成熟期:AI workload将硬件重新推到架构创新中心

早期时代:硬件复杂度倒逼仿真崛起

20世纪80年代初,半导体设计几乎完全由硬件定义,嵌入式软件即便存在也作用微小。行业由处理器与图形芯片先驱推动,冲向当时看似惊人的里程碑:100万门。验证高度依赖门级仿真,这是当时的通用标准。

但随着设计规模扩大,仿真器撞上无法回避的性能墙:主机内存受限、设计频繁换入换出磁盘、仿真时间暴涨、测试向量爆炸式增长,达到合理故障覆盖率的计算负载已无法管理。流片前的全系统验证变得越来越不现实,甚至完全不可能。行业需要更快、更贴近真实芯片的方案。

硬件辅助验证正是为应对这一危机而生。

早期HAV平台主要以在线仿真(ICE) 模式部署:仿真器通过物理线缆接入真实目标系统,工程师可在真实环境与外设中测试被测设计。这是革命性突破:不再依赖人工构造向量,而是用真实负载验证芯片,实现仿真无法比拟的真实度。验证第一次贴近芯片实际工作场景。

前景虽广阔,现实却很痛苦:早期仿真器配置复杂、运行不稳定、故障率高。漫长配置常导致验证延期,线缆与硬件可靠性问题引发频繁宕机,平均无故障时间(MTBF)以小时计,验证团队反而要花大量时间调试仿真器本身。即便如此,趋势已清晰:验证再也无法纯靠软件。

中期时代:软件吞噬世界,HAV成为验证支柱

随后几十年,设计格局彻底改变:功能持续从硬件迁移到软件代码。正如马克·安德森2011年的名言:“软件正在吞噬世界”。这一预言在几乎所有计算相关行业精准应验。SoC变成软件定义平台,智能越来越多地驻留在固件、操作系统、驱动与应用栈中。硬件不再是产品全部,而是软件的载体。

这一转型彻底改变验证。静态测试向量已无法覆盖现代设计的全部复杂度,工程师转向软件驱动激励,用高级测试平台验证全功能域,硬件验证语言与更抽象的方法学随之出现。

曾主要用于实时ICE验证的HAV引擎,转型为以软件为中心环境的执行引擎。行业通过基于事务的验证(IEEE SCE‑MI标准)规范软件测试平台与硬件映射DUT之间的交互。工程师不再逐周期翻转信号,而是通过高级事务与DUT交互,性能与效率大幅提升。

这一转变也消除了早期诸多实际限制:虚拟化环境减少对物理连接的依赖,不再需要ICE所需的速度适配器;验证IP替代硬件接口,形成可扩展、全数字化的验证生态。

随着行业拥抱左移(shift‑left),HAV成为最强力使能器:让工程师在设计流程更早阶段启动软件,从裸机初始化到驱动、操作系统全覆盖。验证不再局限于孤立功能正确性,而是覆盖完整软硬件系统行为,远早于芯片流片。

至此,HAV早已不只是“让验证更快”,而是硬件与软件开发的桥梁,支持团队并行而非串行开发,成为现代系统验证的支柱。

AI时代:AI重塑硬件核心地位,HAV走向全栈

2010年代中期至今,行业进入由人工智能爆发驱动的新时代。叙事从“软件吞噬世界”升级为更激进的趋势:软件定义硬件。

AI时代,软件不再只是运行在硬件上,而是越来越多地定义硬件必须成为什么样子。现代AI模型需求极端,从底层重塑处理器架构。

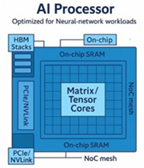

生成式AI暴露了传统通用架构的极限:海量数据搬运与计算强度压垮CPU,即便高度优化系统也不堪重负。行业转向专用架构:GPU、FPGA、专为大规模并行与张量计算设计的AI加速器。

这些发展让SoC设计规模与复杂度急剧提升。AI时代芯片动辄包含数十亿门、异构计算集群、复杂片上网络(NOC)以高效搬运数据。

在此背景下,HAV承担了根本性扩展的角色。

验证不再局限于数十亿门以下设计的功能正确性,而是要扩展到数十亿门级系统,覆盖远不止逻辑、甚至不止软件栈的内容。今天的HAV平台越来越多地用于:

•评估功耗与热行为

•分析性能

•验证安全与安保需求

•捕获全系统级交互

•运行反映真实世界的实际负载

同时,ICE模式从传统方式成熟为关键工程能力,尤其在全速FPGA原型验证中:流片前必须用真实物理接口全速验证。通过让被测设计尽早与真实PHY硬件交互,ICE能发现纯虚拟环境无法暴露的集成、时序、信号完整性问题,在流片前大幅提升软硬件信心。

图1:AI处理器框图

同样重要的是:AI硬件无法脱离软件生态。编译器、运行时、库、内核、部署框架不再是事后考虑,而是决定硬件成败的核心要素。因此HAV平台在流片前就运行真实AI负载,确保软硬件协同演进,而非串行开发。架构与执行的反馈环在流片前就已闭合,而非等到首版芯片。

从这个意义上说,AI时代的验证已真正走向全栈。

HAV不再只是验证工具,而是软硬件协同设计收敛的环境,催生全新范式:软件驱动流片(software‑driven tape‑out)。

结论:HAV——软硬件融合的引擎

历经四十年演进,半导体行业完成了一次完整轮回:

•硬件复杂度最初催生仿真

•随后软件时代扩展HAV,连接虚拟化、更丰富软件栈与系统级流程

•今天AI革命再次重塑格局,让硬件重回创新中心,并要求前所未有的专业化、效率与规模

但最根本的变化,是“核心”的含义。

硬件不再是先设计后编程。这十年的决定性趋势是软件定义设计:架构不仅由晶体管、互联、逻辑结构决定,同样由编译器、运行时、负载决定。软硬件边界模糊,成为高度耦合的单一工程问题。

HAV平台正位于这一交汇点。

它不再被视为孤立检查正确性的工具,而是验证架构意图的核心环境:硬件与真实软件交汇、性能假设在真实负载下被检验、系统级权衡在设计仍可修改时暴露。在软件驱动流片时代,HAV是在芯片诞生前就闭合闭环的机制。

硬件再次成为世界中心,不是因为软件不再重要,而是因为软件太重要,以至于它定义了硬件本身。

成功标准也随之改变:

选择HAV平台,不再只看能验证多少门的功能正确性,而是看能否在流片前执行、分析、优化全场景软件驱动用例。

在这个新时代,硬件不仅是软件创新的底座,更成为其核心引擎之一。

END

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-03-06,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读