SK海力士展示16层堆叠HBM4

SK海力士展示16层堆叠HBM4

芯智讯

发布于 2026-03-19 12:04:49

发布于 2026-03-19 12:04:49

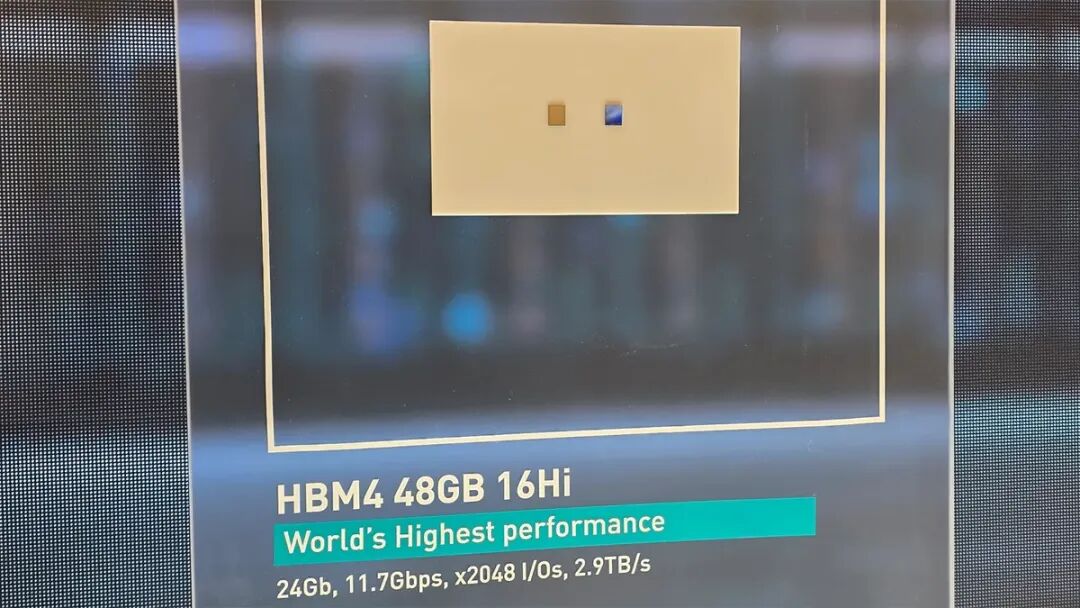

1月14日消息,据外媒Tom's hardware报道,韩国存储芯片大厂SK海力士日前在CES 2026展会上首度公开展示了业界首款16层HBM4 封装。

SK海力士指出,此次展示的16层HBM4 内存堆叠采用2048-bit 接口,相较前一代HBM3E,大幅提升I/O 密度与整体带宽配置。SK海力士透露,其HBM4 內存堆叠运行速度可达10GT/s,比JEDEC 官方规范高出约25%。

报导指出,包括英伟达在内的潜在采用者,对HBM4 不仅着眼于性能提升,也看重其在大规模AI 系统与超大规模数据中心应用中的性能与能源效率弹性。在高功耗、长时间运作的AI 训练与推理环境中,内存的带宽、功耗与可靠度已成为系统设计的关键因素。

从封装规格来看,HBM3/HBM3E 与HBM4 采用相同约10.5×12.0mm 的封装尺寸,但HBM4 允许更高的堆叠高度。以16层HBM4 为例,堆叠高度约950微米,明显高于12-Hi HBM3 的约750微米,同时在相同面积内整合更多I/O 与电源凸块,进一步推升封装复杂度。

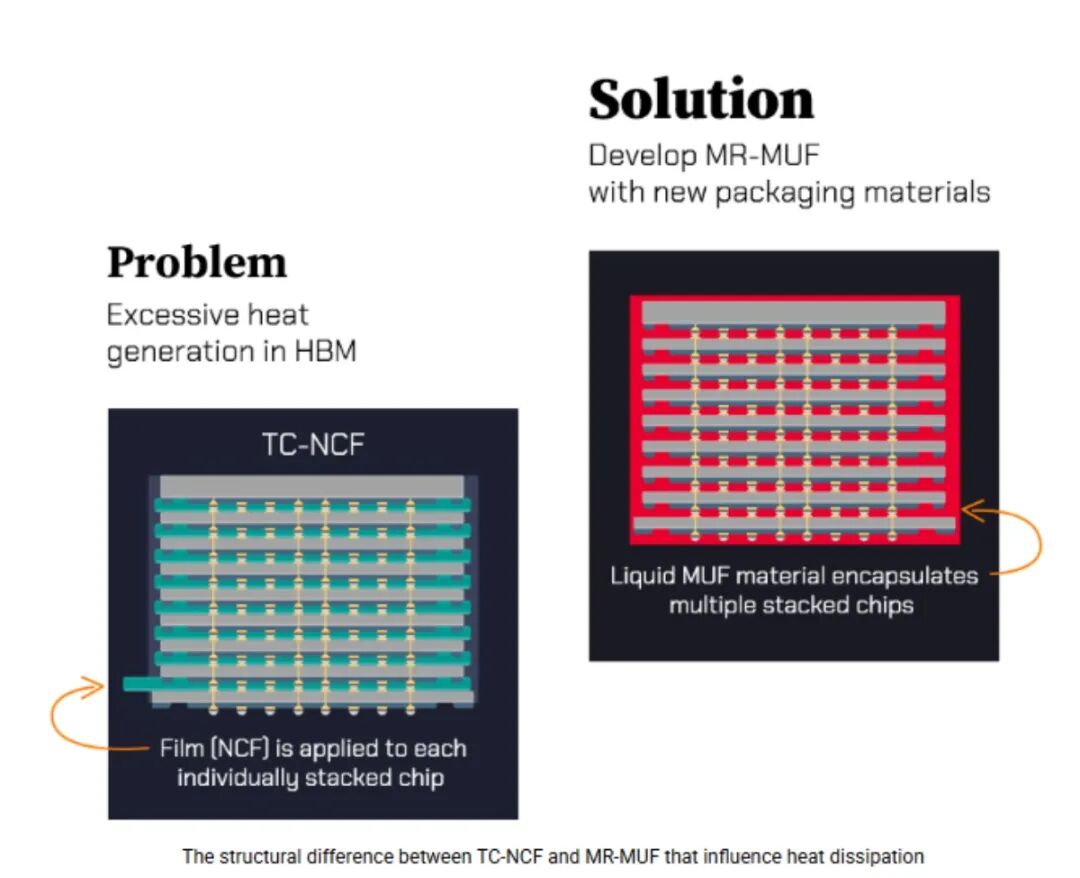

为支撑如此高密度与高堆叠设计,SK 海力士持续采用其关键封装技术MR-MUF(Mass Reflow Molded Underfill)。

根据SK海力士网站资料显示,MR-MUF 结合回焊(reflow)与模封(molding)制程,在一次回焊完成多层芯片堆叠接合后,以液态环氧模封材料(EMC)填充芯片间与微凸块间隙。

这种做法不仅能强化结构稳定性,也有助于提升散热表现、降低封装缺陷风险,并改善整体制造良率。

编辑:芯智讯-林子

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-01-16,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读