ISSCC 2026 Forum:数据中心400G、800G至太比特级可插拔光模块的技术演进、挑战与产业路线(Arista)

ISSCC 2026 Forum:数据中心400G、800G至太比特级可插拔光模块的技术演进、挑战与产业路线(Arista)

光芯

发布于 2026-03-02 21:56:55

发布于 2026-03-02 21:56:55

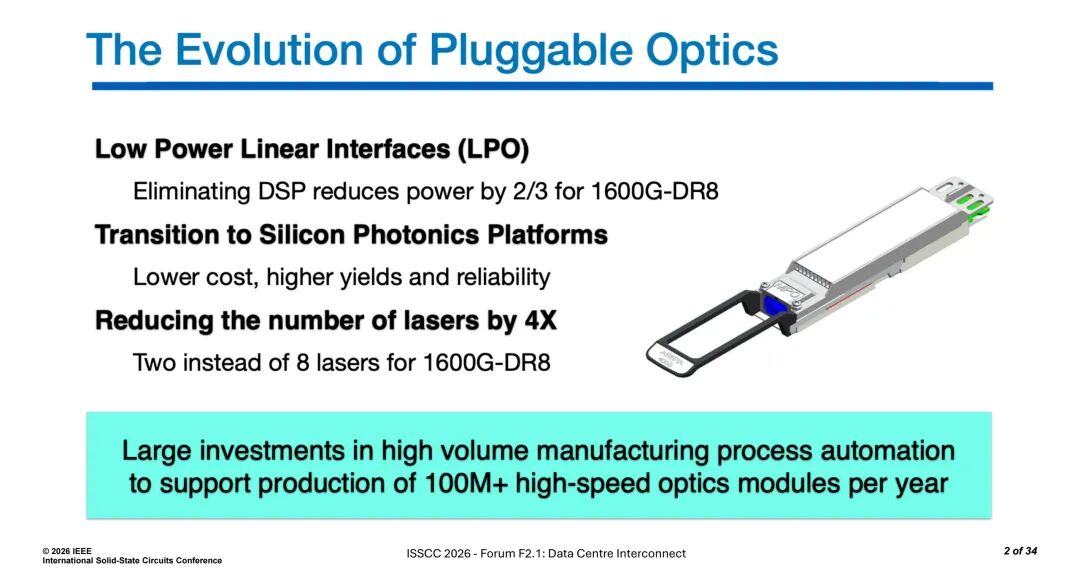

一、可插拔光模块的核心演进方向

当前数据中心可插拔光模块的技术演进,始终围绕功耗优化、光子学平台升级与规模化量产能力建设三大核心方向推进,三大方向共同支撑了从800G到太比特级光模块的代际跃迁。在功耗优化层面,低功耗线性接口(LPO)成为行业核心攻坚的技术路径,其核心价值在于通过移除链路中的DSP芯片,大幅削减模块整体功耗,针对1600G-DR8光模块的实测数据显示,该方案可实现高达2/3的功耗降低,完美匹配超大规模数据中心对高速互连的功耗管控需求。

在光子学平台升级层面,行业正全面向硅光子学平台转型,该平台不仅能够实现更低的器件成本、更高的量产良率与长期运行可靠性,还能实现激光器数量的4倍缩减,最具代表性的案例便是1600G-DR8模块,基于硅光子学平台的方案仅需2颗激光器,即可完成传统方案8颗激光器才能实现的传输性能,从器件层面实现了成本与复杂度的双重优化。在规模化量产能力建设层面,为了支撑未来每年超1亿只高速光模块的市场供应需求,全球产业链正在对高量产制造自动化产线进行大规模投入,为下一代光模块的规模商用筑牢产能基础。

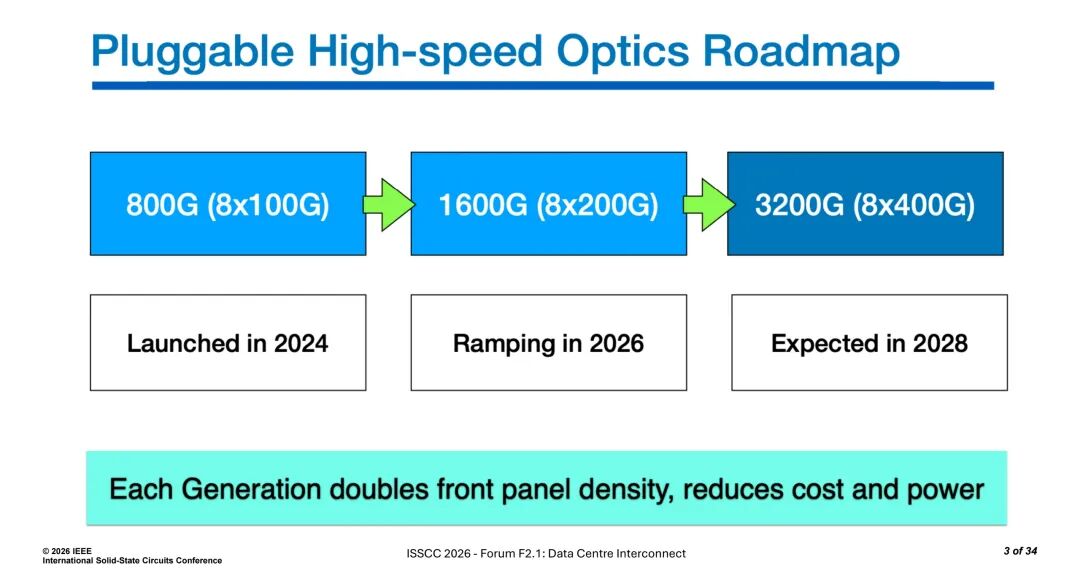

二、高速光模块代际路线图与单波400G技术跃迁

可插拔高速光模块的代际演进,始终遵循“单通道速率翻倍、前面板端口密度同步翻倍、同步实现单位比特成本与功耗下降”的核心规律,目前行业已经形成了清晰、可落地的产业路线图。其中,800G(8x100G)光模块已于2024年正式完成商用发布,1600G(8x200G)光模块于2026年进入大规模量产爬坡阶段,而作为下一代核心产品的3200G(8x400G)光模块,预计将于2028年正式推出市场。

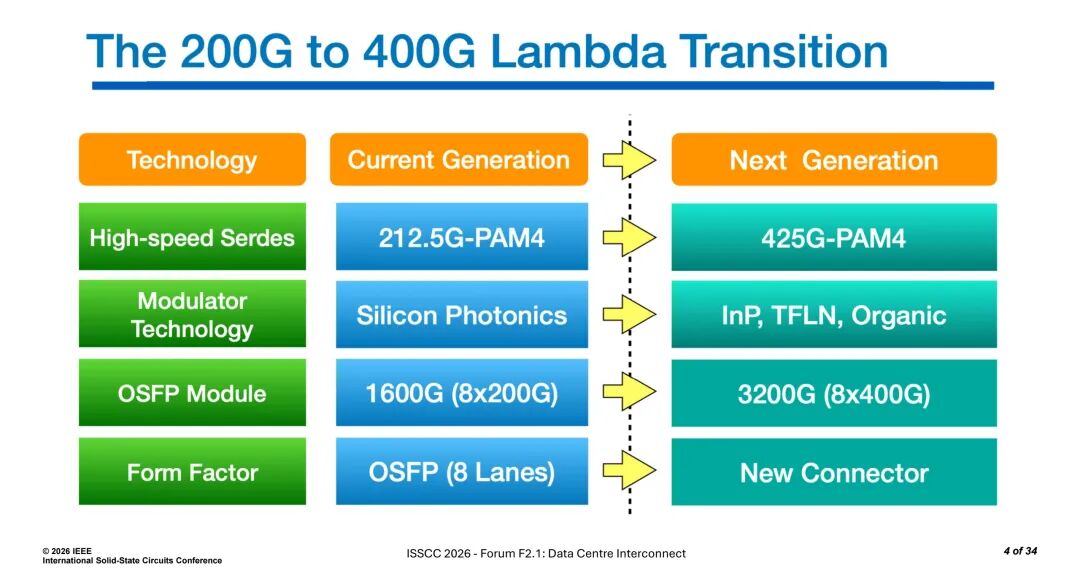

从单波200G向单波400G的技术跃迁,是实现3200G光模块商用落地的核心基础,两代技术在核心架构与关键器件上存在明确的代际差异。当前主流的1600G方案,采用212.5G-PAM4高速Serdes、硅光子学调制技术,搭配8通道OSFP模块封装形态;而下一代3200G方案,将全面升级为425G-PAM4高速Serdes,调制技术也将从传统硅光转向InP、TFLN、有机材料等更高带宽的平台,同时配套全新设计的高带宽电连接器。

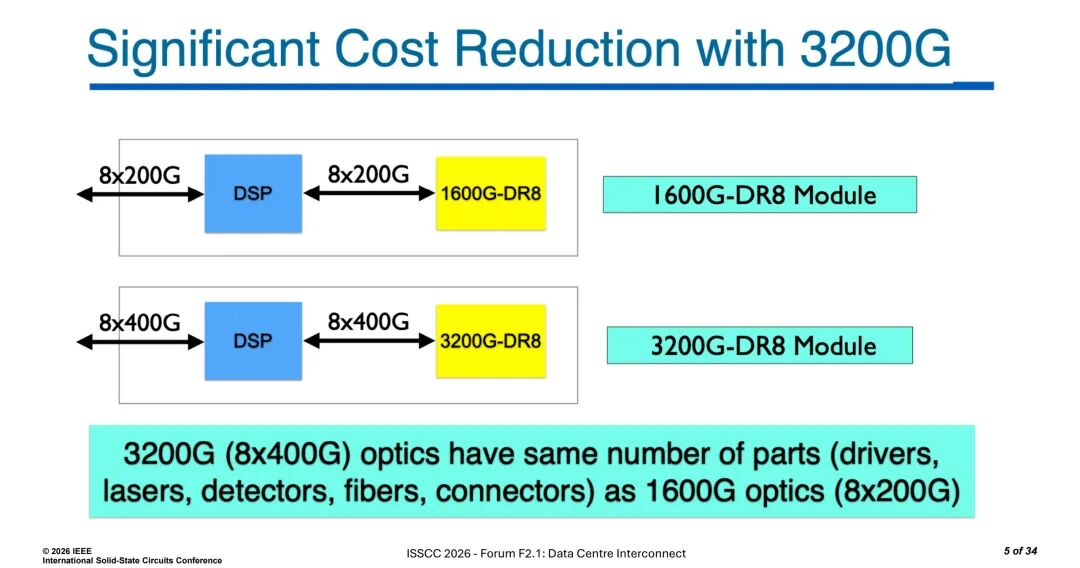

3200G(8x400G)光模块与1600G(8x200G)模块拥有完全相同数量的核心元器件,包括驱动器、激光器、探测器、光纤与连接器,这意味着在单通道速率翻倍、端口容量翻倍的前提下,不会带来元器件数量的增长,为下一代模块的成本优化提供了核心支撑,也让3200G模块具备了快速规模商用的基础。

三、400G IM/DD技术平台对比与功耗特性

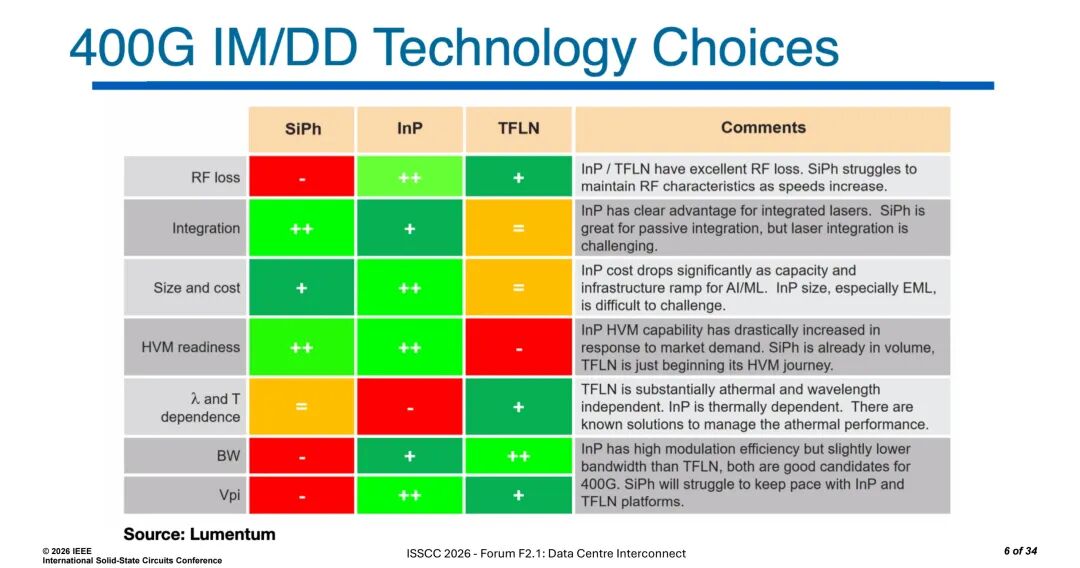

400G IM/DD场景的核心技术竞争,主要围绕硅光(SiPh)、磷化铟(InP)、薄膜铌酸锂(TFLN)三大技术平台展开,三类平台在核心性能维度存在显著差异,也对应了不同的商用场景与演进节奏。在射频损耗特性上,InP与TFLN具备优异的射频损耗表现,而硅光方案在单通道速率持续提升的过程中,难以维持稳定的射频特性,成为其向400G演进的核心瓶颈。在集成能力上,InP在激光器集成方面具备明确的先天优势;硅光在无源集成领域表现优异,但有源激光器的集成始终面临较大的技术挑战;TFLN的集成能力则与硅光处于同一水平。

在尺寸与成本上,随着AI/ML场景带来的市场需求爆发,InP的产能与配套基础设施快速爬坡,其成本出现显著下降,尤其是InP EML方案的尺寸优势,短期内难以被其他技术方案超越。在高量产(HVM)就绪度上,为响应快速增长的市场需求,InP的量产能力已实现大幅提升;硅光方案早已进入规模化量产阶段,产业链成熟度最高;而TFLN的高量产产业化进程才刚刚起步,仍需时间完成产能与良率的爬坡。在波长与温度依赖性上,TFLN具备显著的无热化特性,且性能与波长无关;InP则具有较强的热依赖性,不过目前行业已有成熟的方案来管理其无热化性能,满足商用场景的温度稳定性要求。在带宽特性上,InP具备高调制效率,带宽略低于TFLN,二者均是400G场景的优质候选方案;而硅光在带宽性能上,已难以跟上InP与TFLN平台的发展节奏,在单波400G场景下面临带宽不足的问题。

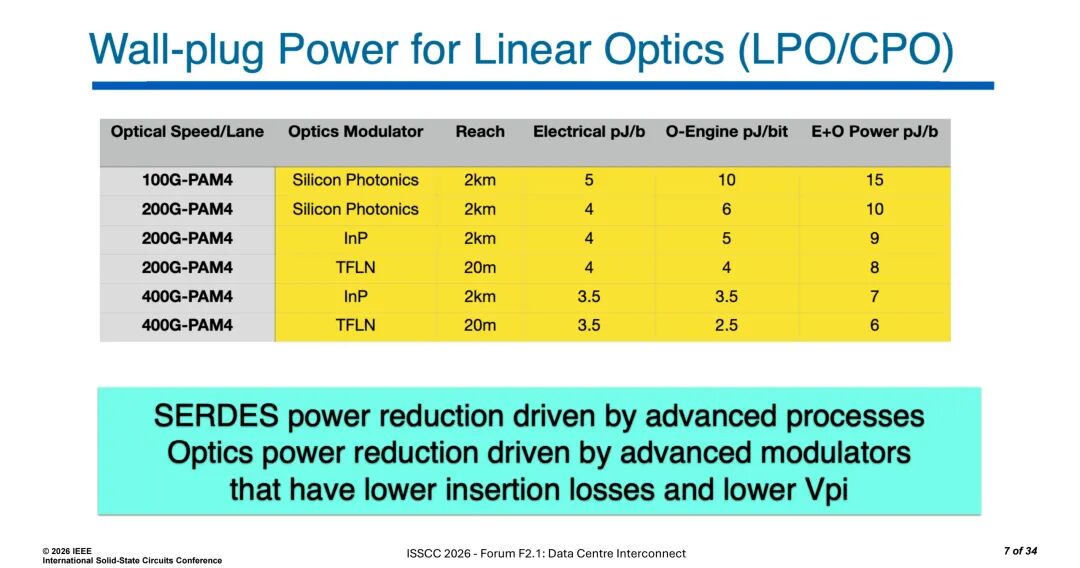

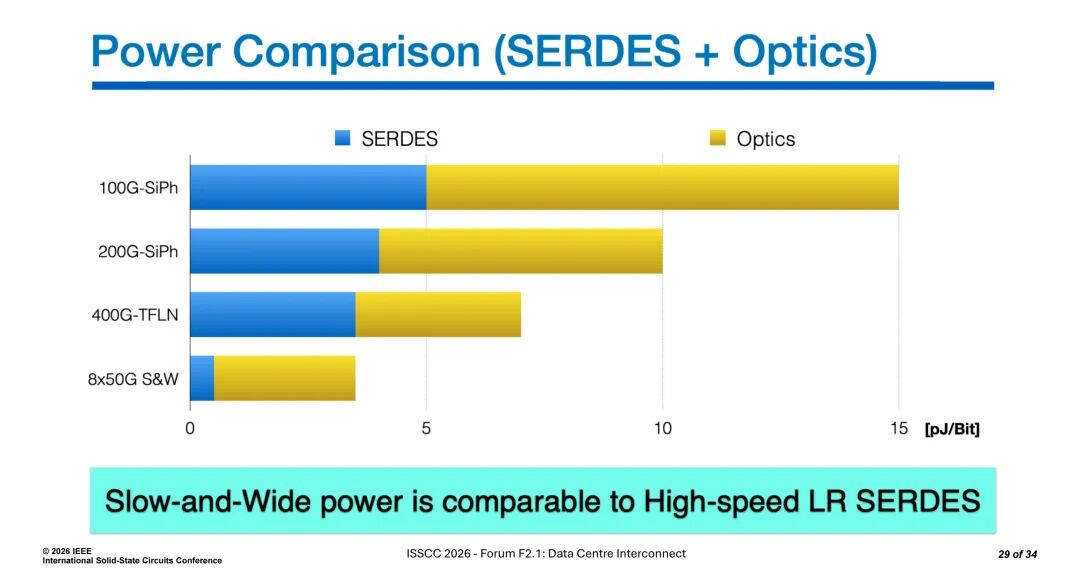

线性直驱光学(LPO/CPO)的墙插功耗实测数据,进一步验证了不同技术平台的功耗差异,以及单通道速率提升带来的功耗优化红利。具体来看,100G-PAM4速率下,采用硅光调制器、支持2km传输距离的方案,电气功耗为5pJ/b,光引擎功耗为10pJ/b,总功耗达到15pJ/b;进入200G-PAM4速率后,同传输距离的硅光方案,电气功耗降至4pJ/b,光引擎功耗降至6pJ/b,总功耗降至10pJ/b,同速率下采用InP调制器、2km传输的方案总功耗进一步降至9pJ/b,采用TFLN调制器、20m传输(?)的方案总功耗仅为8pJ/b;而到了400G-PAM4速率,采用InP调制器、2km传输的方案总功耗可降至7pJ/b,采用TFLN调制器、20m传输(?)的方案总功耗仅为6pJ/b,实现了单比特功耗的大幅下降。

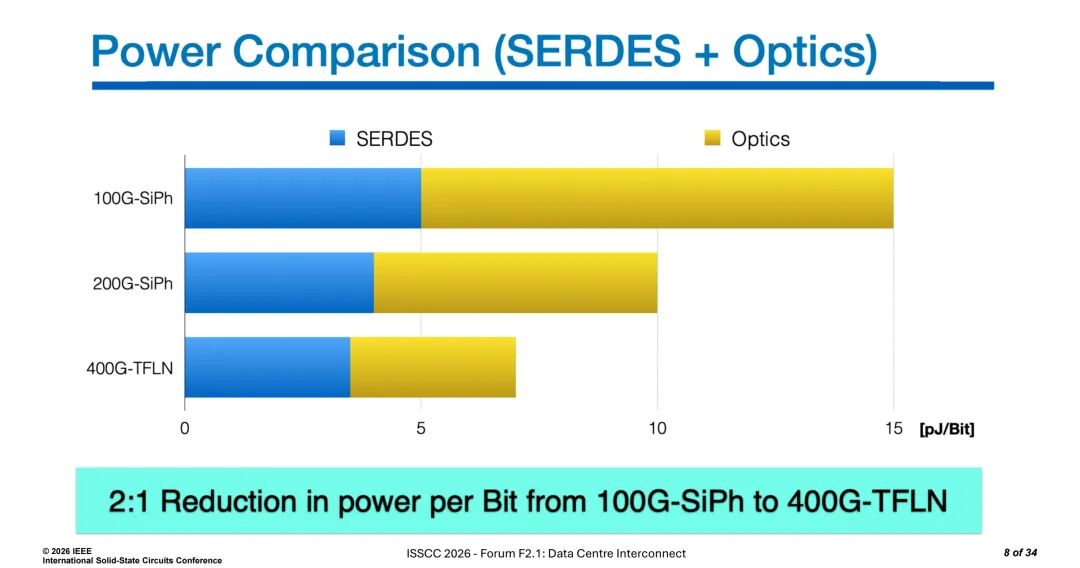

整体来看,SERDES功耗的降低,主要由先进半导体制程节点驱动,其中100G场景采用5nm工艺,200G场景采用3nm工艺,400G场景则升级至2nm工艺;而光模块功耗的降低,则由低插入损耗、低Vpi驱动电压的先进调制器技术驱动。从100G硅光方案到400G TFLN方案,单比特功耗实现了2:1的大幅缩减,同时,在425G-PAM4场景下,所有光方案均需要通过2.5D/3D堆叠的先进封装技术,实现电芯片(EIC)与光学芯片的高密度集成,以最大限度降低寄生参数,满足高带宽信号的传输要求。

四、400G/通道调制技术的可行性论证 400G-PAM4是光模块IM/DD调制场景下唯一可行的技术选择,这一结论得到了带宽性能、OSNR表现与产业链成熟度的多重支撑。光模块需要PAM4调制来获得良好的光信噪比(OSNR)性能,425G/通道的PAM4调制,对应需要106GHz的通道带宽,目前新型光调制器技术已可实现100+GHz的调制带宽,完全满足400G-PAM4的带宽需求,而传统硅光方案已出现带宽不足的问题,无法支撑该速率的商用落地。

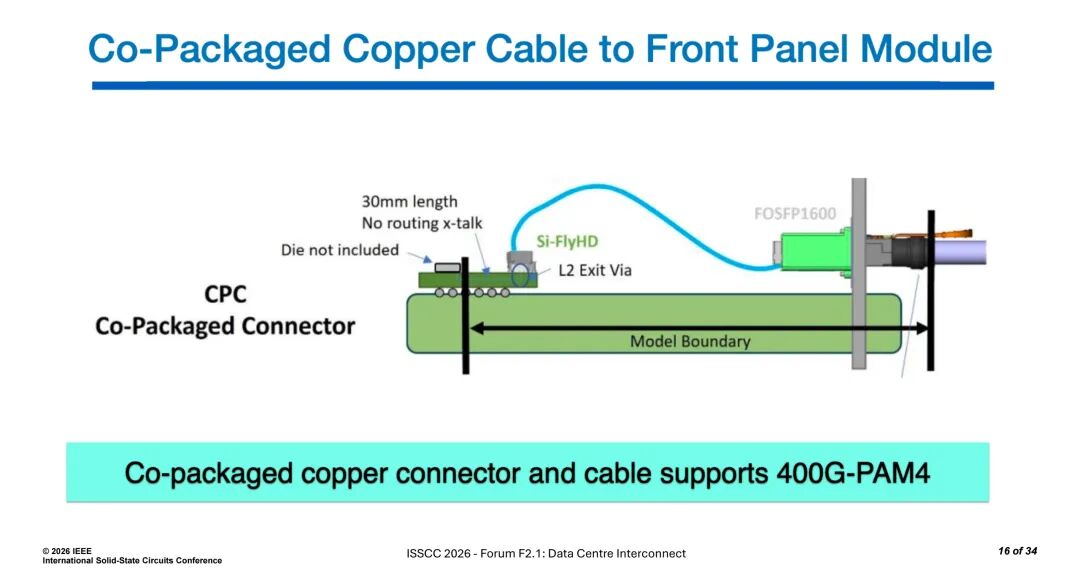

同时,全新高带宽CPC连接器的配套应用,能够实现干净、低损耗的高带宽通道,进一步为400G-PAM4的规模化商用提供了系统级支撑。

针对行业内关注的400G-PAM6方案,报告明确给出了结论:该方案仅适配铜缆传输场景,不适用于光模块传输场景。400G-PAM6的奈奎斯特带宽为85GHz,显著低于PAM4的106.25GHz,插入损耗更低,更适配铜缆的传输特性,但对于光模块场景,PAM6存在无法忽视的显著缺陷:一方面,PAM6会带来最高4dB的OSNR代价,需要额外的FEC开销来保障传输可靠性;另一方面,PAM6-PAM4转换所需的gearbox DSP功耗极高,8通道下的功耗超过25W,对应单比特额外增加8pJ/b的功耗,仅能通过gearbox转换为PAM4后才能适配光模块传输,整体性价比与功耗表现远不及直接采用400G-PAM4方案。

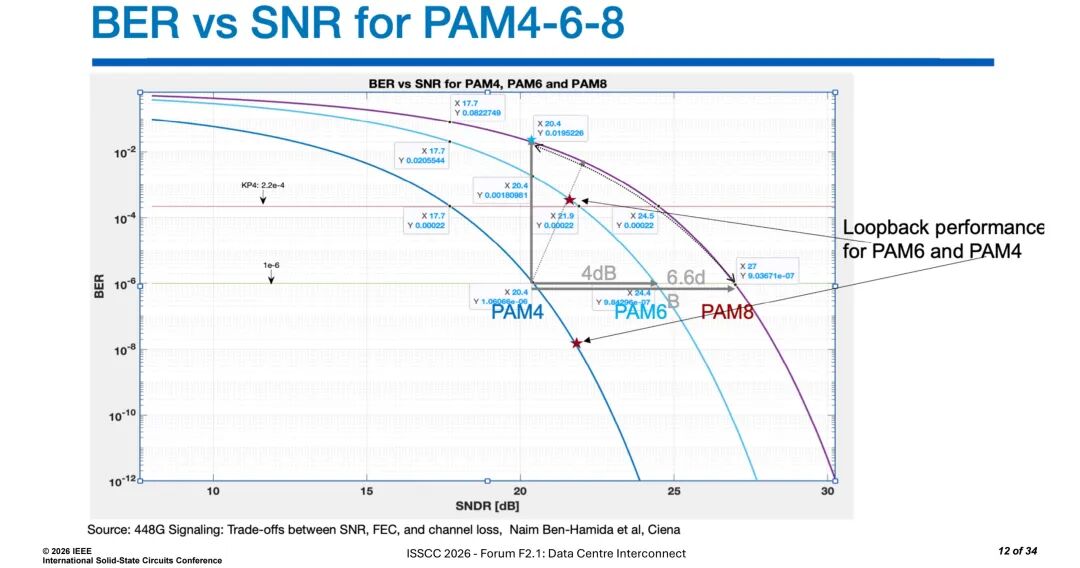

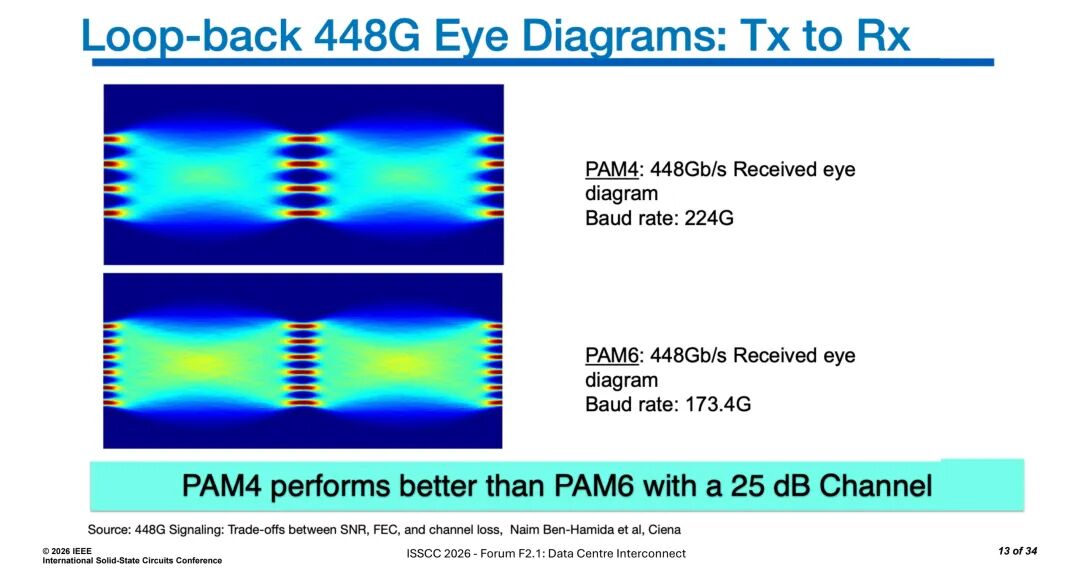

误码率(BER)与信噪比(SNR)的测试数据,进一步验证了PAM4调制的性能优势。在KP4 FEC对应的2.2e-4误码率要求下,PAM6相比PAM4需要额外4dB的SNR预算,PAM8则需要额外6.6dB的SNR预算,高阶调制带来的SNR代价极为显著。同时,在25dB通道下的448Gb/s环回测试中,PAM4的接收眼图表现显著优于PAM6,在长距传输场景下的可靠性更有保障。

五、400G-PAM4系统的连接器与信号完整性挑战

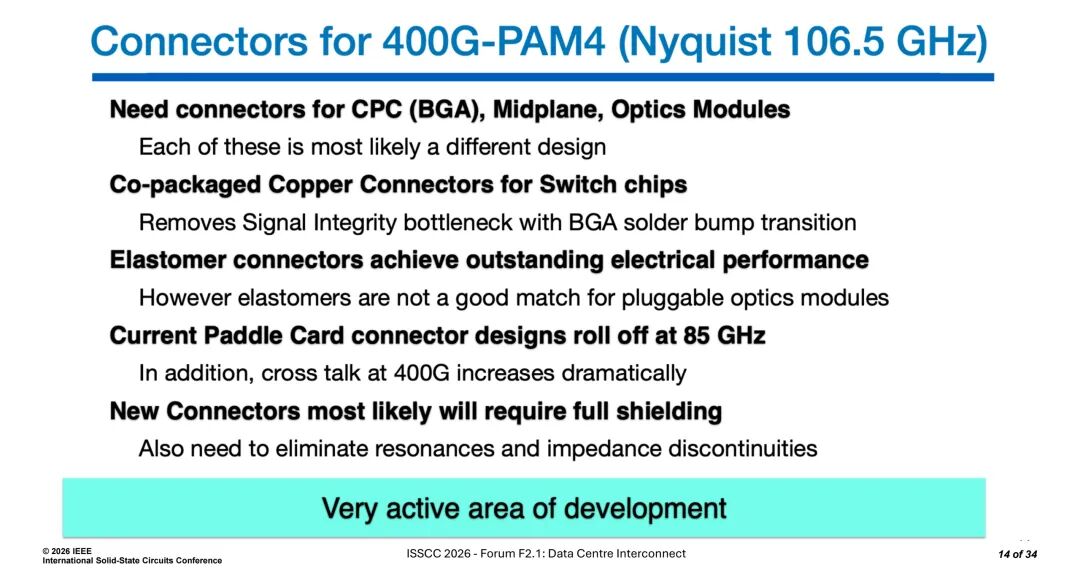

400G-PAM4的奈奎斯特频率达到106.5GHz,对系统级的连接器设计与信号完整性管控提出了前所未有的全新要求,也成为下一代高速互连系统的核心攻坚方向。行业需要开发适配CPC(BGA)、中板、光模块三类核心场景的全新连接器,且不同场景的应用需求差异较大,大概率需要采用不同的设计方案。面向交换芯片的共封装铜连接器(CPC),能够消除BGA焊球过渡带来的信号完整性瓶颈,是实现高带宽通道的最佳解决方案,其中CPC flyover电缆是该方案最优的实现形式。弹性体连接器虽然可实现出色的电气性能,但其机械特性与可插拔光模块场景的适配性极差,无法规模应用。当前主流的paddle card连接器设计,在85GHz频率下就出现了明显的性能滚降,无法满足106.5GHz的带宽需求,同时400G场景下的通道串扰会随频率升高急剧增加,进一步恶化信号完整性。

因此,面向400G-PAM4的新型连接器,大概率需要采用全屏蔽设计,同时需要通过结构优化消除谐振与阻抗不连续问题,目前该领域正处于全行业活跃研发的阶段。

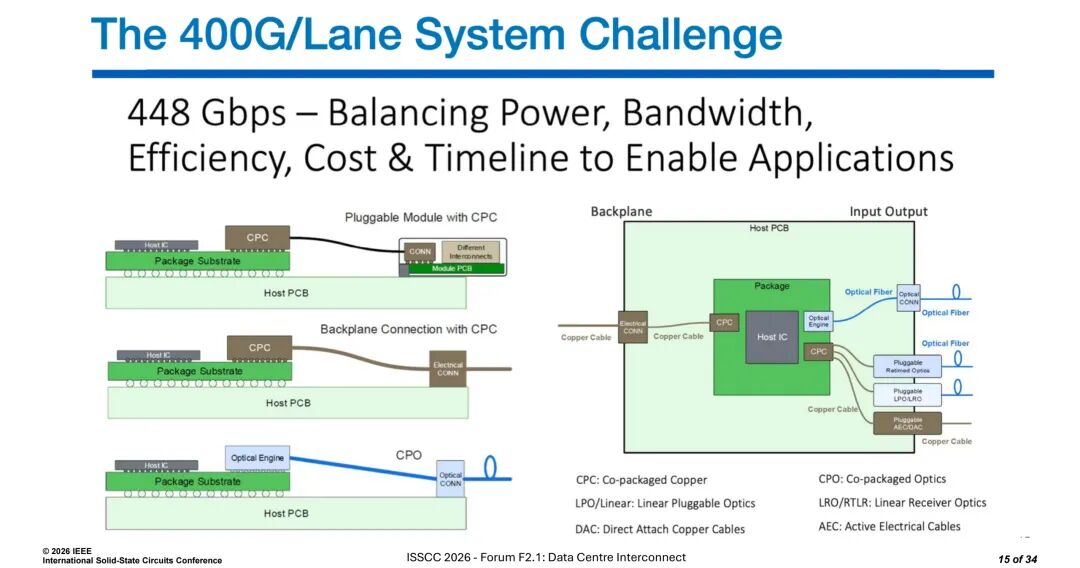

六、400G/通道多形态实现方案与仿真验证 400G/通道的高速互连系统,存在多种技术实现形态,报告中对核心术语给出了明确定义:CPC为共封装铜连接器,CPO为共封装光学,LPO/Linear为线性可插拔光模块,LRO/RTLR为线性接收光模块,AEC为有源电电缆,DAC为直连铜电缆,不同技术形态对应了不同的传输场景与系统需求。

3200G(8x400G)可插拔光模块采用8x400G-PAM4的核心架构,需要配套全新设计的高带宽电连接器,支持线性或LRO/TRO接口,光器件将采用EML、InP或TFLN方案,预计将于2028年伴随新连接器的成熟实现规模量产。

共封装光学(CPO)方案的核心优势在于极短的电通道设计,50mm走线@0.34dB/mm的插入损耗仅为17dB,能够大幅降低电通道的损耗与功耗,但该方案受限于技术平台的成熟度:硅光方案在400G-PAM4场景下已出现带宽不足的问题,需要切换至InP、TFLN或有机材料等新型光子学平台,而这些新技术平台尚未完成与CPO量产流程的适配,当前主流的CPO制造工艺仍基于硅光平台,因此CPO的单通道速率大概率会在200Gbps阶段停留更长时间。

更高通道数的可插拔模块是重要的补充演进方向,典型方案为64通道@400Gbps,可实现25.6T的单模块容量,仅需8个模块即可搭建204.8T的交换机系统,能够大幅缩短系统电通道长度,目前行业对高通道数可插拔模块的关注度正在持续提升,其面临的热挑战可通过液冷方案解决,但该方案的规模商用需要多厂商的标准化协同。

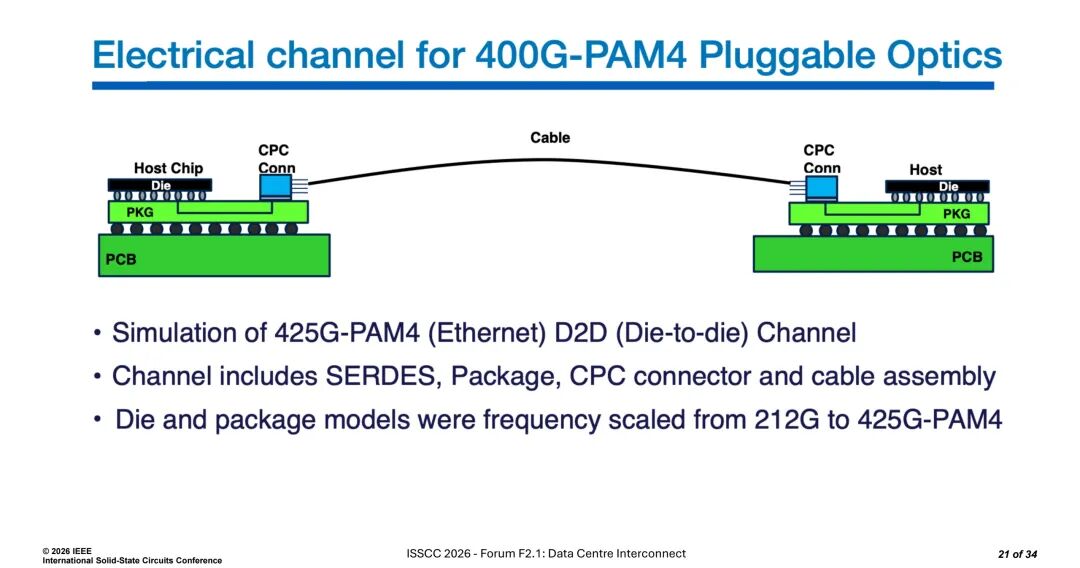

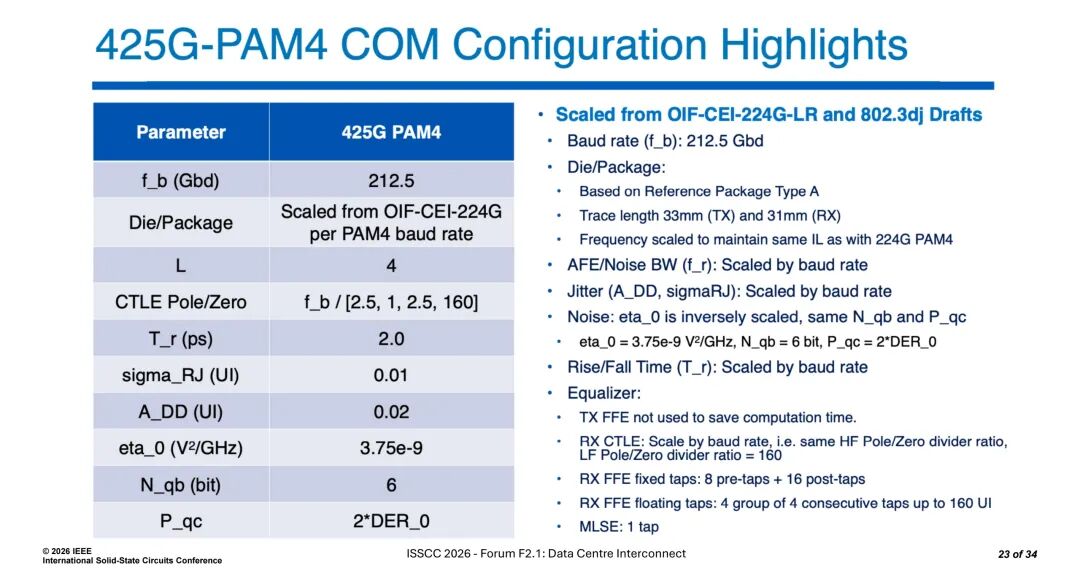

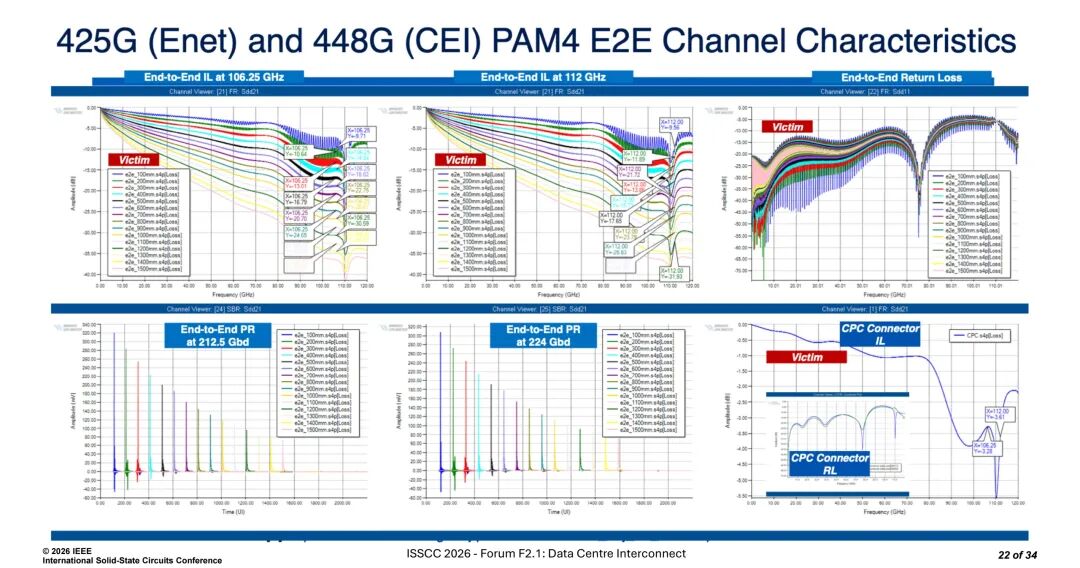

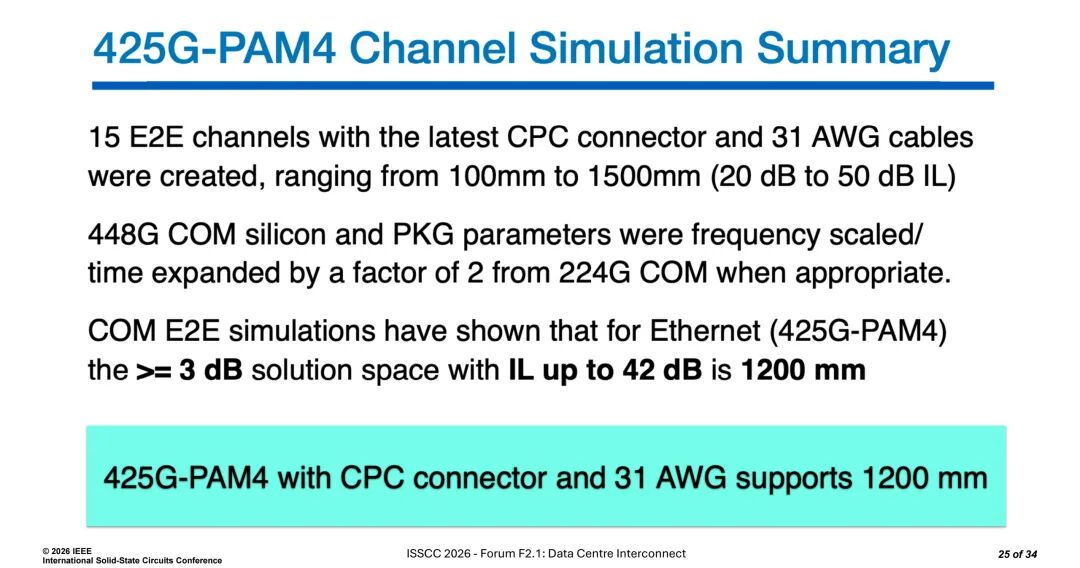

针对400G-PAM4电铜通道的通道工作裕量(COM)仿真,完整验证了该方案的传输能力边界。仿真基于以太网KP-FEC场景开展,425Gbps PAM4对应的奈奎斯特带宽为106.25GHz,仿真模型基于OIF-CEI-224G标准与802.3dj草案,将212G到425G-PAM4的芯片与封装模型按波特率进行频率缩放,完整覆盖了SERDES、封装、CPC连接器与线缆组件的端到端全通道。

仿真的核心设置如下:425G-PAM4的波特率为212.5Gbd,芯片与封装基于参考封装Type A,TX走线长度33mm、RX走线31mm,按波特率频率缩放以保持与224G PAM4相同的插入损耗;AFE/噪声带宽、抖动、噪声、上升/下降时间均按波特率对应缩放;RX CTLE按波特率缩放,保持相同的高频零极点分频比与160倍的低频零极点分频比;RX FFE配置为8个前置抽头+16个后置抽头,另有4组4个连续抽头的浮动抽头,最高支持160UI;MLSE为1抽头。

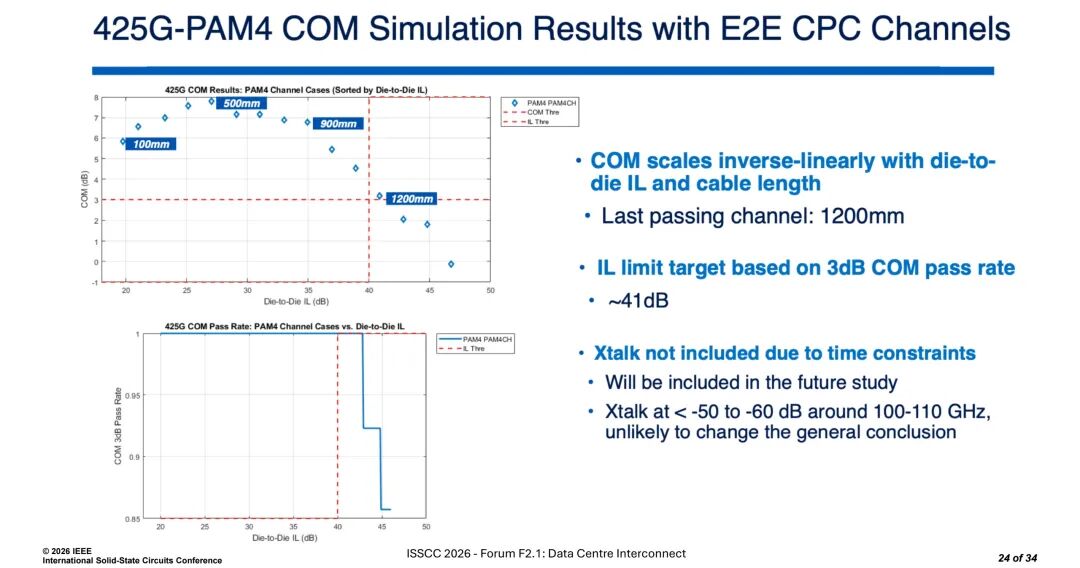

本次仿真共覆盖了15条采用最新CPC连接器与31AWG线缆的端到端通道,通道长度从100mm到1500mm不等,对应插入损耗范围为20dB到50dB。仿真结果显示,在以太网425G-PAM4场景下,COM不低于3dB的解决方案空间,对应通道插入损耗最高为42dB,匹配的线缆长度最长为1.2m;同时,通道串扰在100-110GHz范围内为-50至-60dB,不会对整体仿真结论产生显著影响。

七、铜传输的物理极限与新兴替代技术

400G-PAM4场景下,传统铜通道已经接近其物理传输极限,面临着多重无法回避的技术挑战。超过100GHz的带宽需求,对传统系统设计带来了极大的考验:趋肤效应与介质损耗会随频率升高急剧增加,直接限制了铜缆的最大传输距离;频率相关的损耗会带来严重的码间干扰(ISI),恶化信号质量;通道中任何阻抗失配都会产生额外的信号干扰,即使是极小的制造公差导致的几何结构变化,也会对信号完整性产生显著影响;通道内外的串扰会随频率升高而急剧加剧,同时全屏蔽连接器的小型化也存在明确的物理极限。铜通道突破传输极限的唯一路径是采用更高阶调制,但更高阶调制会带来OSNR代价、额外FEC开销与功耗增加等一系列系统代价,并非无成本的解决方案。

空芯波导太赫兹射频传输技术,是10-20米中短距互连场景极具潜力的新兴替代方案,能够解决传统铜通道的物理极限问题。太赫兹射频信号可在空芯波导中实现10-20米的稳定传输,且传输过程中无趋肤效应、无介质损耗,码间干扰也大幅降低。该方案的核心优势在于,信号全程在电域内传输,无需进行光电-电光转换,因此无需激光器、调制器、光电探测器等光器件,也无需微米级的光学精密对准,相比高速光模块具备更低的成本与功耗,可匹配数据中心scale-up场景的核心传输需求。 八、低功耗光技术的演进方向与集成挑战

单光纤对实现400Gbps传输带宽,存在多种技术实现方案,包括1x400G-PAM4(106GHz奈奎斯特)、2x200G-PAM4-FR2(2个波长,53GHz奈奎斯特频率)、4x100G-PAM4-FR4(4个波长,26.5GHz奈奎斯特)、8x50G-NRZ-FR8(8个波长,26.5GHz奈奎斯特),不同方案对应了不同的功耗、复杂度与应用场景。其中,无需高速SERDES的Slow & Wide(慢而宽)方案,是低功耗光技术的核心演进方向,能够实现当前最低的整体功耗。

该方案功耗降低的核心逻辑,是通过架构优化消除了高速SERDES带来的功耗开销,这需要交换芯片与EIC/硅光芯片的极紧密耦合;400G/波长方案虽然已经具备优异的功耗效率,但Slow & Wide方案通过消除高速SERDES,实现了更极致的功耗优化,其功耗水平与高速长距SERDES相当。

Slow & Wide光学方案(也被称为“超越CPO”方案)的商用落地,需要实现硅级集成来彻底消除高速SERDES的功耗,通常采用50G-NRZ或类似的并行接口,需要配套高密度硅光微环调制器或同等尺寸的调制器,以及外部DWDM 200GHz间隔的激光器阵列或梳状激光器。该方案面临的核心挑战在于制造工艺与光纤耦合:当前硅光工艺采用复杂的混合键合工艺,光纤耦合单元(FAUs)的技术虽有进展,但尚未实现100%的量产良率,而昂贵的GPU或高速交换芯片无法承受任何良率损失,因此全集成光学的落地,是先进封装领域面临的重大技术挑战。 九、核心结论与产业路线总结 基于全系列的技术分析、仿真验证与产业链调研,报告给出了四大核心结论,完整定义了400G/通道互连技术的发展边界与商用前景:

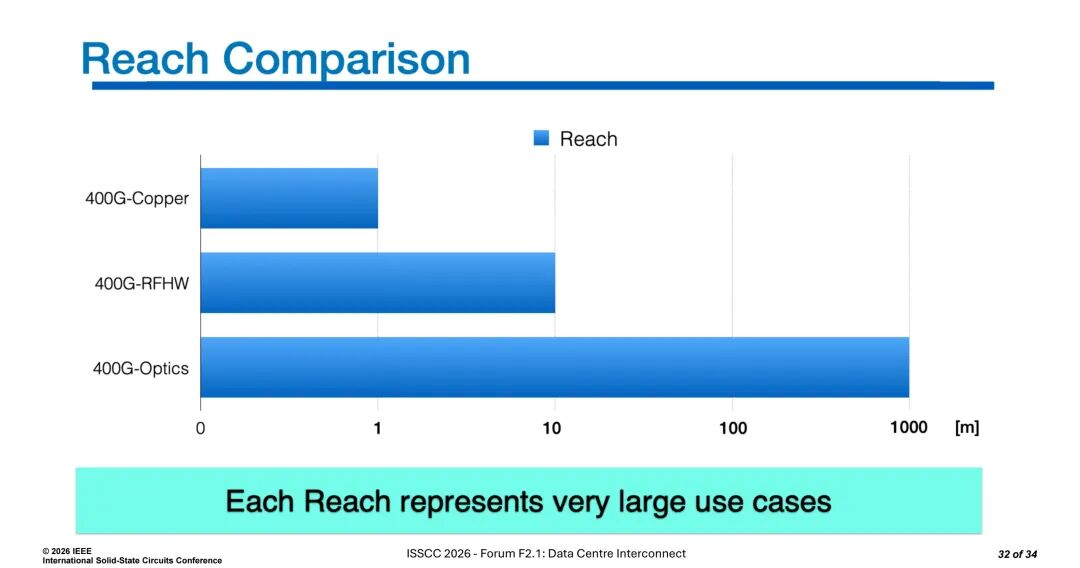

1. 单通道400G-PAM4铜缆方案具备技术挑战性,但具备商用落地的可行性,采用45dB长距SERDES与31AWG双轴铜缆的方案,最大传输距离极限为1.2米; 2. 单通道400G-PAM4光模块方案技术路径成熟,可支撑规模商用,其落地需要InP、TFLN或其他高带宽调制器技术的配套支撑; 3. 单通道400G-PAM4空芯波导射频方案正处于研发阶段,该方案可在无需光器件与光学精密对准的前提下,实现10-20米的稳定传输距离; 4. 400G“Slow & Wide”多波长DWDM光模块方案正处于研发阶段,其商用落地需要极高良率的硅级集成技术支撑,全集成光学是该方案面临的先进封装核心挑战。

在产业路线上,报告定义了不同技术方案的商用节奏与应用场景。400G-PAM4技术将于2028年成为数据中心互连的主流技术,相比当前主流的200G方案,具备显著的端口密度、单位比特成本与功耗优势。400G-PAM4铜缆的传输距离限制在1米左右,仅适用于机箱内与机架内的短距连接场景;400G-PAM4空芯波导射频方案在10-20米传输场景极具发展潜力,完美匹配数据中心scale-up场景的核心需求;400G-PAM4光模块方案仅需要配套低损耗电通路,技术风险较低,行业核心的竞争焦点在于哪种调制器技术能够最终实现最高的量产规模;400G-DWDM低功耗“Slow & Wide”光模块方案仍处于研发阶段,需要采用与其他400G接口完全不兼容的硅级集成架构,落地节奏相对滞后。报告最终指出,单通道400G是数据通信领域的下一个核心技术节点,也极有可能是该领域的最后一个技术节点。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-02-26,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读