博通:200G PAM4 VCSEL技术研发与VCSEL NPO在AI scale up网络的应用探索

博通:200G PAM4 VCSEL技术研发与VCSEL NPO在AI scale up网络的应用探索

光芯

发布于 2026-03-02 21:50:49

发布于 2026-03-02 21:50:49

一、200G PAM4 VCSEL的器件设计与制造

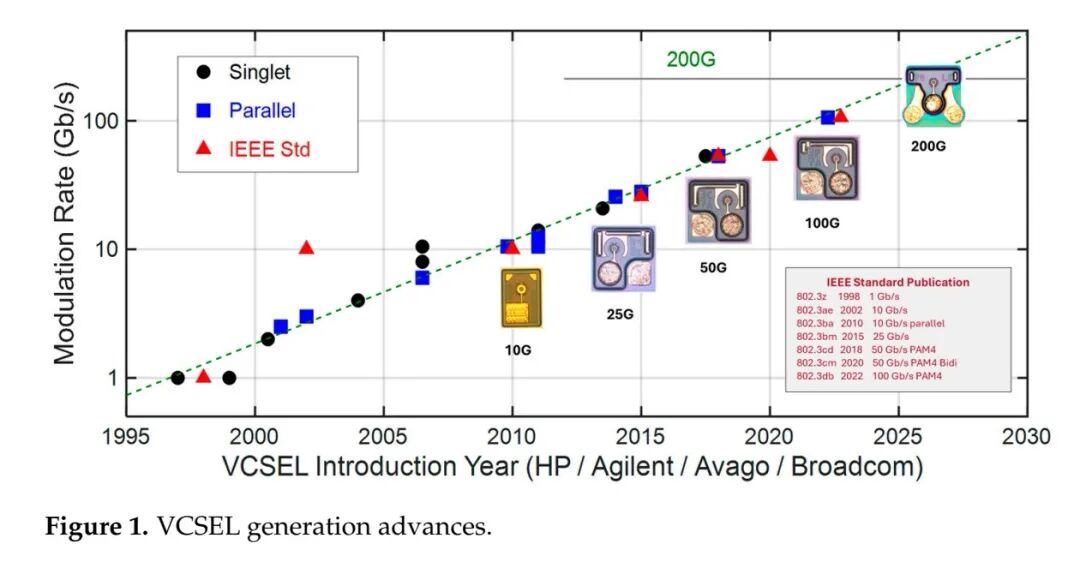

为实现单通道200 Gbps多模光链路的PAM4传输,通过仿真模型确定了200G VCSEL的核心性能阈值:支持106.25 Gbd速率时,器件-3 dB带宽需大于35 GHz,相对强度噪声(Relative Intensity Noise,RIN)需低于-152 dB/Hz。本款200G PAM4 850 nm VCSEL的设计基于博通已量产的100 Gbps PAM4 VCSEL成熟外延与制造工艺流程,在继承其高量产性、宽温性能及现场可靠性的基础上,完成了带宽、噪声与热特性的多维度优化,核心设计目标并非追求极致的速率与低噪声,而是打造性能优化且可靠性达标的工程化器件。

器件采用湿法横向氧化工艺制备氧化层,通过沟槽刻蚀暴露高铝含量氧化层后完成氧化,实现载流子与光子的有效限制;同时采用多能量注入工艺降低bonding焊盘电容,减少电学寄生参数对器件高速调制性能的影响。在100 Gbps VCSEL设计基础上,该器件同步实现了带宽提升、RIN降低与热阻优化,通过改进热阻特性最小化结温上升,为器件在高速工作条件下的稳定性提供保障,其整体器件结构与已验证的100 Gbps VCSEL设计一脉相承。

二、200G PAM4 VCSEL的核心性能表征

基于上述设计完成的200G PAM4 VCSEL器件,通过直流特性、小信号调制响应、噪声性能及大信号响应等多维度测试完成全面表征,所有测试结果均达到并满足200 Gbps单通道传输的核心指标要求,且链路传输稳定性得到充分验证。

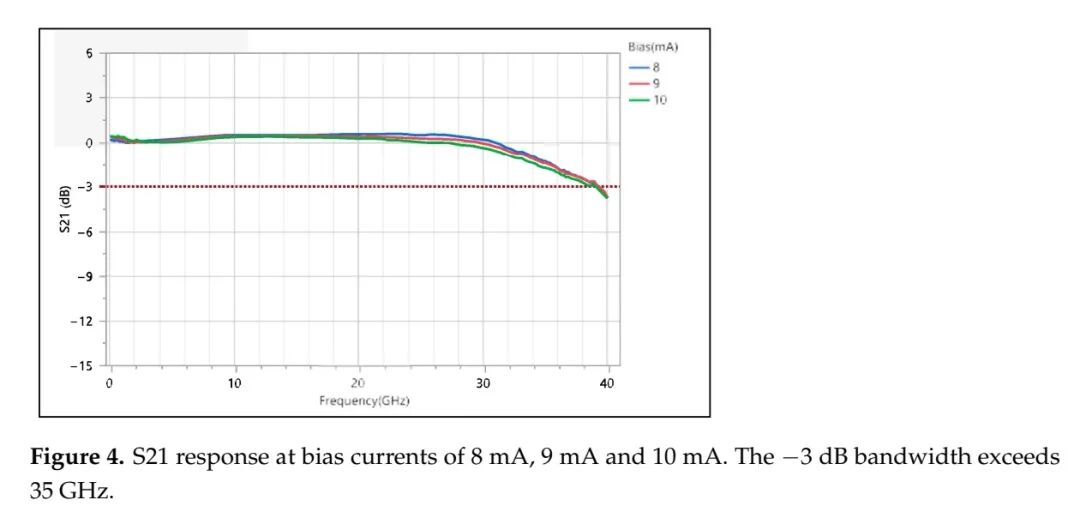

在直流特性方面,典型200G VCSEL在9 mA偏置电流下,光输出功率超过3 mW,工作电压约2.5 V,具备良好的光电转换效率,为实际应用中的驱动设计提供了基础。小信号调制响应测试通过FormFactor/Cascade空气共面探针对晶圆进行直接探测,结合Agilent E8364B网络分析仪与35 GHz以上带宽的高速PD完成,测试结果显示器件在8 mA、9 mA、10 mA偏置电流下均呈现平坦的阻尼型S21响应,9 mA偏置下-3 dB带宽超过35 GHz,完全满足设计阈值;研发团队同时证实,通过进一步降低电容、电阻等电学寄生参数,该VCSEL的光调制带宽有望突破45 GHz。

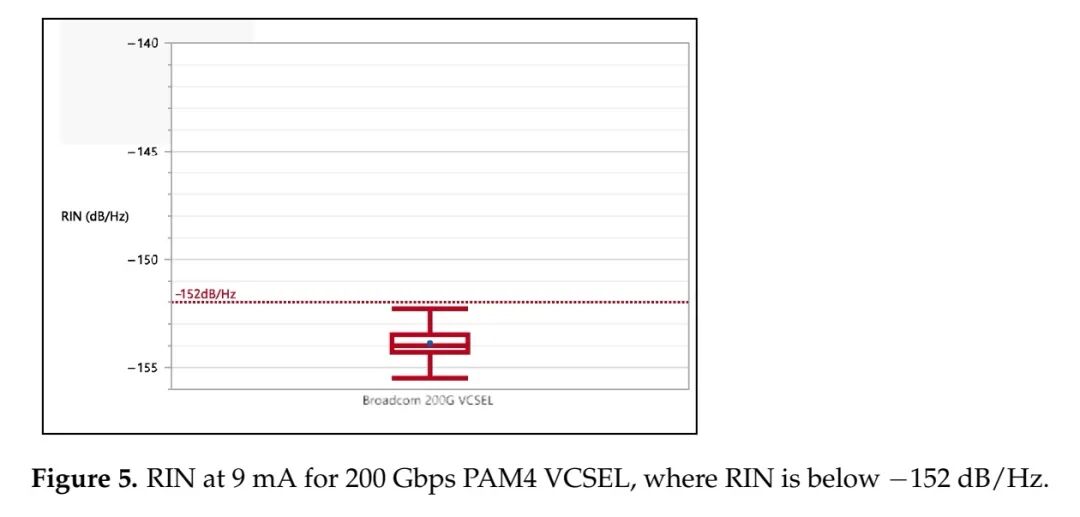

噪声性能是影响光链路传输质量的关键因素,200G VCSEL通过设计优化抑制了模式拍频等因素引发的功率波动,将9 mA偏置下的RIN指标降至-152 dB/Hz以下,大幅降低了器件噪声对整个光链路总噪声的贡献,为低误码率传输奠定了基础。

大信号响应测试则模拟了实际场应用的驱动与传输条件,采用Keysight M8199B任意波形发生器生成106.25 GBd PAM4 PRBS13Q码型,设置消光比2.2 dB并施加7抽头发射端有限长单位冲激响应(Tx FIR)均衡;通过65 GHz带宽偏置器合流直流偏置与交流调制信号,经射频探针对器件键合焊盘馈电,光信号通过显微光学系统耦合至多模光纤;接收端采用Keysight 200G多模DCA-M,结合自适应25抽头FFE与53.1 GHz SIRC滤波器完成光波形表征。

测试结果显示,该器件在不同长度、不同有效模带宽(Effective Modal Bandwidth,EMB)的多模光纤传输后均呈现清晰的开眼图:2 m标准OM4光纤、30 m EMB 4700 MHz·km的OM4光纤,以及50 m EMB 7500 MHz·km的康宁定制OM4光纤,均能稳定支持200 Gbps PAM4传输,其中高EMB定制光纤将200G链路的无中继传输距离拓展至50 m。链路误码率测试进一步验证了传输稳定性,在50 m OM4光纤上开展的9小时连续流量测试中,仅出现最多5个可纠正帧错误,无任何不可纠正错误,展现出优异的链路工作稳定性。

三、200G PAM4 VCSEL的可靠性测试与分析

可靠性是光器件实现工程化与规模化应用的核心考量,而结温控制是提升VCSEL老化寿命的关键——器件结温由耗散电功率与自身热阻共同决定,高速VCSEL所需的高电流密度会带来更大的焦耳热,且小尺寸器件的热阻更高,易导致结温上升进而加速器件退化。为解决这一问题,200G VCSEL在设计中采用了低热阻抗的分布式布拉格反射镜(DBR),有效降低了器件工作时的结温,为高可靠性提供了硬件基础。

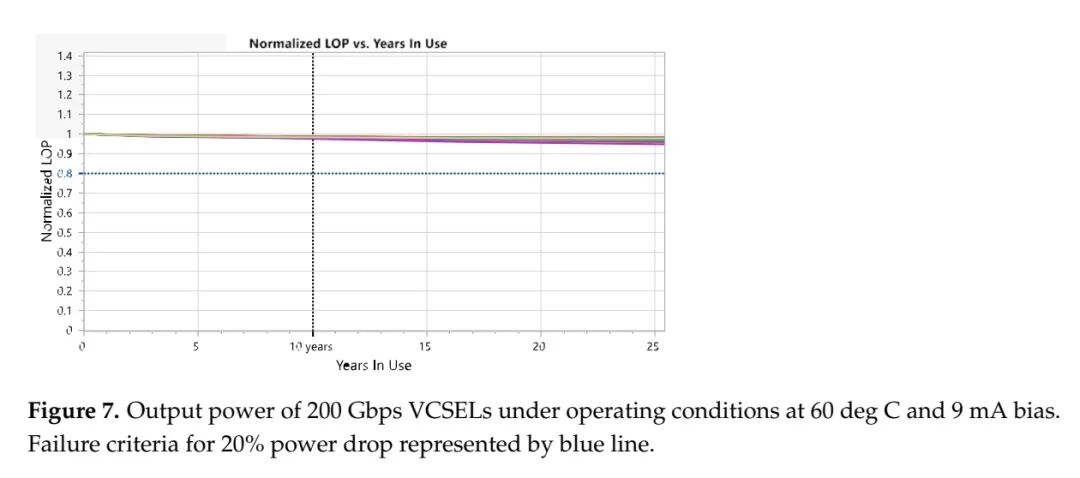

研发团队对200G PAM4 VCSEL开展了初步可靠性测试,器件封装于TO管座中,在100℃高温、9 mA恒定偏置条件下进行应力测试,定期取出器件并在室温下完成光电性能复测,测试方法与数据分析均遵循半导体激光器的标准可靠性模型与规范。在60℃、9 mA的实际使用条件下(可通过热电制冷器(TEC)将VCSEL衬底温度稳定在该水平及以下),器件的归一化输出功率随使用时间的退化趋势与成熟的100 Gbps VCSEL基本一致,呈现缓慢、平稳的退化特征,本次测试设定的器件失效判据为输出功率下降20%。目前更全面的可靠性测试仍在进行中,后续将进一步验证加速模型,补充更完善的器件老化寿命统计数据。

四、AI scale up网络的互连需求与铜互连的技术局限性

AI scale up网络的发展要求实现更多加速器(XPU,为GPU、张量处理器等各类加速芯片的通用称谓)的互联互通,以支撑大规模高带宽内存交互与高效并行计算,这对互连链路的带宽、传输距离、能效与可靠性提出了严苛要求。而传统铜互连技术在AI scale up网络中存在显著的传输局限性,成为制约XPU集群扩展的核心因素。

当前直连铜缆(DAC)支持100 Gbps SerDes通道的传输距离仅为4~5 m,受抖动、插入损耗等信号损伤限制;下一代200 Gbps SerDes因奈奎斯特频率下的插入损耗更高,DAC传输距离进一步缩短至1~2 m,即便通过增加重定时器将传输距离拓展至7 m,也会带来显著的成本与功耗上升。这一特性使得铜互连仅能实现单机架内或最多两个机架间的XPU连接,限制了单跳连接的XPU数量。

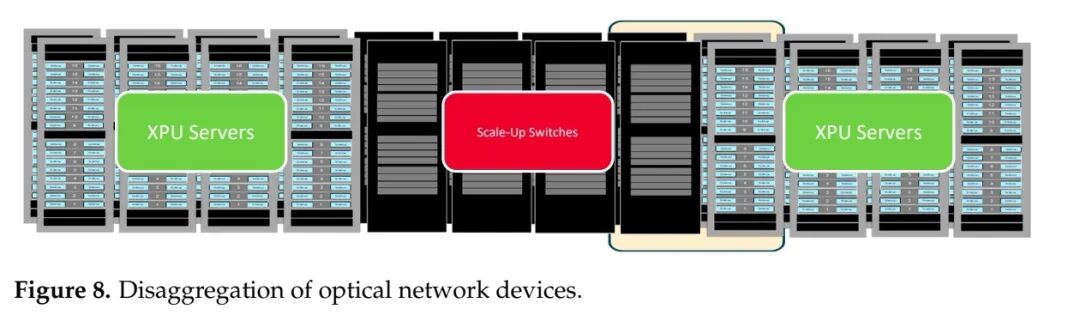

与之相比,光互连通过将主机专用集成电路(ASIC)的电信号转换为光信号在光纤中传输,可实现50 m及更远距离的高速率传输,能够支持网络解耦(network disaggregation)设计,成为AI scale up网络互连的核心解决方案。面向AI scale up网络的光互连需满足四大核心技术指标:超高的能量效率,以匹配数据中心的低功耗整体要求;高可靠性,最大化XPU的利用率;高逃逸带宽密度,适配有限的物理布线空间;低成本,实现与铜互连的性价比对标,而VCSEL基光互连技术凭借其固有特性,成为满足上述指标的优选方案。

五、面向AI scale up网络的VCSEL基近封装光学(NPO)方案提案

依托200G PAM4 VCSEL的优异性能、高现场可靠性与低功耗特性,本文提出了VCSEL NPO架构,针对AI scale up网络的互连需求完成了核心设计与性能评估,该方案在能量效率、可靠性、逃逸带宽密度及成本四大维度均满足AI scale up网络的应用要求,成为突破铜互连传输限制的关键技术路径。

5.1 3.2 Tbps VCSEL NPO光引擎核心设计

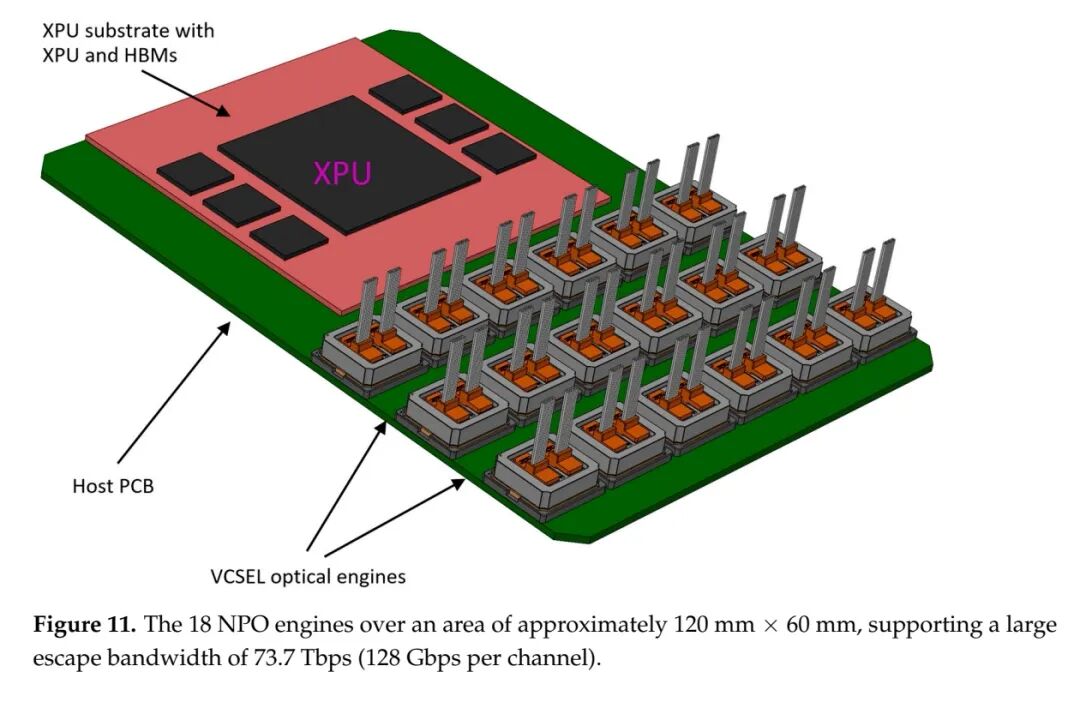

本方案提出的3.2 Tbps VCSEL NPO光引擎为自包含封装结构,尺寸为19 mm×19 mm,内部集成4个1×8 VCSEL阵列及对应的驱动集成电路(IC)、4个1×8光电二极管(PD)阵列及对应的跨阻放大器(TIA)IC,同时集成MCU。该引擎单通道支持100~128 Gbps的数据速率,整体可实现3.2~4.1 Tbps的总带宽;为满足该高速传输需求,光学组件的奈奎斯特频率需大于32 GHz,而博通已量产的100G VCSEL即便在75℃高温衬底条件下,-3 dB带宽仍能超过32 GHz,可完全适配该设计要求。

NPO光引擎的发射与接收部分可单独封装为独立功能单元,VCSEL与PD阵列通过引线键合至光引擎衬底,光信号通过高性价比的塑料阵列透镜垂直耦合至多模光纤,实现光信号的高效、低成本传输,该封装方式兼顾了器件集成度与工艺可实现性。

5.2 NPO方案的核心技术优势

1. 超高能效:基于CMOS工艺的VCSEL驱动器与TIA可实现极高的功率效率,包含VCSEL在内的NPO整体能量效率约1 pJ/bit,单台NPO器件功耗低于4 W,远优于硅光子光互连5~10 pJ/bit的能效水平。硅光子互连功耗偏高的核心原因在于DFB激光器需要更高的驱动电流,以保证向硅调制器注入足够的光功率,而VCSEL的低驱动特性成为其能效优势的关键。

2. 高可靠性:博通已出货超1亿个50G/100G VCSEL通道,累计实现超5万亿小时的现场器件服务时间,无任何因VCSEL可靠性问题导致的现场退货,其失效单位(FIT)率低于0.1,对NPO整体的可靠性风险可忽略不计。结合CMOS工艺的成熟性与多模光器件的规模化制造能力,NPO的整体FIT率有望与有源铜互连持平,完全满足AI scale up网络对高可靠性的需求。

3. 高逃逸带宽密度:将18个NPO引擎以3×6的布局方式集成,可在约120 mm×60 mm的物理面积内实现最高73.7 Tbps的XPU逃逸带宽,逃逸带宽密度大于0.6 Tbps/mm,能够适配XPU带宽向50 Tbps及以上演进时的高密度互连需求,解决了有限布线空间下的带宽瓶颈问题。光光纤可灵活路由至XPU服务器的前面板或背板,也可通过服务器内的光纤重排或机架顶部的光纤交换盒实现光连接的灵活配置,适配不同AI scale up网络的应用场景需求。

4. 低成本工程化潜力:高速光互连的成本核心贡献者为DSP芯片,而NPO因紧邻SerDes布局,内部电链路长度短、插入损耗低,无需DSP即可完成信号损伤校正,大幅降低了核心器件成本;同时19 mm×19 mm的小尺寸封装,相较于同速率标准光可插拔模块进一步降低了材料成本;此外,一维VCSEL/PD阵列的光学透镜设计比多维阵列更简单,简化了制造工艺并降低了生产升本。在高量产条件下,该NPO方案的每Gbps成本可与有源铜缆持平。

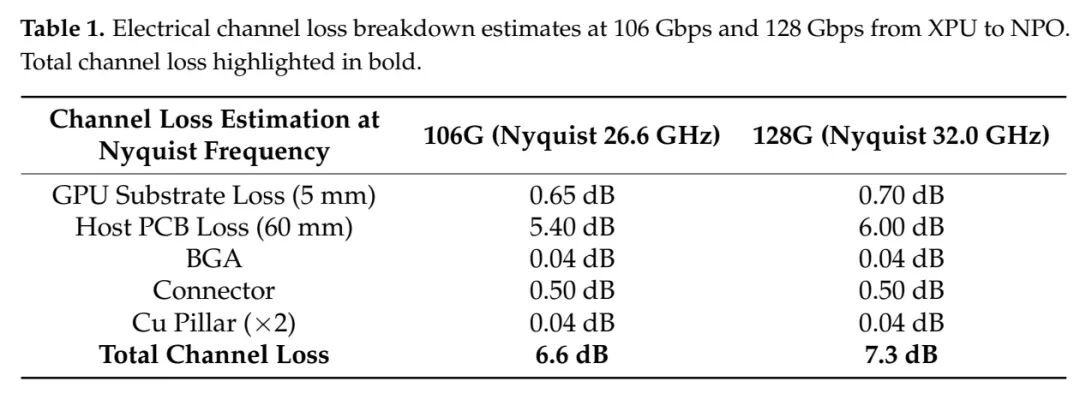

5.3 NPO设计的关键考量——电插入损耗优化

NPO与标准光链路的核心区别在于其电插入损耗预算依赖于XPU SerDes的性能,而NPO紧邻SerDes的布局成为降低电插入损耗的核心优势,大幅降低了对SerDes预加重、均衡等性能的要求。以18个NPO引擎的布局为例,SerDes到NPO的最长电走线约65 mm,最短仅15 mm,采用低损耗介质材料时,106 Gbps(奈奎斯特26.6 GHz)下的电通道总插入损耗约6.6 dB,128 Gbps(奈奎斯特32.0 GHz)下约7.3 dB,损耗构成主要包括GPU衬底损耗、Host PCB损耗、BGA、连接器及铜柱损耗等。

相较于IEEE标准中光模块8~16 dB的电插入损耗(BGA至DRV/TIA IC凸点),NPO不仅整体损耗值更低,且不同通道间的损耗差异更小,这一特性大幅降低了对XPU SerDes的性能要求,简化了AI scale up网络的整体系统设计。

六、讨论与结论

本文研发的200G PAM4 850 nm VCSEL通过差分增益提升、载流子传输优化、腔失谐精准调控及热阻降低等设计改进,实现了-3 dB带宽超35 GHz、RIN低于-152 dB/Hz的核心性能,大信号测试证实其可在2 m、30 m、50 m多模光纤中稳定实现200 Gbps PAM4传输,50 m OM4光纤链路9小时测试无不可纠正错误,展现出优异的高速传输稳定性。初步可靠性测试显示,该器件在60℃使用条件下的功率退化趋势与成熟的100 Gbps VCSEL一致,低热阻抗DBR设计为结温控制与长老化寿命提供了保障,后续将通过更全面的测试完善可靠性模型与寿命统计数据。该200G VCSEL设计也将推动下一代212.5 Gbps单通道商用光器件的落地。

依托200G VCSEL的技术优势提出的VCSEL基NPO方案,成为AI scale up网络光互连的关键赋能技术,有效突破了铜互连的传输距离限制,实现了50 m及更远距离的高速光传输,支撑了AI scale up网络的解耦设计与多机架间XPU的全互连,使单跳连接的XPU数量仅受交换机基数限制。该NPO方案全面满足AI scale up网络的四大核心要求:1 pJ/bit的超高能量效率远优于硅光子光互连;VCSEL低于0.1的FIT率为NPO提供了极致的可靠性基础;大于0.6 Tbps/mm的逃逸带宽密度适配了XPU的高密度互连需求;高量产下有望与有源铜缆持平的每Gbps成本,具备工程化与规模化应用的潜力。同时,NPO紧邻SerDes的布局大幅降低了电插入损耗,减少了对XPU SerDes的性能要求,进一步简化了AI scale up网络的系统设计。

未来的研发工作将重点围绕NPO器件的整体FIT率展开全面评估,完善可靠性模型,进一步验证VCSEL基NPO方案的工程化与产业化可行性,使其成为铜互连的高效替代方案,满足AI、HPC和数据中心领域持续增长的高速互连需求。而VCSEL技术本身的持续演进,也将为更高速率、更长距离、更高集成度的光互连应用提供核心器件支撑。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-02-12,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读