走进 10G 采样的直采 ADC:奇历士CAE2200(带时域测试版)

走进 10G 采样的直采 ADC:奇历士CAE2200(带时域测试版)

云深无际

发布于 2026-01-07 14:20:16

发布于 2026-01-07 14:20:16

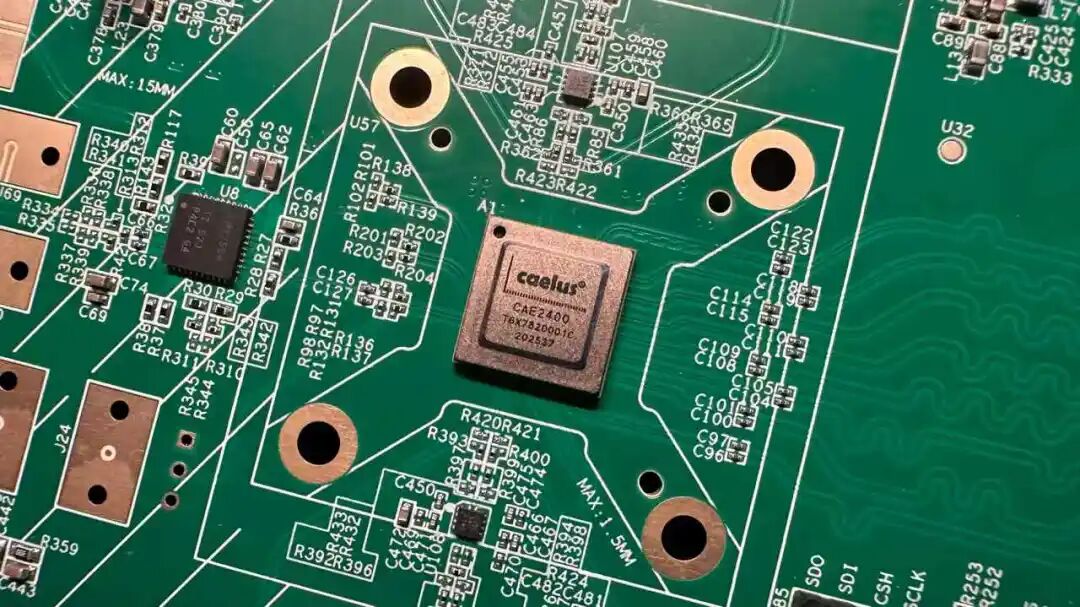

我之前介绍了几颗超高速 ADC,然后这次也是继续完善这部分的内容,还是我们的老朋友,奇历士:

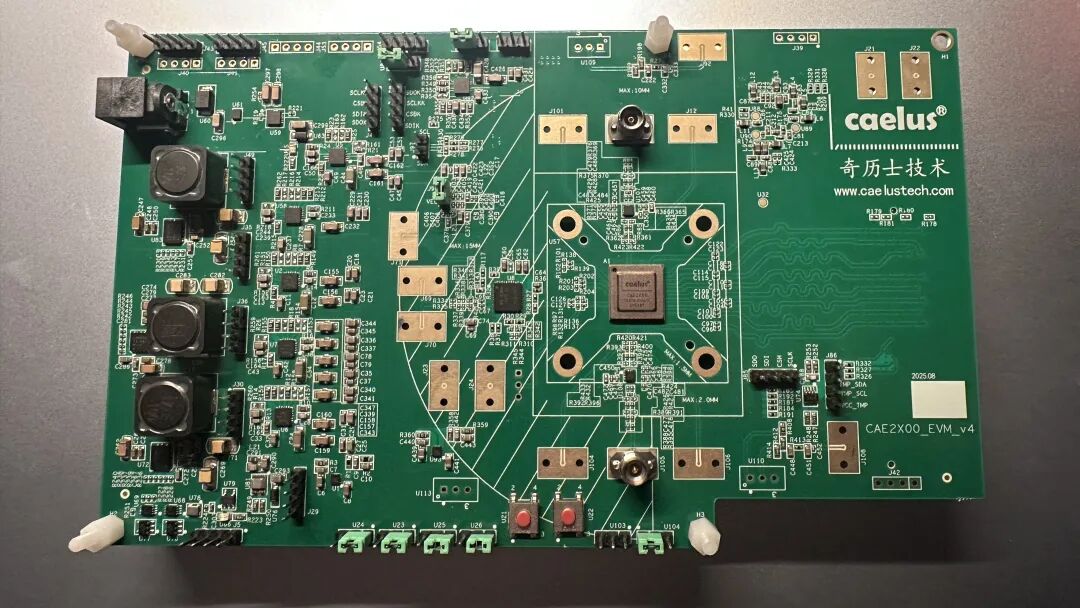

我要了一块评估板

我要了一块评估板

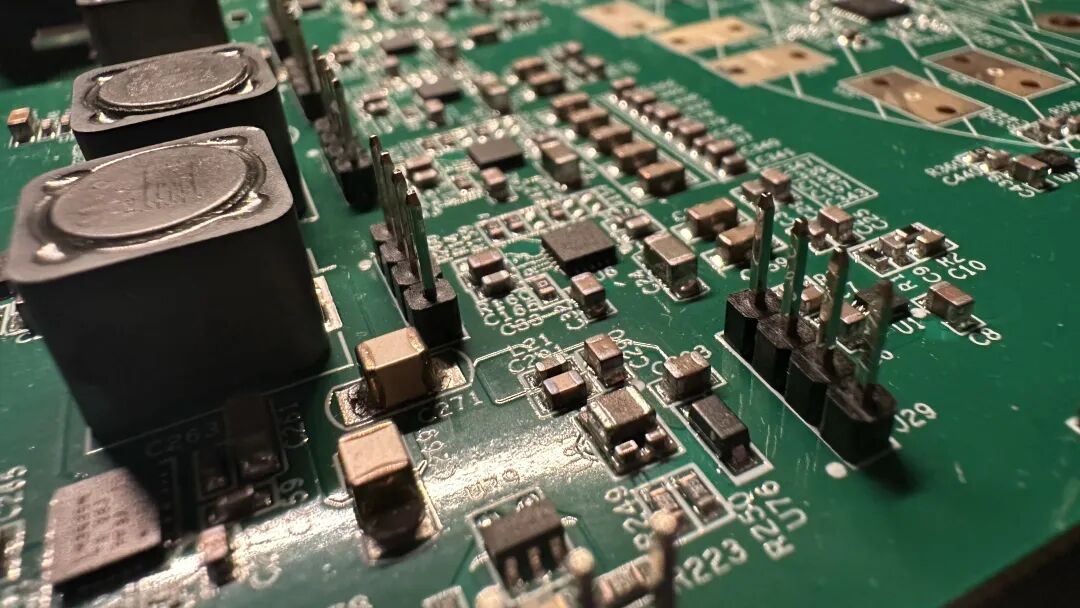

换个角度,很难想这样小小的身躯有这么大的能量

换个角度,很难想这样小小的身躯有这么大的能量

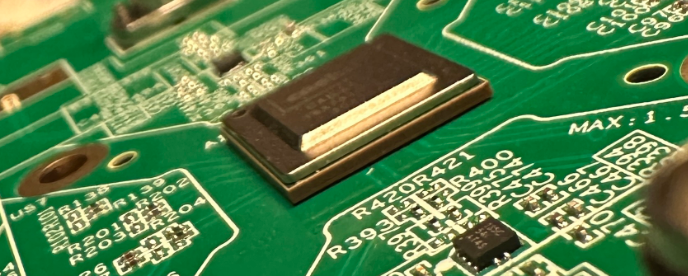

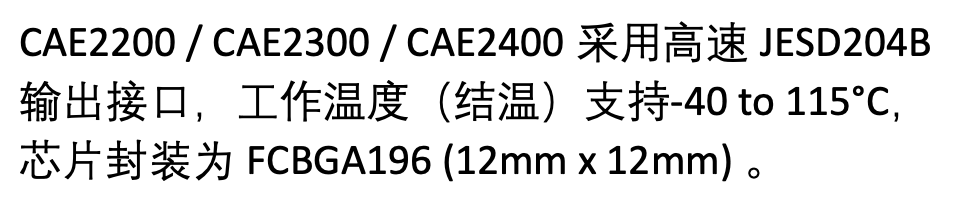

在开始参数的巴拉巴拉以前,我们可以先看看这个封装,就像这几天的 LLC 封装一样就是外壳把性能提升了。

反正是 BGA 的

反正是 BGA 的

看图知道,上面其实有个盖子

看图知道,上面其实有个盖子

FCBGA196 指的是一种带有196个焊球的倒装芯片球栅阵列集成电路封装用于高引脚数、高性能芯片,适用于高端示波器、频谱分析仪、宽带通信、高速数据采集等要求苛刻的应用,通过直接连接到基板,提供比旧封装更好的信号完整性和更小的尺寸。

FCBGA:倒装芯片球栅阵列,意味着芯片翻转过来,通过焊球直接连接到基板上,而不是通过引线键合。这样做主要还是为了优异的电气性能、散热性能和由于直接连接而降低的信号延迟。从本质上讲,它是一种特殊的、先进的半导体封装设计,适用于需要在紧凑空间内实现大量连接的芯片。

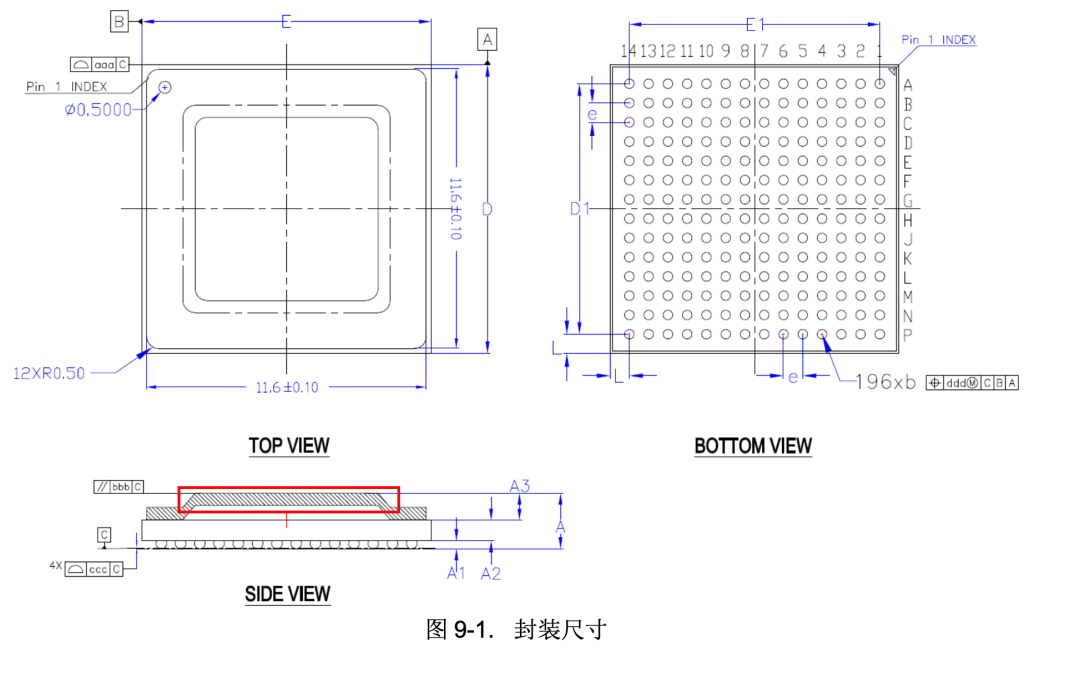

完整的开发板样子

完整的开发板样子

这样复杂的芯片,相关的外围配套电路也是非常复杂的

这样复杂的芯片,相关的外围配套电路也是非常复杂的

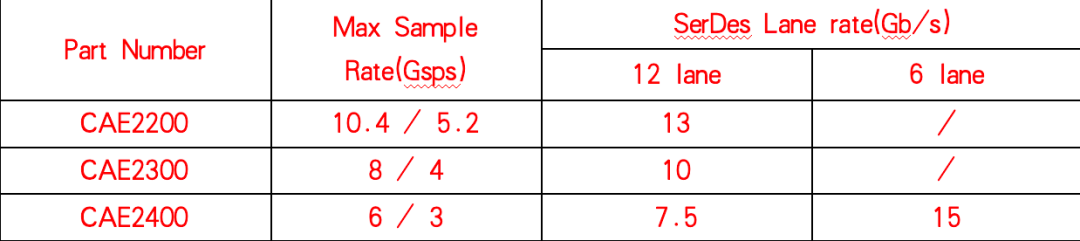

还是老样子,其实一次有三颗,都是一个家族的

还是老样子,其实一次有三颗,都是一个家族的

12-bit RF-sampling ADC,内部架构基本一致,主要差别是最高采样率和功耗/指标 binning。

CAE2200:单通道 10.4 GSPS,双通道 5.2 GSPS

CAE2300:单通道 8 GSPS,双通道 4 GSPS

CAE2400:单通道 6 GSPS,双通道 3 GSPS(我这次拿到的是双通道版本)

可以简单理解为:

CAE2200 = 这家族里最高采样率、性能最强的那档; CAE2300/CAE2400 = 降速版,SNR/SFDR/ENOB 略好一些,功耗更低。

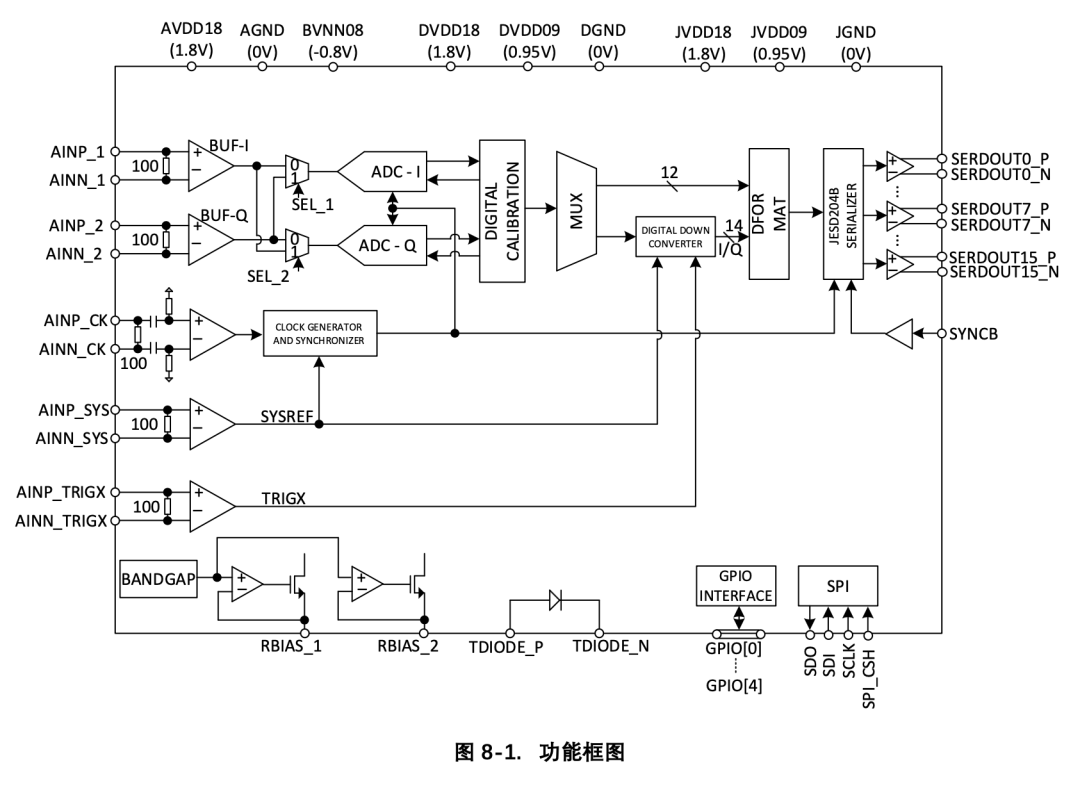

总体架构(功能框图解读)

看第 8.2 节的功能框图,可以概括为几大块:

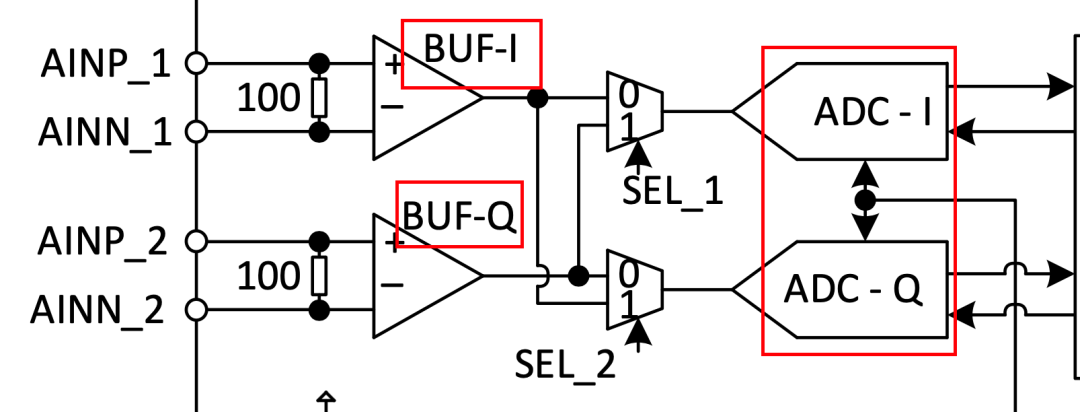

模拟前端 + ADC 内核

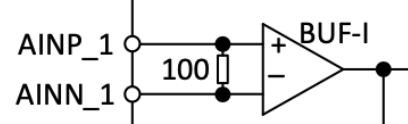

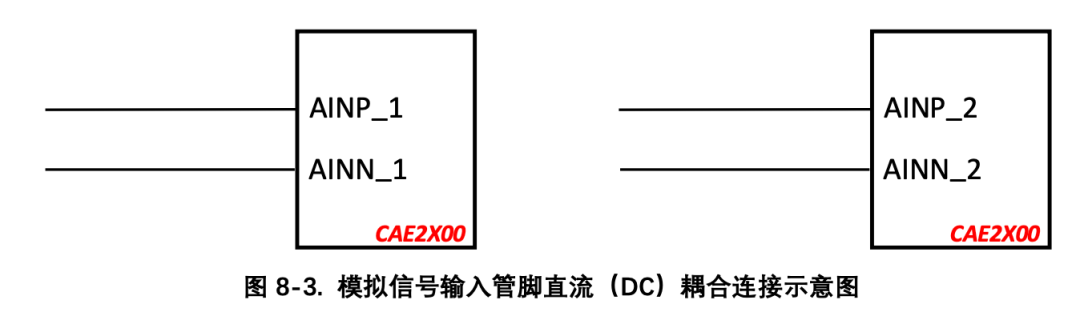

两组差分输入:AINP_1/AINN_1 和 AINP_2/AINN_2,每通道内部有 100 Ω 差分端接。

可以工作成:

单通道模式:等价于“一个 10.4 GSPS ADC”

双通道模式:等价于“两个 5.2 GSPS ADC”

内部标为 ADC-I / ADC-Q,既可以当 I/Q 两路 也可以当 CH1/CH2 使用。

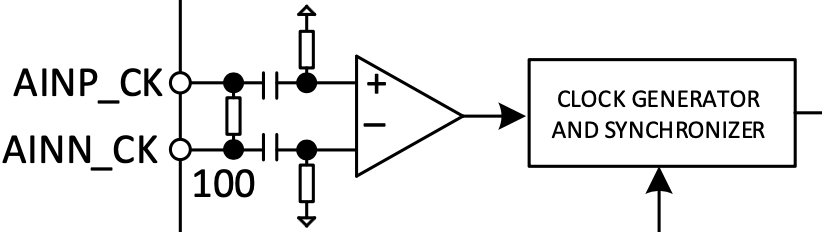

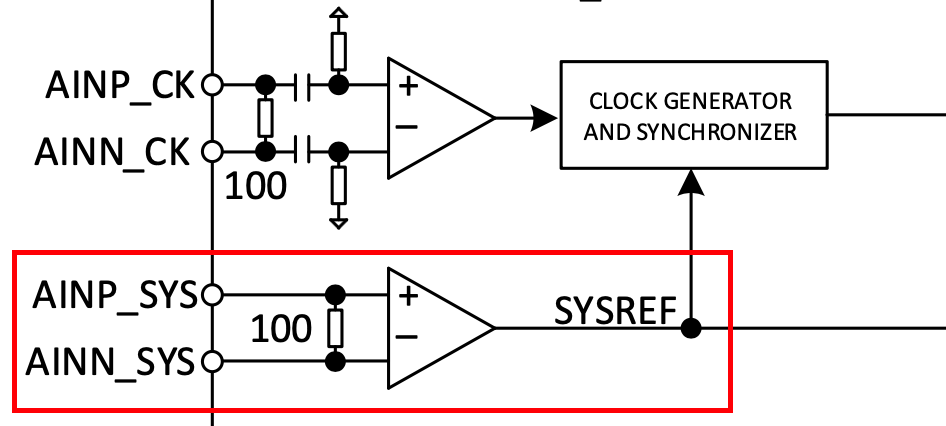

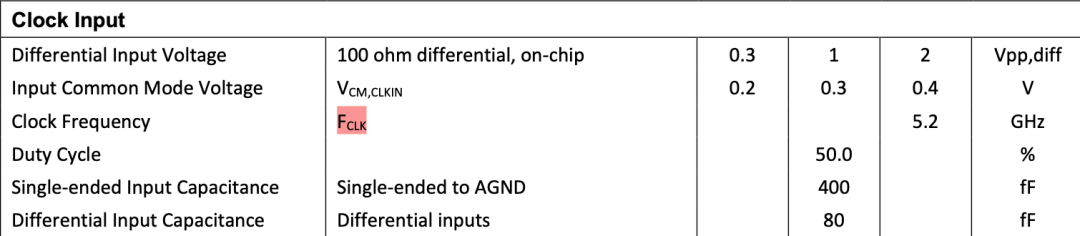

时钟与同步

AINP_CK/AINN_CK:主时钟差分输入,内置 100 Ω 端接,只支持 AC 耦合。

内部有 Clock Generator & Synchronizer:产生内部多相时钟,做通道间对齐/交织校准。

SYSREF(对应 AINP_SYSREF/AINN_SYSREF)+ SYNCB:构成 JESD204B Subclass-1 确定性延迟链路。

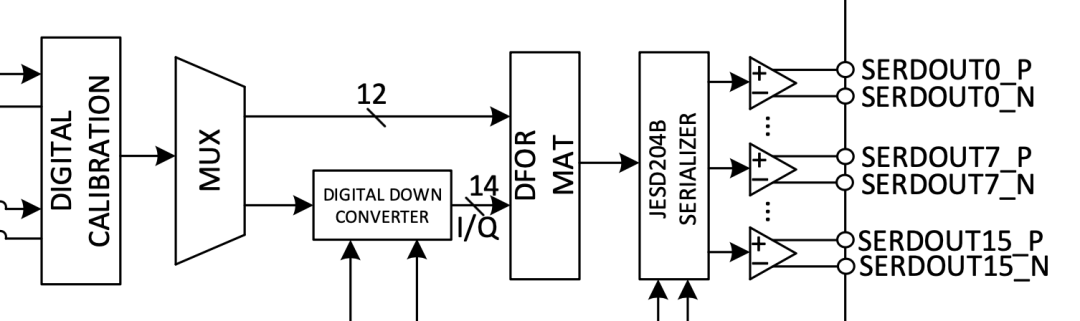

数字校准 + DDC(数字下变频器)

Digital Calibration:做增益、偏置、通道间/交织失配、自校准、后台 skew 校准等(配合 TSKEW_BG 管脚)。

DDC(Digital Down Converter):每个 DDC 有 4 个独立 NCO(48-bit),可做载波搬移 + 抽取滤波;支持很多抽取比(实数 1×–64×,复数 2×–128×)。

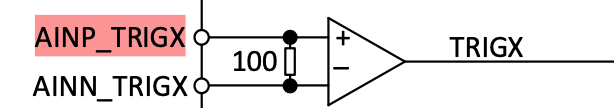

TRIGX 差分输入 + GPIO[4:0]:用来做 快速频率跳变 触发——非常典型的“扫频/跳频信号侦收”场景。

输出链路:JESD204B SerDes

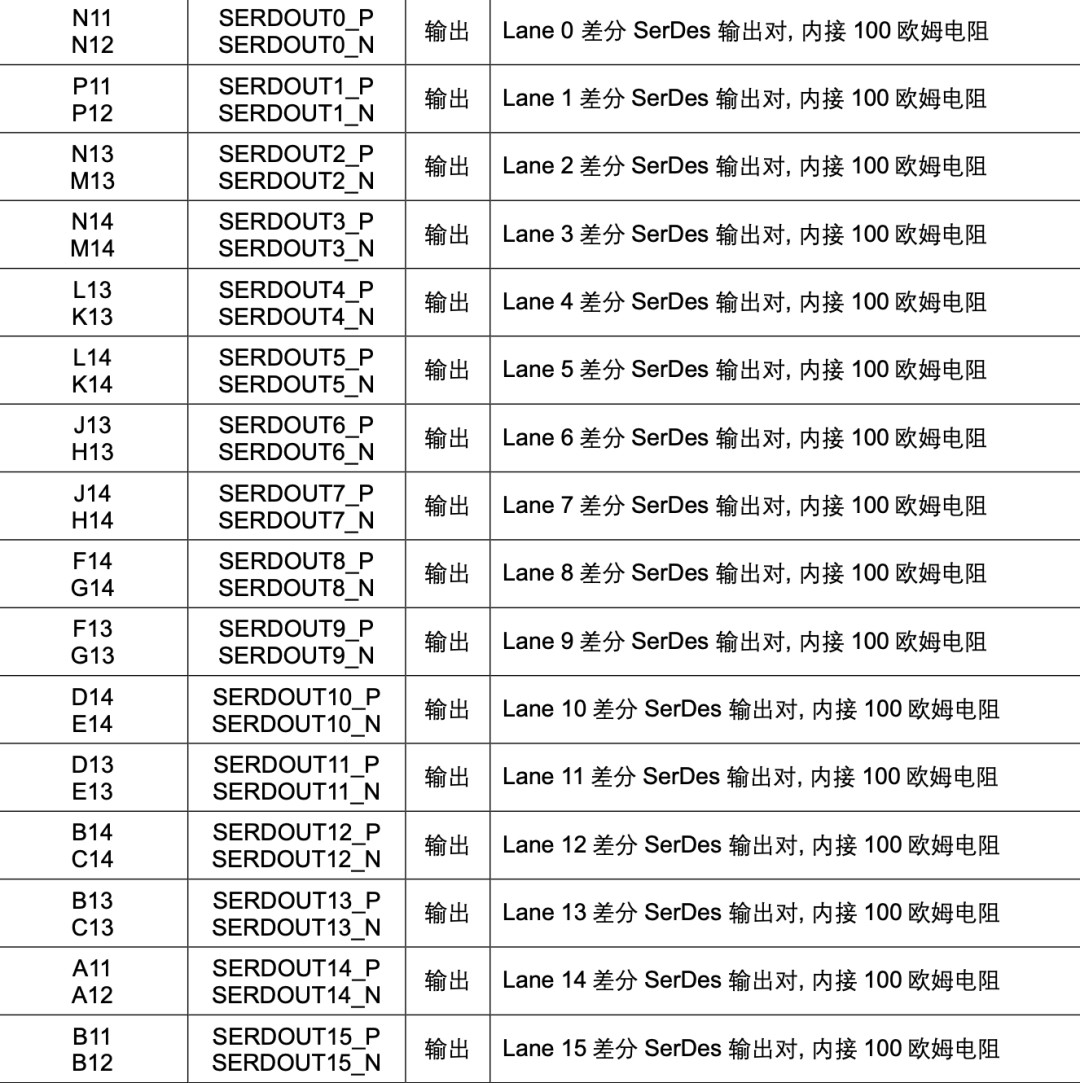

最多 16 个 lane:SERDOUT0/…/SERDOUT15,每 lane 差分 100 Ω 端接,输出摆幅约 0.5 Vpp,diff,AC 耦合;支持 JESD204B、8b/10b 编码,Subclass-1。

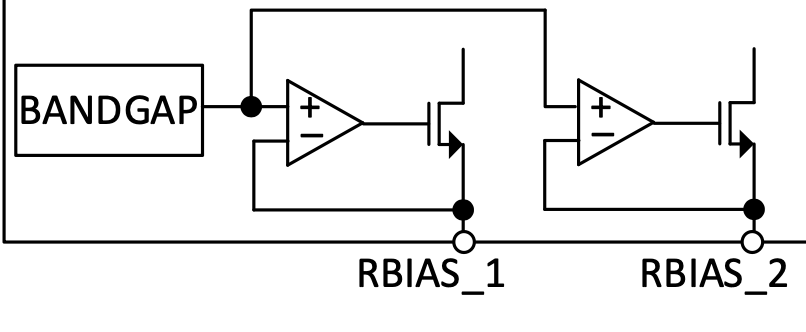

基准与偏置

RBIAS_0/1 外接 12 kΩ 精密电阻到地,用于设定内部模拟电路的参考电流。要求高精度、低温漂(建议 0.1%,25 ppm/°C);内部 bandgap 参考 产生 ±0.4 V 全差分参考,温漂在 ±50~±100 ppm/°C。

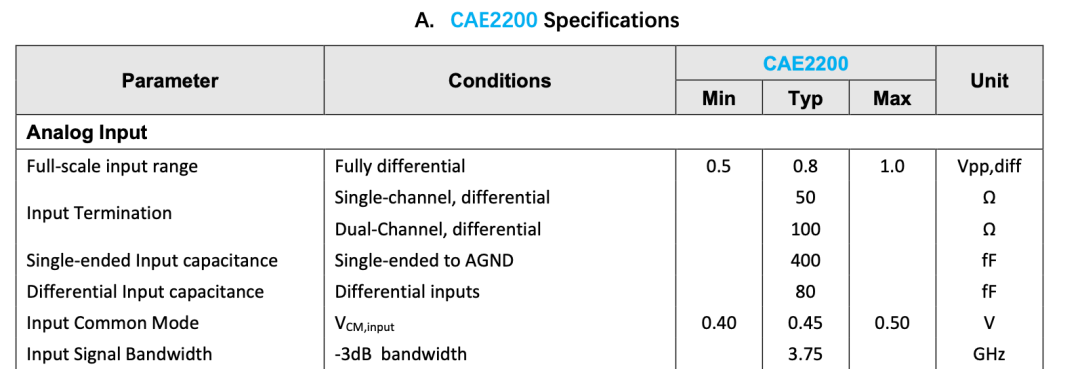

模拟输入:范围、耦合与 PCB

电气指标(以 CAE2200 为例)

全差分满量程:0.5–0.8–1.0 Vpp,diff(typ 0.8 Vpp,max 1 Vpp)。

输入共模:典型 0.45 V(0.40–0.50 V)。

-3 dB 带宽:3.75 GHz,典型 RF-sampling 级别。

端接:差分 100 Ω(相当于每线对地 50 Ω)。

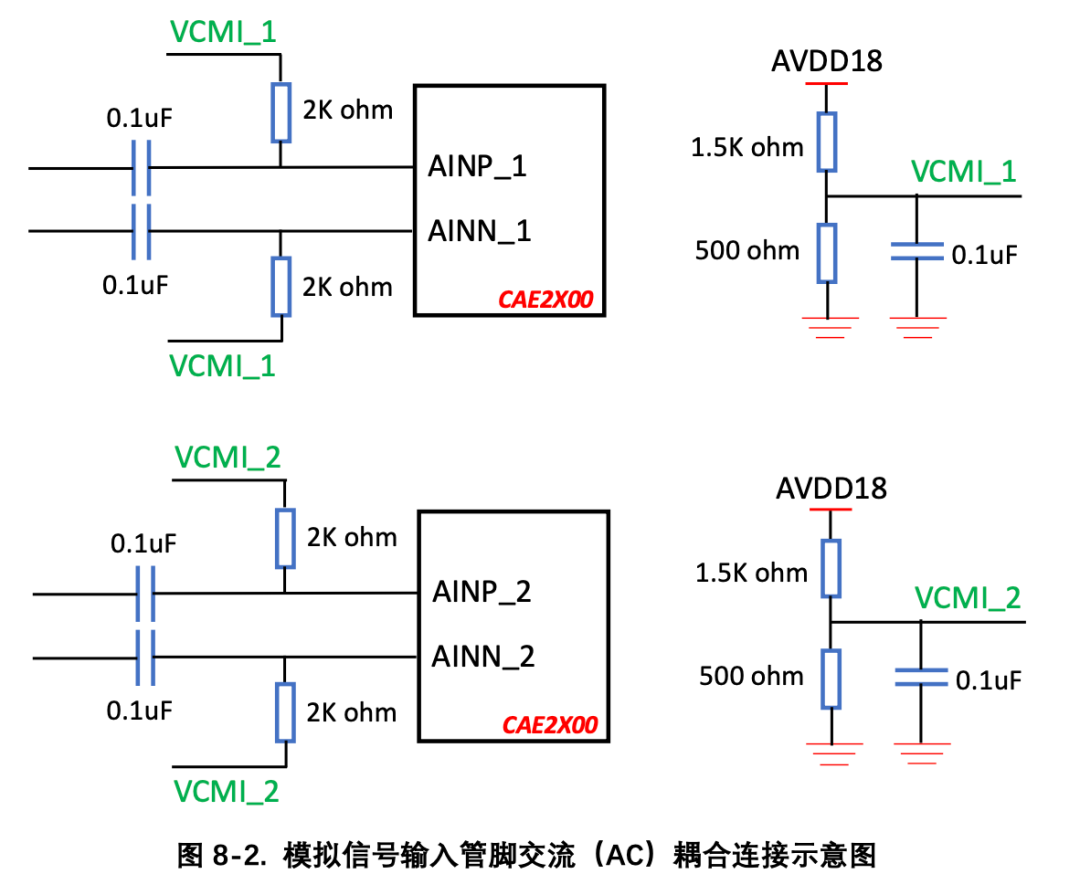

AC / DC 耦合

文档在“信号管脚连接说明”里给了很清晰的建议:

AC 耦合

模拟信号通过电容(如 0.1 µF)接到 AINP_x/AINN_x;芯片 不会自动提供输入共模,需要你用外部分压产生约 0.45 V 的 VCMI,通过 2 kΩ 电阻分别送入每个输入脚。(每个通道的 VCMI 必须 独立,不能两个通道共用,以免通道串扰。)

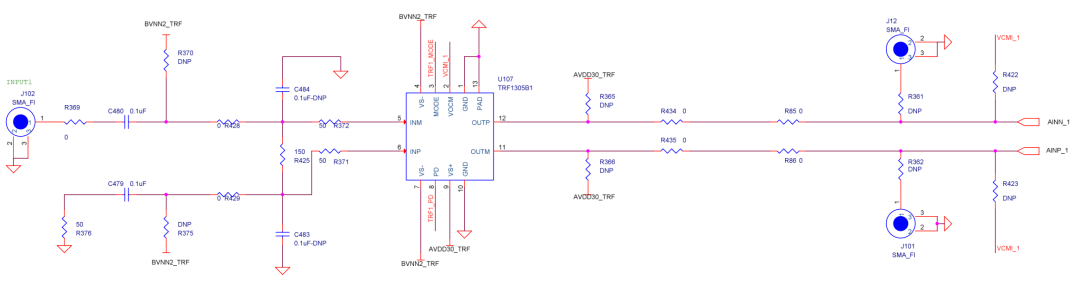

板子的原理图上面有这个

板子的原理图上面有这个

适合:前端为 50 Ω RF 源、滤波器、Balun 等,且想自己定义 DC 偏置。

DC 耦合

如果前级是差分运放等,可以直接直连到 AINP_x/AINN_x,前级输出的差分共模必须就是 0.45 V;适合:IF/Baseband 差分放大器直接推这颗 ADC。

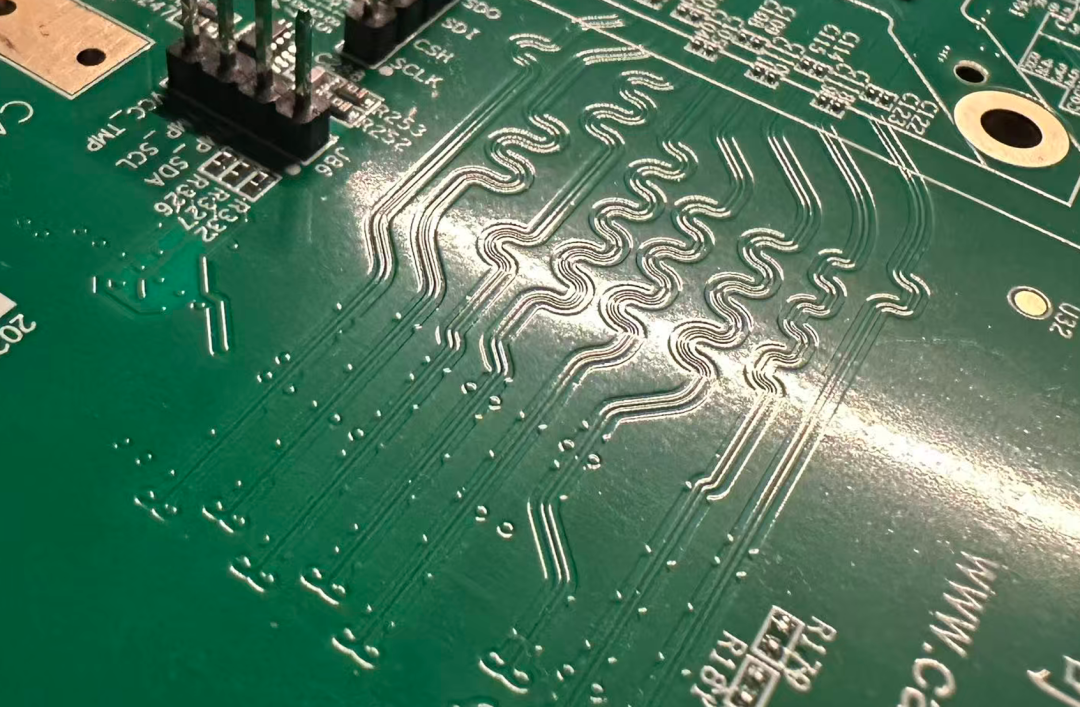

PCB 走线与板材

走线必须做 50 Ω 单端 /100 Ω 差分 阻抗控制;尽量避免 via;与其他高速/开关电源走线隔离。

整体看到都是蛇形走线

整体看到都是蛇形走线

用高速板材(Rogers RO4350B、松下 M6 等)减少损耗和失配。 (这个我就看不出来了是什么了);做高频射频前端(Balun + 滤波 + LNA),一般用 AC 耦合 + 外部 VCMI;如果做中低频宽带 IF 或直接采样基带,一般用 差分运放直推 + DC 耦合。

时钟、SYSREF 与触发

主时钟 AINP_CK / AINN_CK

只支持 AC 耦合,内部已有 100 Ω 端接;外部需要提供一个差分共模 VCM_CLK(典型通过电阻分压自 3.3 V 时钟电源产生),避免直接用 ADC 的 AVDD18,以减少时钟噪声耦合进模拟。

对 CAE2200:规格表写 FCLK = 5.2 GHz,而采样率是 10.4 GSPS;这意味着内部采用 2× 交织(比如上升/下降沿各采一拍),常见于 10 G 级别 ADC。

TRIGX & GPIO[4:0](快速跳频)

AINP_TRIGX/AINN_TRIGX 同样支持 AC/DC 耦合、100 Ω 端接、内部共模。

由 FPGA 输出差分触发脉冲(TRIGX),配合 GPIO 上的瞬时配置,让 DDC 内部 NCO 快速切换频点或模式。;工程上,相当于内置了一套“硬件级快速扫频/跳频 DDC”,不用每次靠 SPI 改寄存器。

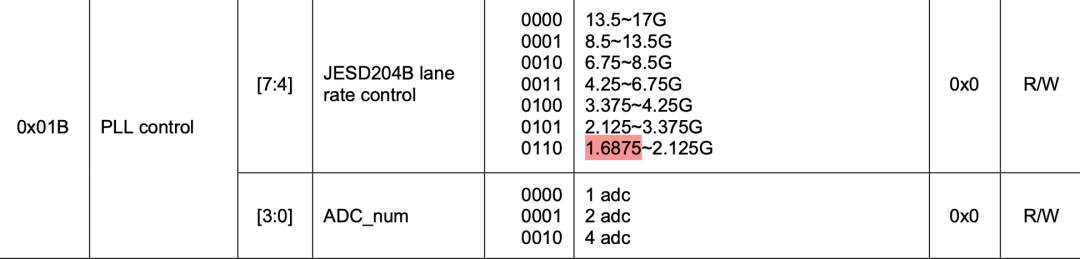

数字输出:JESD204B 细节

16 条数据输出,毕竟还是太恐怖了

16 条数据输出,毕竟还是太恐怖了

Lane 数:CAE2200支持 SerDes Lane rate和lane数如下表,16 条 SerDes 输出,每条为 SERDOUTx_P/N 差分对,内部 100 Ω 端接。

差分摆幅:约 0.45–0.50 Vpp,diff,AC 耦合到 FPGA。

Lane 速率:

规格表给出可配范围:1.6875–13 Gbps,一般 CAE2200 高速模式会跑到 ~12–13 Gbps,CAE2400 6lane最高跑到15Gbps。

协议:JESD204B,8b/10b 编码,Subclass-1(用 SYSREF + SYNCB 实现确定性延迟)。

对 FPGA 侧,可以按常见 JESD204B Rx 构建:

SYSREF → JESD204B core → lane 解码 → frame/alignment → 再把采样数据还原成 AXI-Stream / 并行总线。

核心性能( CAE2200)

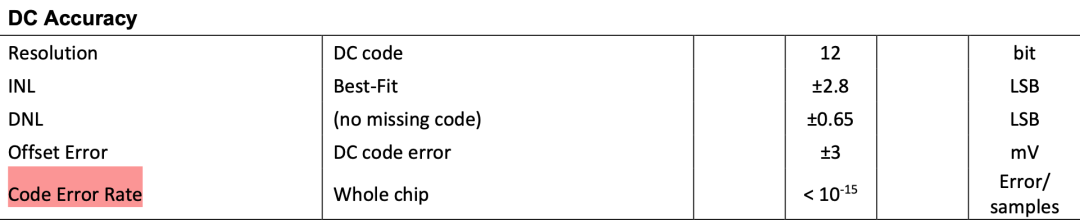

DC 指标

分辨率:12 bit,无失码(DNL 在 ±0.65 LSB 以内)。

INL:约 ±2.8 LSB(180 MHz 条件下)。

Offset Error:约 ±3 mV。

Code Error Rate:全芯片误码率 < 10⁻¹⁵ /Sample,说明长期跑不会随便跳码。

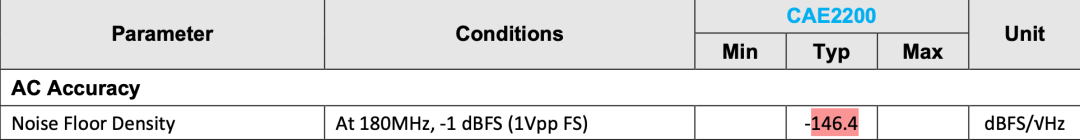

AC 指标(单通道 10.4 GSPS)

以数据手册表格和首页摘要为准:

SNR(1.09 GHz, -1 dBFS,1.0 Vpp):约 48.6 dBFS

SFDR(1.09 GHz, -1 dBFS,1.0 Vpp):约 67 dBFS

ENOB(1.09 GHz, -1 dBFS,1.0 Vpp):约 7.8 bit

噪声底密度:在 180 MHz、1 Vpp FS、-1 dBFS 下约 -146.4 dBFS/√Hz。

随着频率升高到 2–4 GHz,SNR 会从 ~49 dB 稍微掉到低 40 多 dB,ENOB 从 7.8 降到 6.9–7.2bit,典型的高频 RF-sampling 行为。

与 CAE2300/2400 的对比要点:

降速版本(8 GSPS/6 GSPS)在同频点通常会多 0.3–0.5 bit ENOB、1–2 dB SNR,这是因为对带宽/采样速度放松后更容易优化线性与噪声;功耗也更低(CAE2200 3 W,2300/2400 分别是 2.8/2.4 W)。

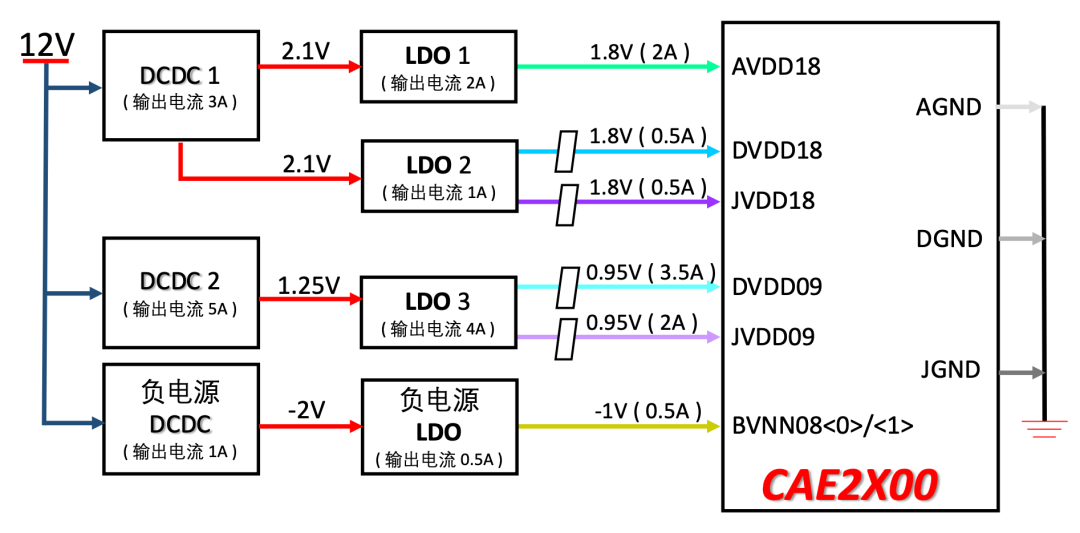

供电、功耗与温度

电源轨

这才算是电源轨是这个名词,大家各司其职

这才算是电源轨是这个名词,大家各司其职

+1.8 V:AVDD18、DVDD18、JVDD18(模拟、数字、JESD I/O)

+0.95 V:DVDD09、JVDD09(数字内核 + JESD 内核)

-1.0 V:BVNN08(模拟负电源,多个 pin)

电流 & 功耗(CAE2200)

典型工作(全部后台校准开、DDC 关):

1.8 V 轨:约 1250 mA

0.95 V 轨:约 780 mA

总功耗约 3 W。

掉电模式下电流大幅降低至几十 mA。

结合上面的特性,可以总结 CAE2200 最适合:

宽带示波与实时频谱分析:10.4 GSPS + 3.75 GHz 模拟带宽,做 4 GHz 以内的 RF 采样示波/频谱仪很合适;配合 DDC 可以在芯片里直接做下变频 + 抽取,降低 FPGA 负担。

宽带通信/雷达前端(直接 RF 采样或高 IF 采样):JESD204B Subclass-1,方便多通道 MIMO、波束成形、TDD 系统对齐;TRIGX + NCO 快速跳频,适合扫频/跳频雷达或电子对抗接收机。

测试仪器:信号分析仪、矢网前端、5G/802.11ad 测试、超宽带系统等。

如何在 2200/2300/2400 之间选:

需要最高瞬时带宽/最快时域分辨率 → CAE2200:对频率略低(比如 ≤3 GHz)但追求更好 SNR/ENOB + 低功耗 → CAE2300/2400。

另外多片并行堆通道数时,系统的散热能力也是一个重要考量:功率越低越容易做多通道。

工程使用要点

前端匹配

保证驱动源或放大器输出为 0.8–1 Vpp,diff,差分共模 0.45 V;PCB 按 50 Ω/100 Ω 阻抗控制,高速板材 + 减少 via;AC 耦合时记得给每通道单独的 VCMI。

时钟设计

5.2 GHz 差分时钟,低抖动时钟芯片 + 短线 + 独立 3.3 V 时钟电源;只 AC 耦合进 AINP_CK/AINN_CK,外部分压生成 VCM_CLK。

同步 & JESD

SYSREF 走 100 Ω 差分控制,来自支持 JESD SYSREF 的时钟芯片;用 SYNCB 做 lane 对齐握手,Subclass-1 确保多片 deterministic latency。

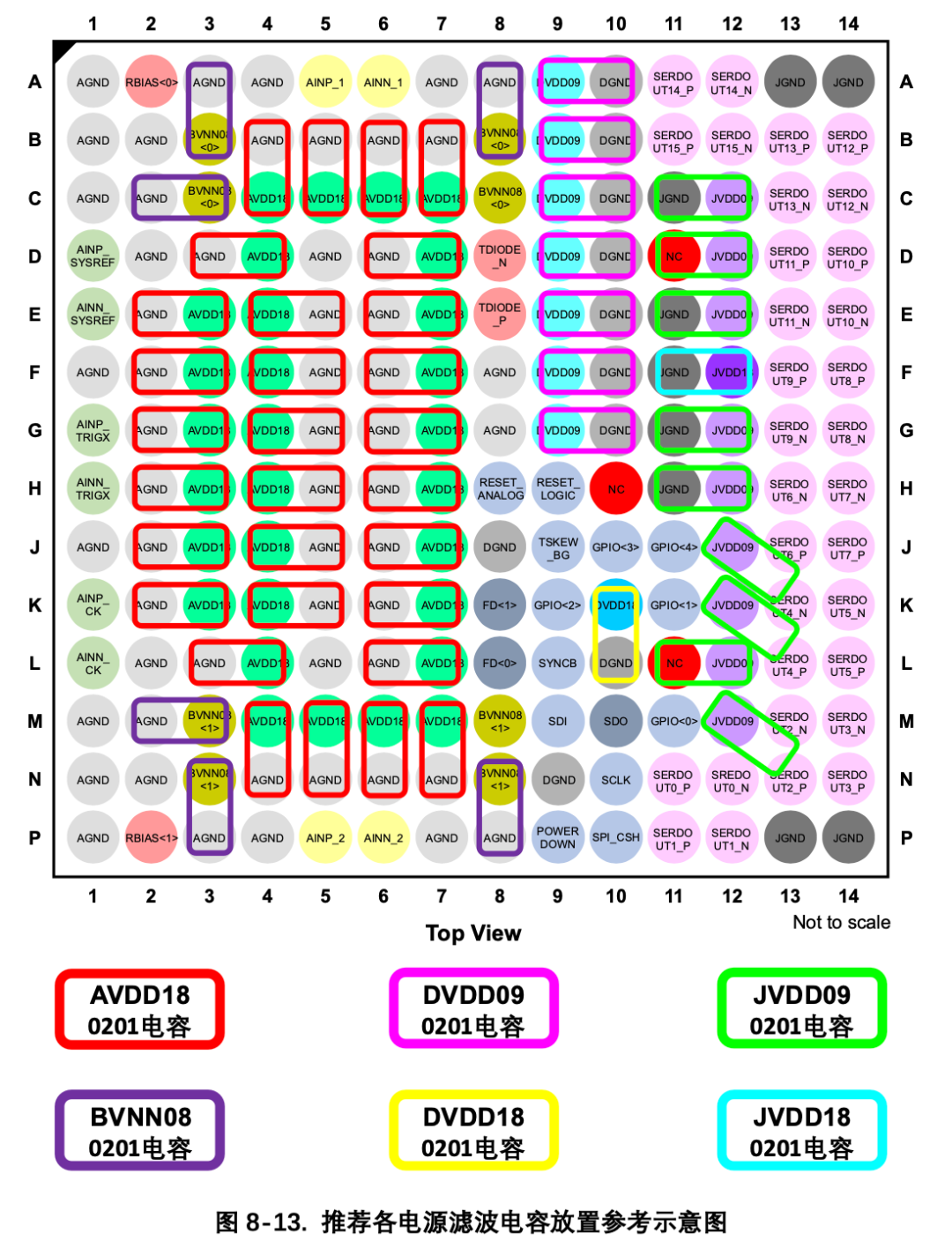

电源与去耦

只能说高速还是太讲究了

只能说高速还是太讲究了

1.8 V/0.95 V/-1.0 V 电源最好分 rail,用 LDO + 合理的 LC 滤波;按 8.4/8.5 节推荐在每个电源 pin 近端布 0.1 µF + 若干 µF 级电容,分模拟/数字/JESD 区域布局。

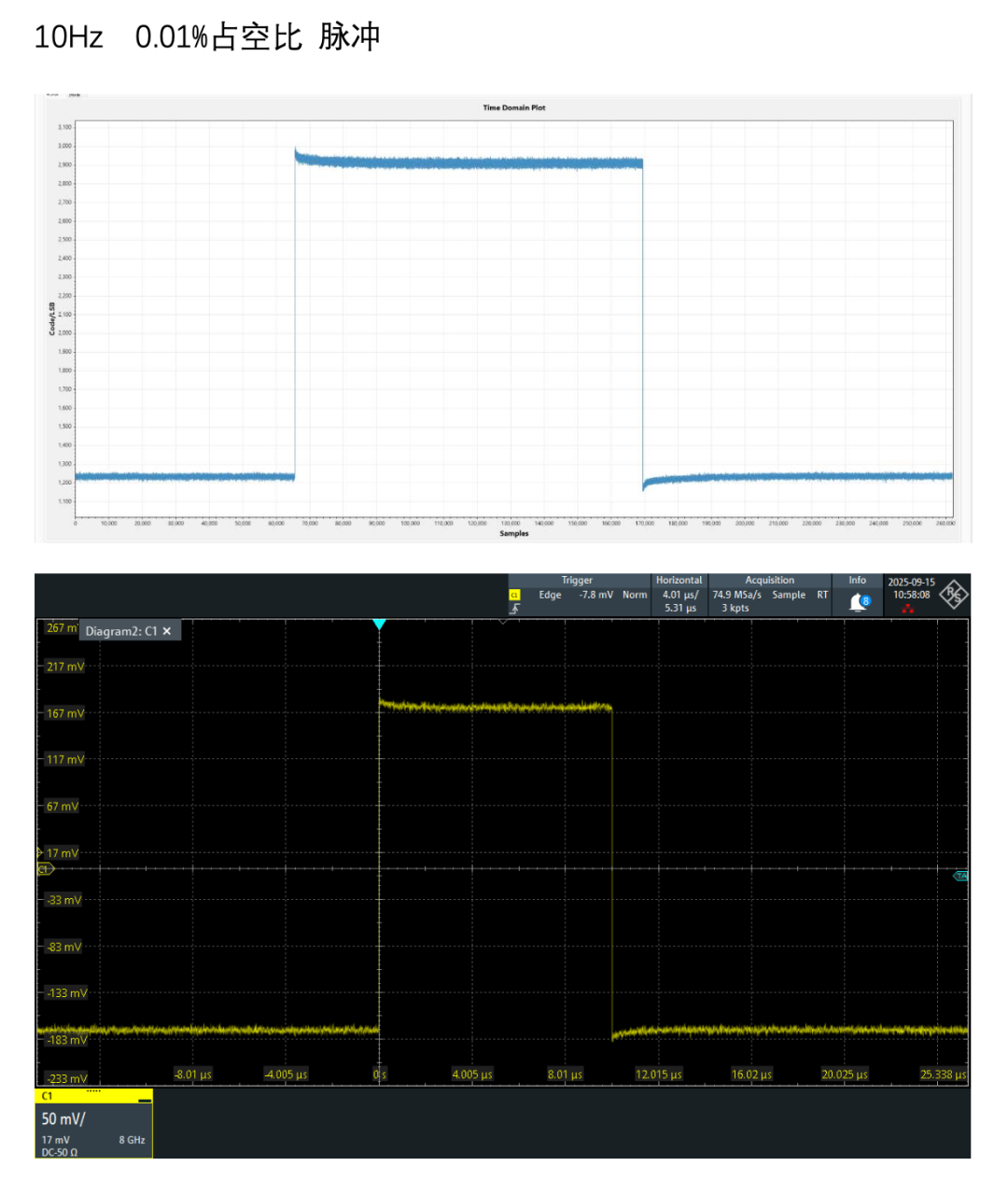

实测结果

因为需要很好的高速信号源来测试,我这边就拜托专门的实验室做了相关的测试,以时域为主。

那这一组实验整体在验证什么?

从 10 Hz 窄脉冲到 100 MHz 方波、再到几 MHz 锯齿波,其实在同时验证几件事情:

是否真·DC 耦合

超低频(10 Hz,0.01% 占空比)脉冲:看 100 ms 周期内高电平有没有“慢慢掉下去”(高通衰减 / 基线漂移)。

10 Hz,0.01% 占空比 脉冲(P1)

测试点:DC、低频、超窄脉冲。

示波器下图:看到 100 ms 周期,脉冲宽度大约几~几十 µs,高电平非常平,低电平也平,没有外围“慢慢爬回”的迹象。

ADC 上图:低电平一大段、窄脉冲、高电平保持一会儿再回到低电平;高/低平顶都很稳,没有“斜坡/指数衰减”。

前端 + ADC 链路是真正能看 DC 的:没有类似 AC 耦合 / 1 Hz 高通造成的基线恢复;长时间占空比极端不对称时,DC 分量仍然被保留。对做“慢信号示波 / 低频脉冲捕捉 / 电源波形”等很友好。

中高频带宽和上升沿能力

100 kHz → 1 MHz → 10 MHz → 100 MHz 方波:看边沿是否变“斜”“钝”“带大毛刺”。

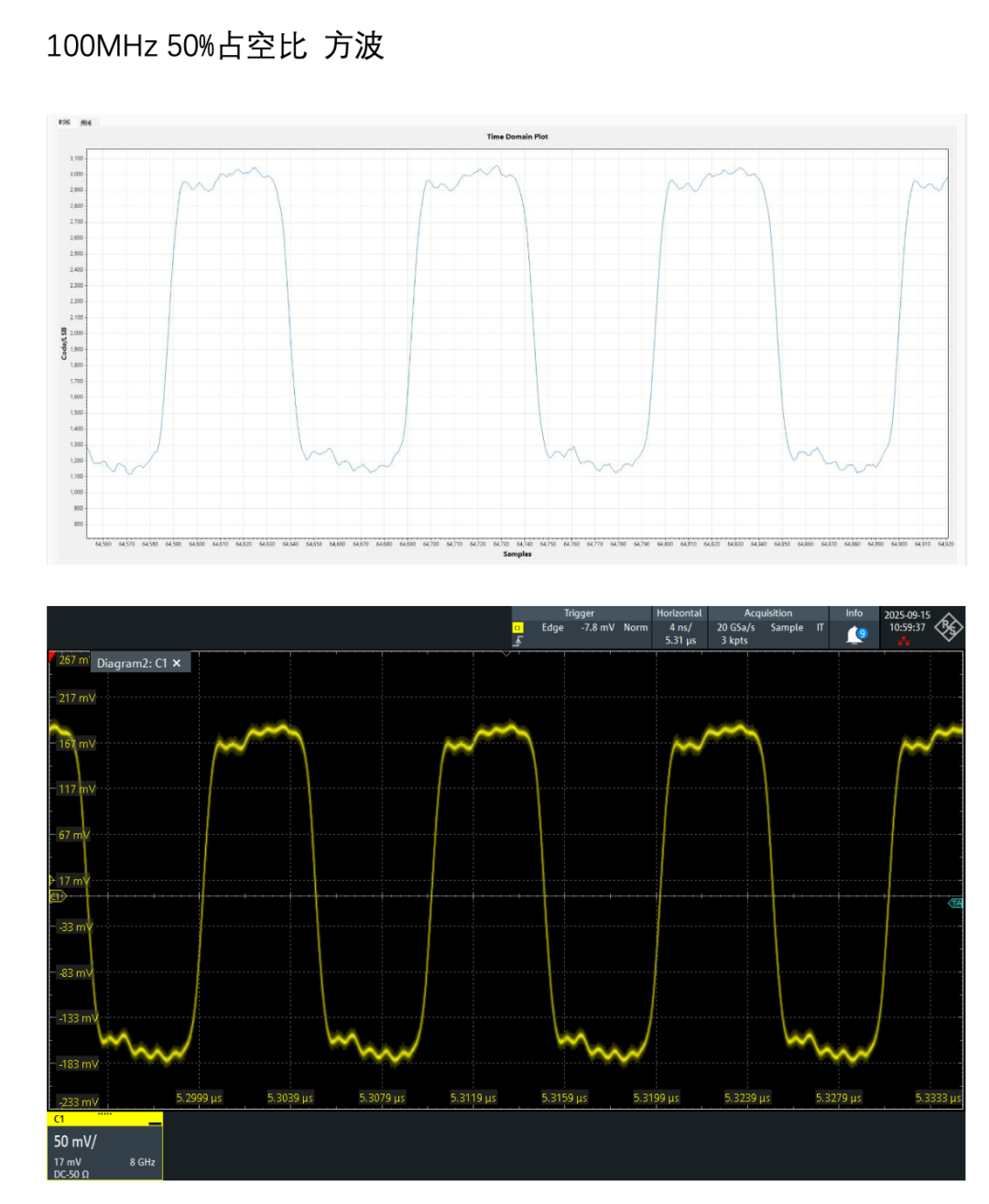

100 MHz 50% 方波

测试点:高频带宽、边沿保持情况。

示波器:上升沿、下降沿很快,有一点过冲和振铃(这是信号源+探头+带宽的综合效果)。

ADC:方波形状完整,有一点“圆角”,顶端略微轻微倾斜,这说明:高频谐波(> 几百 MHz)被 ADC 前端 + 布线 + 数字滤波平滑了一些;但基本波和前几个谐波仍被保留,所以宏观上还是方波。

100 MHz 方波的主要谱线在 f、3f、5f…,也就是 100、300、500 MHz……CAE2200 模拟带宽 3.75 GHz,ADC 本身完全能吃下这些谐波;现在看到的“圆角”,主要是 前端匹配 / 插值重建 / 示波器 vs ADC 的滤波特性不同,而不是 ADC“带宽不够”。

边沿在 ADC 波形里仍然相当陡,和示波器形状接近,说明 前端带宽和采样率足以保留到 100 MHz 的方波尖锐度(对 CAE2200 这种 RF-ADC 来说,这是轻松的)。

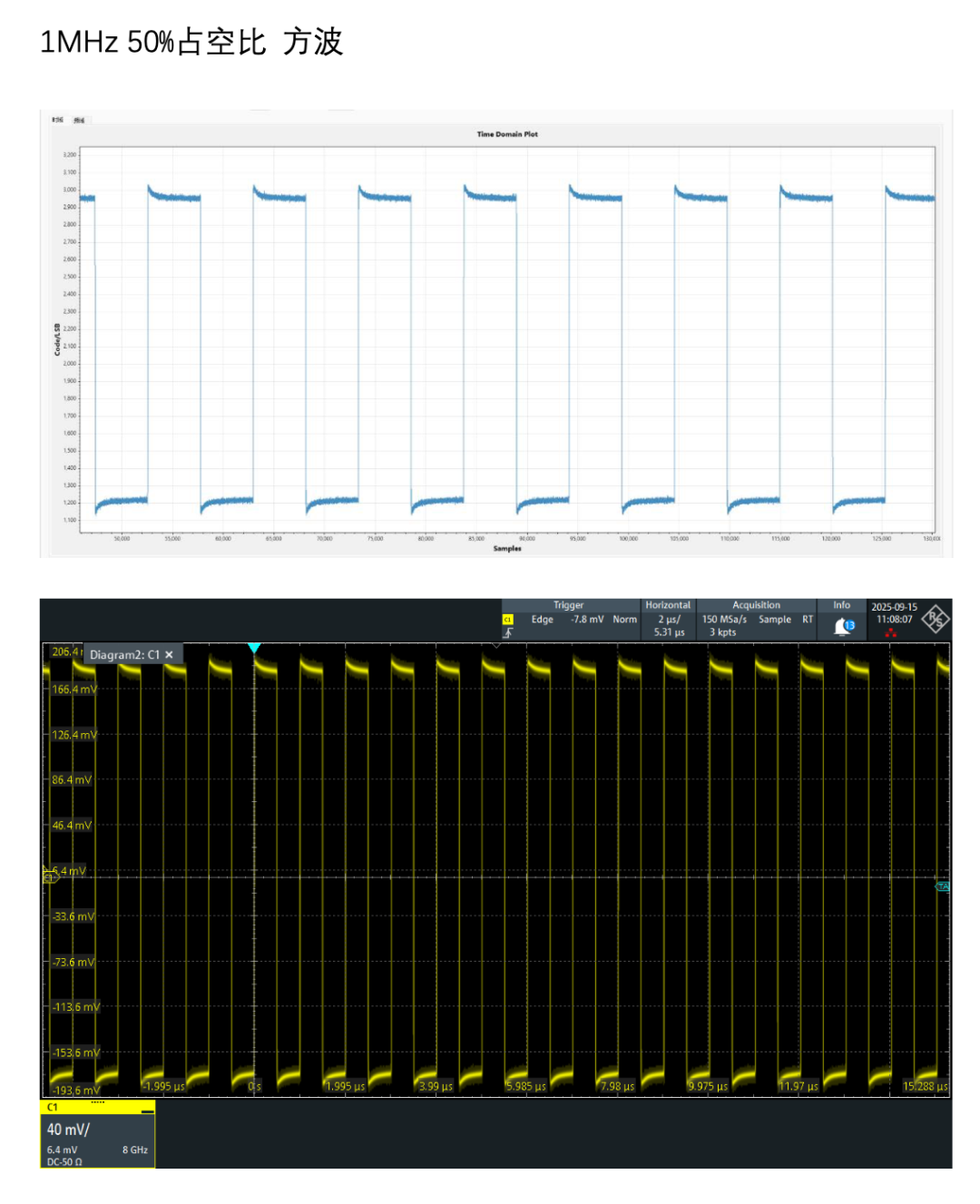

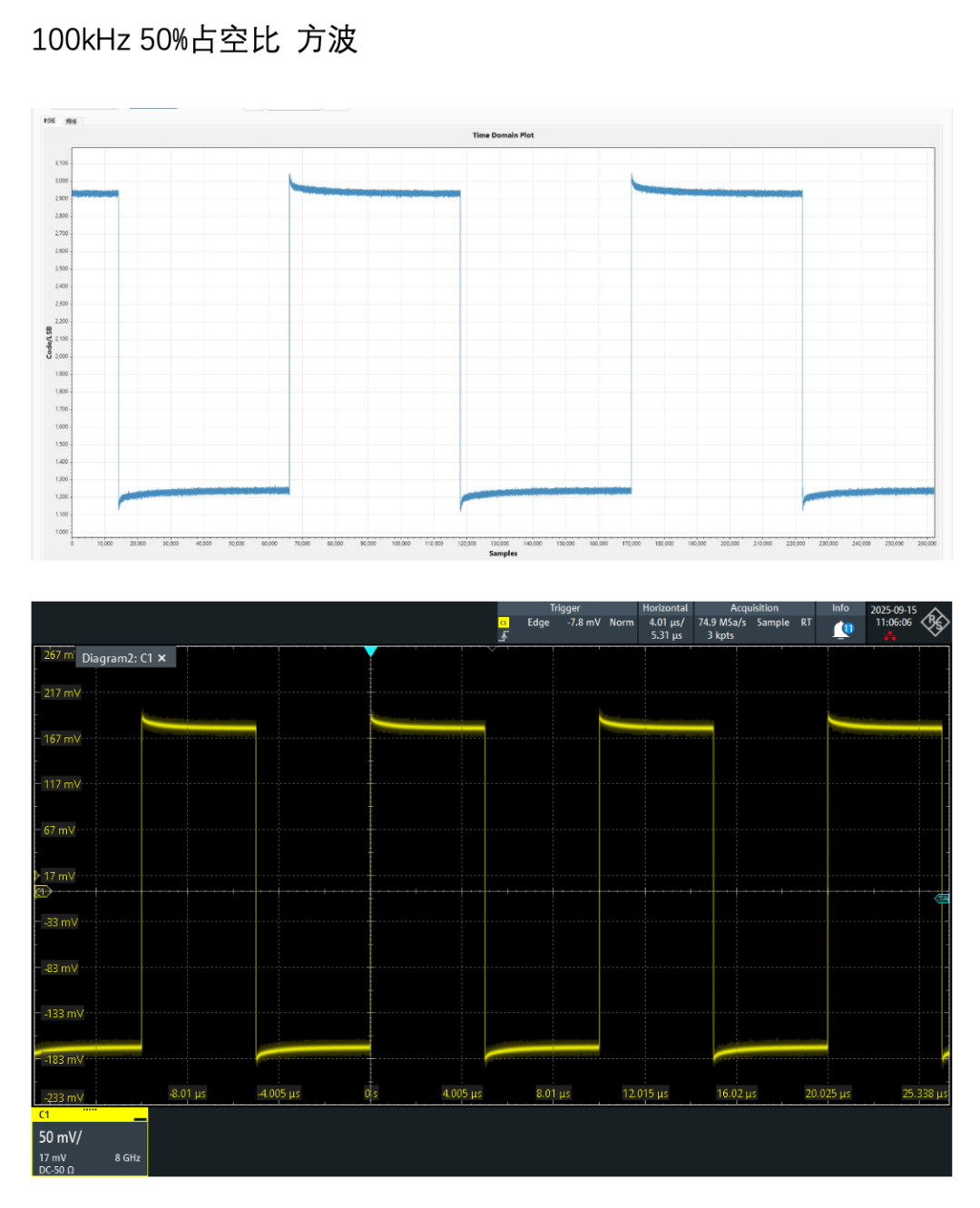

10 MHz / 1 MHz / 100 kHz 方波

测试点:中频方波的还原性和上升沿的一致性。

10 MHz 方波:ADC 和示波器波形几乎一模一样。

1 MHz 方波:高、低电平平台相当长,几乎看不到任何倾斜或 droop。

100 kHz 方波:更“教科书”,ADC 波形的方形非常规整。

在 100 kHz–10 MHz 范围,你的系统可以当作“理想示波器 + 很好的直流精度”:边沿跟得上,平台不倾斜;没有明显过冲 / 振铃;说明前端的 RC 匹配 + 布线质量不错。从时域角度看,中频下 THD/IMD 的时域痕迹很小(若有严重非线性,方波顶会有弯曲/肩)

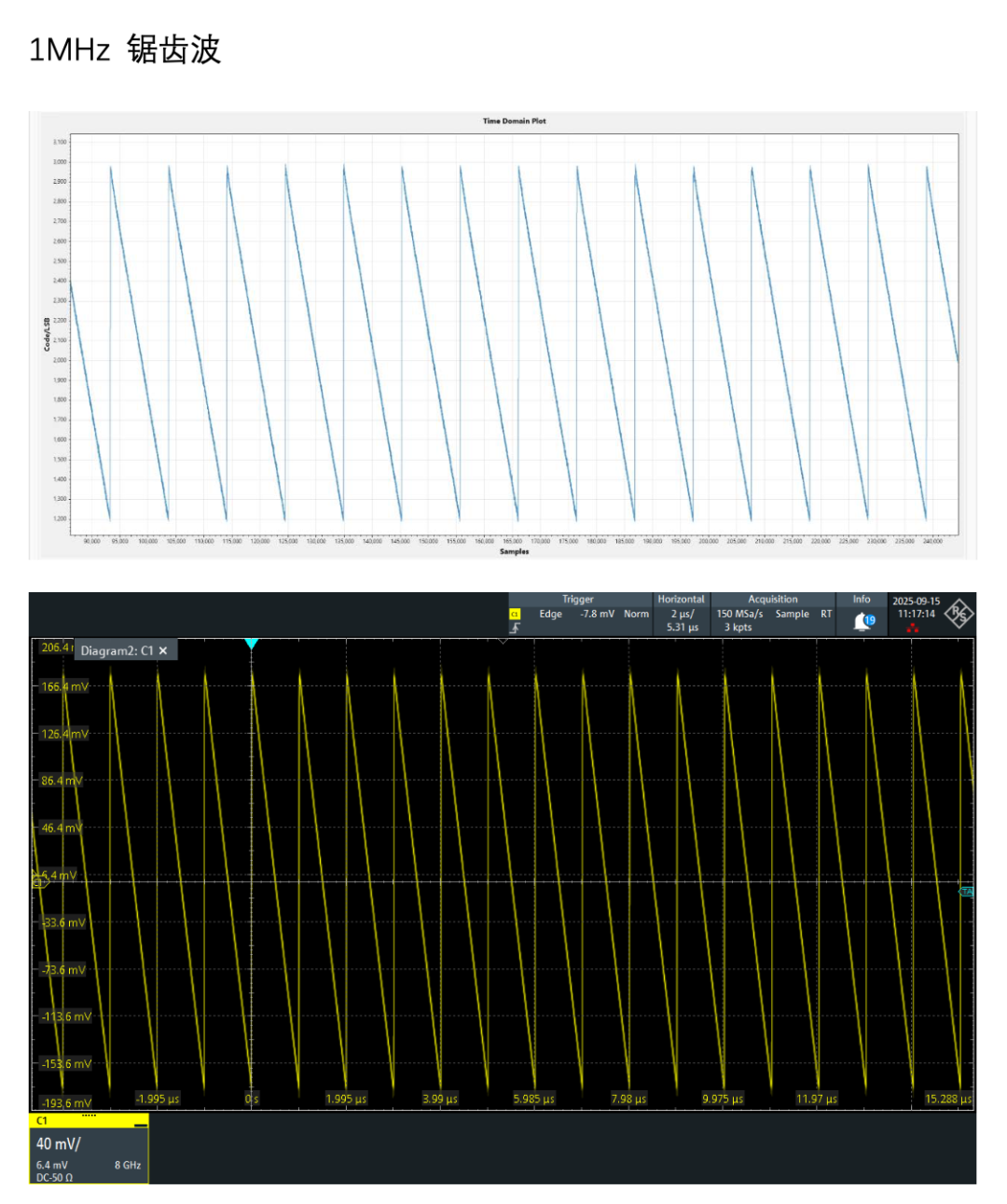

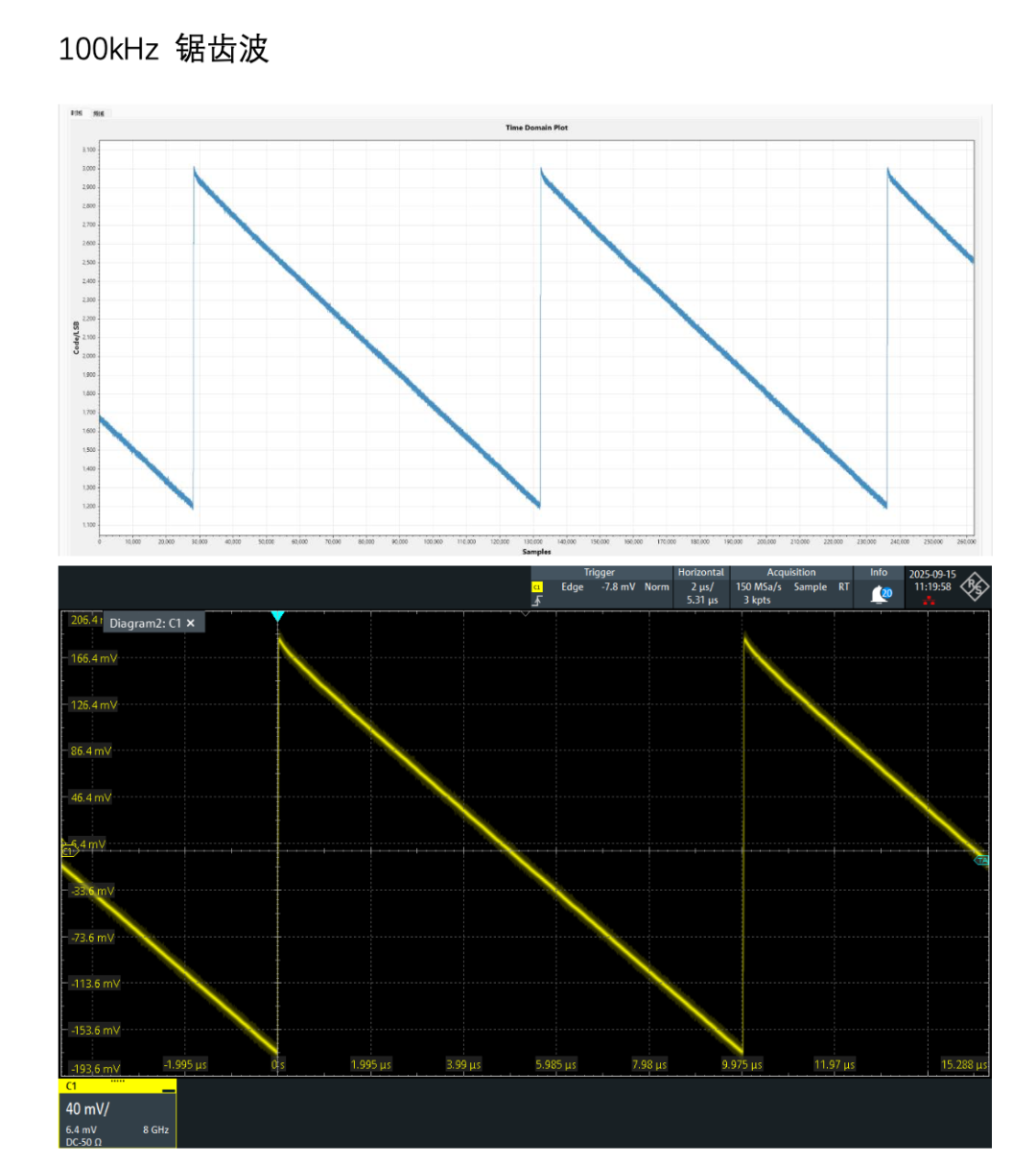

1 MHz / 100 kHz 锯齿波

测试点:大信号线性度、长斜坡线性、回零行为。

示波器:斜坡非常直,回跳沿很陡。

ADC:上升(或下降)沿的斜率几乎是恒定直线,整体斜坡很笔直;回零瞬间,能看到一个很窄的“尖/拐”,对应 saw 的“快速回扫”。

说明什么:

线性度好如果 INL 大,斜坡上会看到明显弯曲(比如接近满量程处“拉平”);现在直线很好,说明至少在设置的幅度范围内,大信号 INL 抑制得不错。

也能看到无显著带内压缩 / 偏置漂移因为多周期连续斜坡顶端落在同样位置,说明没有慢性的偏移累积。

这组实验 “能证明” 和 “不能证明” 的东西

能证明的(从时域直观结论)

DC–100 MHz 以内的时域波形保真度很不错,不管是方波还是锯齿,形状与 8 GHz 实时示波器差异很小。DC 耦合是真实有效的,超低频极端占空比脉冲,没有看到基线恢复和严重 droop。

前端线性度与动态范围在时域上表现良好

锯齿扫描整个输出范围,未见明显压缩/折线;输入匹配/布线总体良好,没有特别夸张的振铃;方波边沿干净,说明反射和包络不严重。

暂时还没证明的(需要频域/统计测试)

SNR / ENOB / SFDR 等频域指标,要做正弦波 FFT、扫频幅度曲线才能定量评价。

抖动、相位噪声需要看频谱上边带、时域上零交叉抖动统计。

从“做仪器”的角度,这组结果说明什么?

如果想把 CAE2200 当成“实验室级通用采集机/示波器内核”来说,这组图非常有说服力:

DC 到至少 100 MHz 的波形形状,已经和高端示波器相当接近;DC 耦合、低频、极端占空比都工作正常,可以安心做慢速测量、单次捕获;锯齿 + 方波都直观展示了不错的线性和动态范围。

简单说:

在时域观察层面,CAE2200 + 这条前端/板子,是可以扛起“实验室测量仪器级别”的;真正要分出“示波器 vs 仪器级频谱分析/精密测量”的区别,下一步要看频域 SNR / SFDR / 噪声底。

另外高速的确实是不好测量:

R&S®RTP 示波器

R&S®RTP 示波器

那 RS 的示波器肯定是首选:

因为真的在工作

因为真的在工作

后记

很高兴看到国内陆续有厂家勇攀高峰拿出各种重量级的东西,祝大家越来越好!

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2025-12-16,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录