Chiplet通信桥接技术介绍及大厂方案分析(二)

上一篇介绍了Chiplet设计和异构集成封装的技术分类和实现手段,这一篇来看下大厂的chiplet方案。

5.5 Intel的嵌入式多芯片互连桥(EMIB)

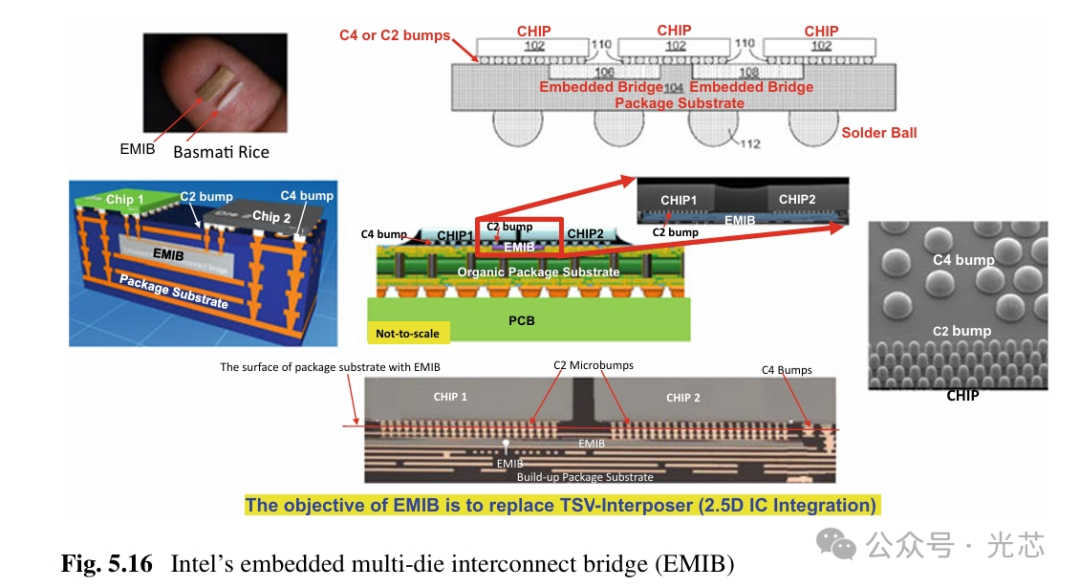

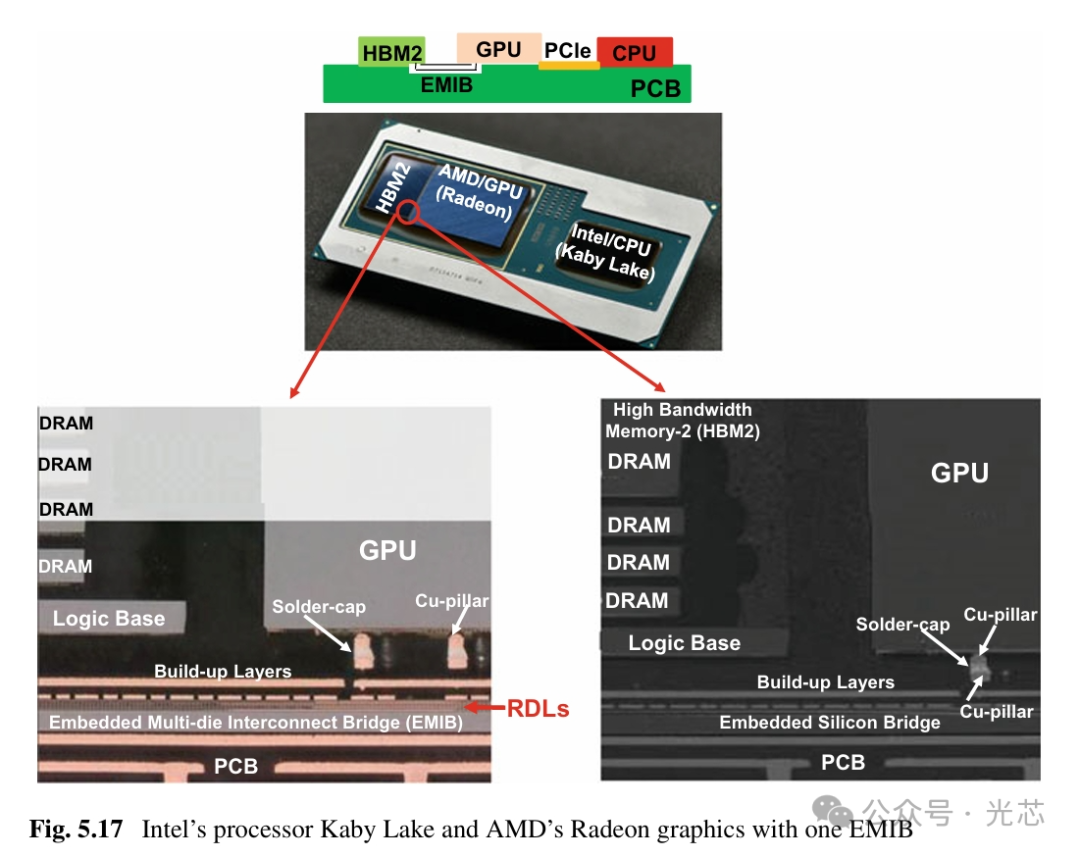

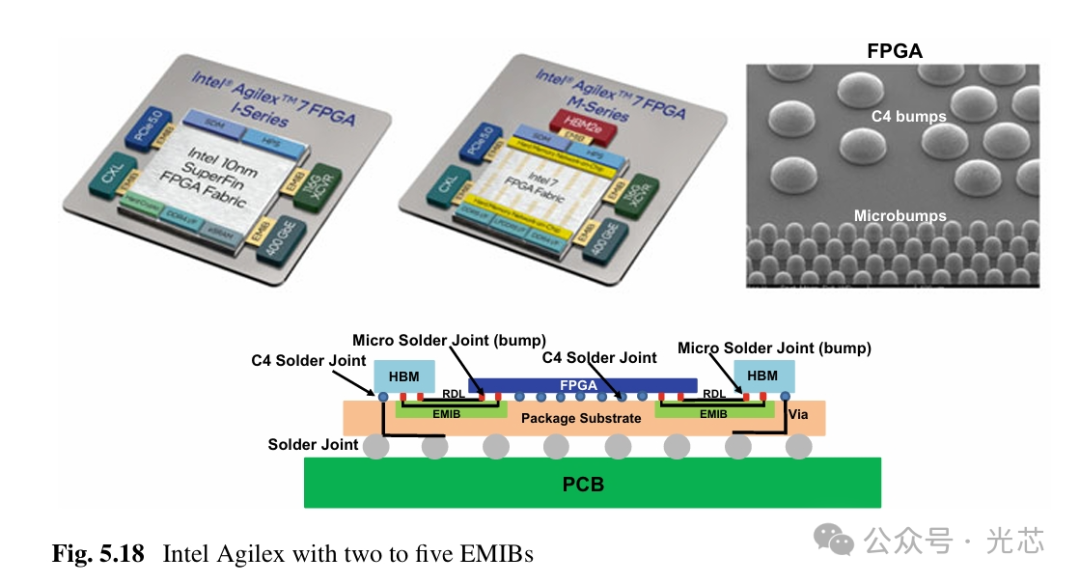

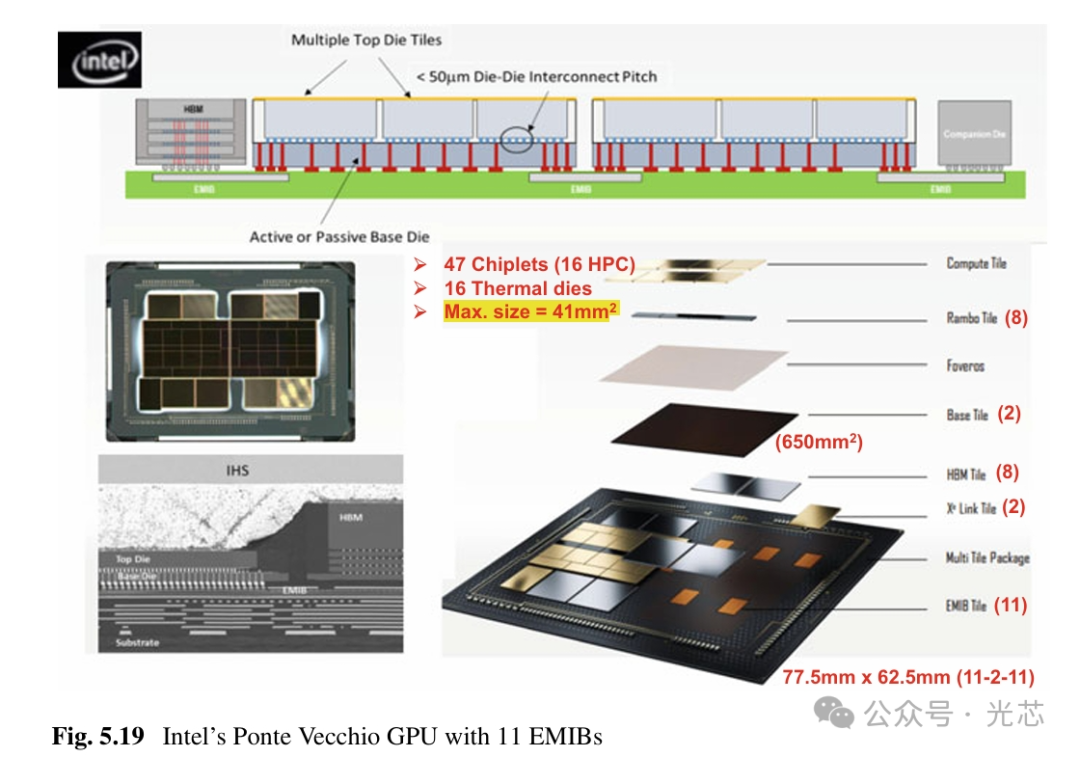

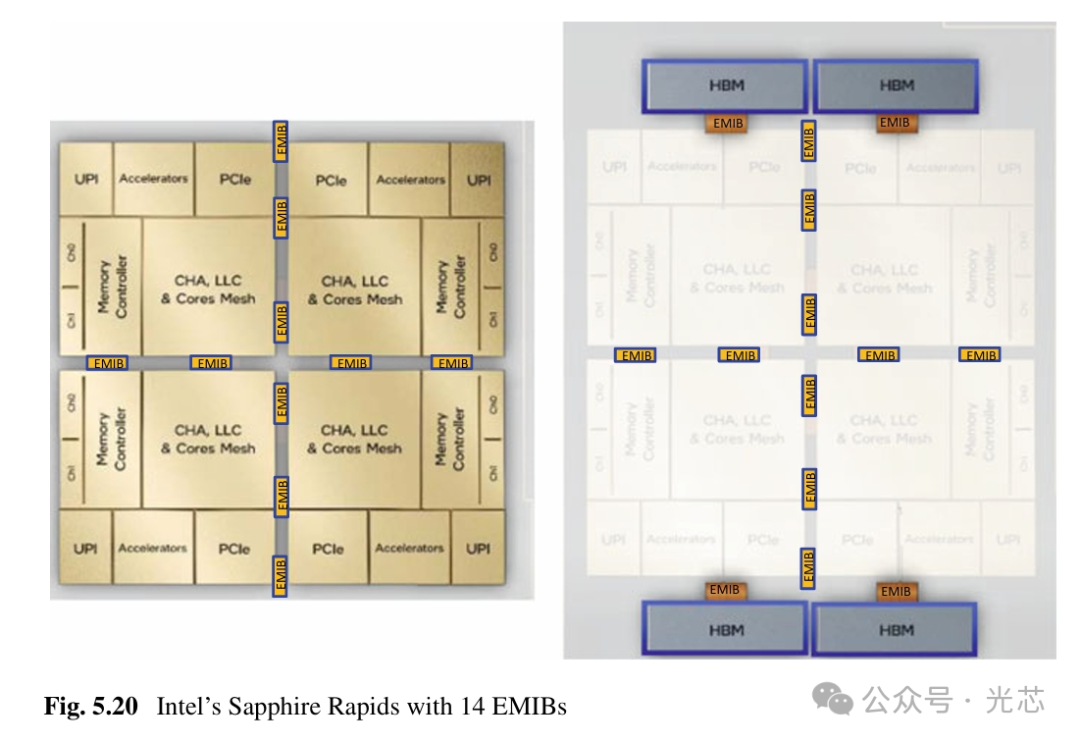

最著名的刚性桥互连方案是Intel的嵌入式多芯片互连桥(EMIB)方案。图5.16显示了Intel的EMIB专利之一。可以看出,EMIB芯片嵌入在积层build-up封装基板的腔中。图5.17显示了Intel 2017年的处理器(Kaby Lake),它使用Intel自己的EMIB以及HBM,将高性能×86核心与AMD的Radeon Graphics集成到同一处理器封装中。Intel在2019年10月停产了所有Kaby Lake-G产品。从2019年起,Intel一直在发货新的带有2到5个EMIB的Agilex芯片(图5.18),22年开始发货带有11个EMIB的Ponte Vecchio GPU(图5.19)。而到了Intel的下一代Xeon可扩展处理器Sapphire Rapids(图5.20),则由4个SoC组成,通过10个EMIBs连接,还有另外4个EMIBs连接4个SoC和4个HBMs。最近,Intel一直在讨论将SoC的数量减少到2个,并推出产品的新迭代。

EMIB的三大难点(图5.16),即:

(1)在chiplet晶圆上进行两种不同类型的焊点(桥上无焊料凸点);

(2)将桥接结构嵌入封装基板的腔中,然后对基板的顶表面进行层压laminating;

(3)将chiplet与嵌入桥的基板进行bonding。

5.5.1 EMIB的solder bump

从图5.16中可以看出,芯片上有两类焊点,即C4 bump和C2 bump,这个工艺其实是有难度的,但Intel已经解决了这个问题。

5.5.2 制造EMIB基板

制造带有EMIB的有机封装基板有两个主要工作(图5.16)。一个是制作EMIB,另一个是制作带有EMIB的基板。要制造EMIB,首先必须在Si晶圆上构建RDLs(包括接触焊盘)。制作RDL的方法取决于RDL的导线线宽/间距。最后,将非RDL侧的Si晶圆附着到芯片附着膜上,然后切割Si晶圆。

要制造带有EMIB的基板,首先将分割的EMIB与芯片附着膜一起放在基板腔中的Cu箔上。接着在整个有机封装基板上层压一层介电膜。然后,通过介质薄膜钻孔和Cu电镀以填充通孔连接到EMIB的接触焊盘PAD。随后继续进行Cu电镀以制作基板的横向连接,并在整个基板上再层压一层介电膜,接着钻孔和Cu电镀以填充孔并制作接触焊盘。较小线宽和间距的焊盘用于C2焊点,而较大线宽和间距的PAD则用于C4焊点。

目前能实现的最小的金属L/S/H一般是2/2/2um,桥的大小从2×2 mm到8×8mm,但大多数不大于<5×5mm。介电层厚度为2微米。通常有不多于4层的RDLs。EMIB技术的挑战之一是制造带有硅桥腔的有机积层封装基板,然后通过层压(用压力和温度)在顶部另一层build-up层以满足基板表面平整度要求,以便具有C2和C4 bump的芯片bonding。

5.6 IBM的直接键合异构集成(DBHi)

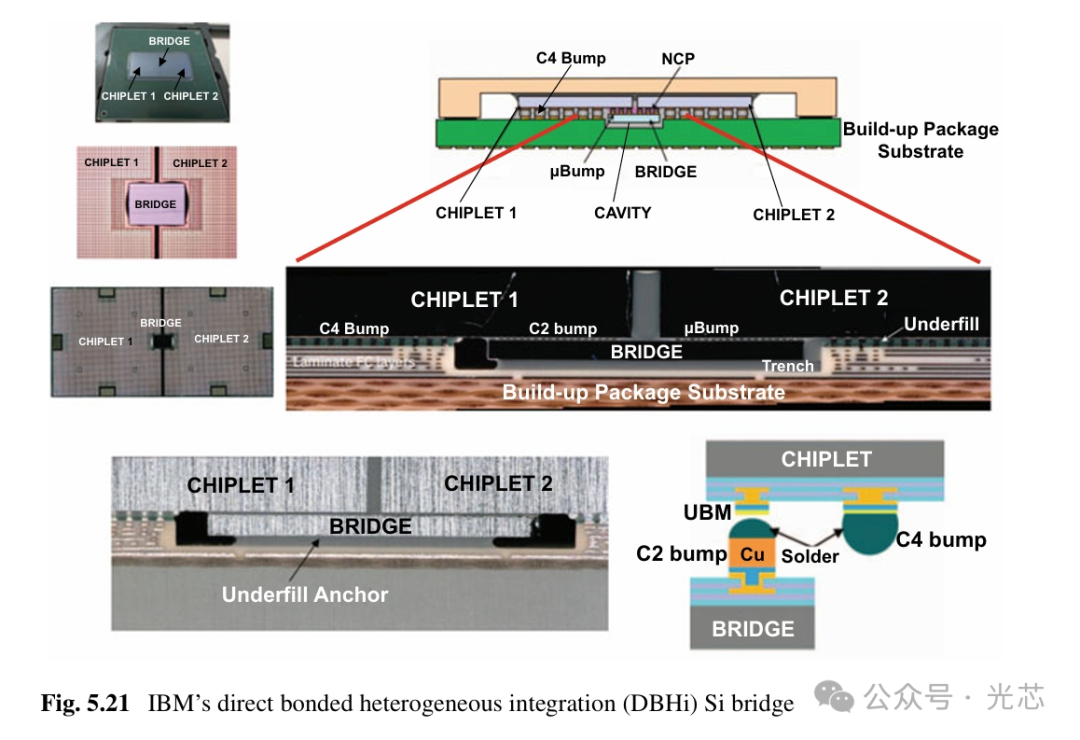

在IEEE/ECTC 2021和2022期间,IBM发表了7篇关于“直接键合异构集成(DBHi)硅桥接”(图5.21)的论文。Intel的EMIB和IBM的DBHi之间的主要区别如下:

(a)对于Intel的EMIB,芯片上有两类不同的焊点(C4和C2)(桥上没有焊点)(图5.16),而对于IBM的DBHi,芯片上有C4 bump,桥上有C2 bump(图5.21)。

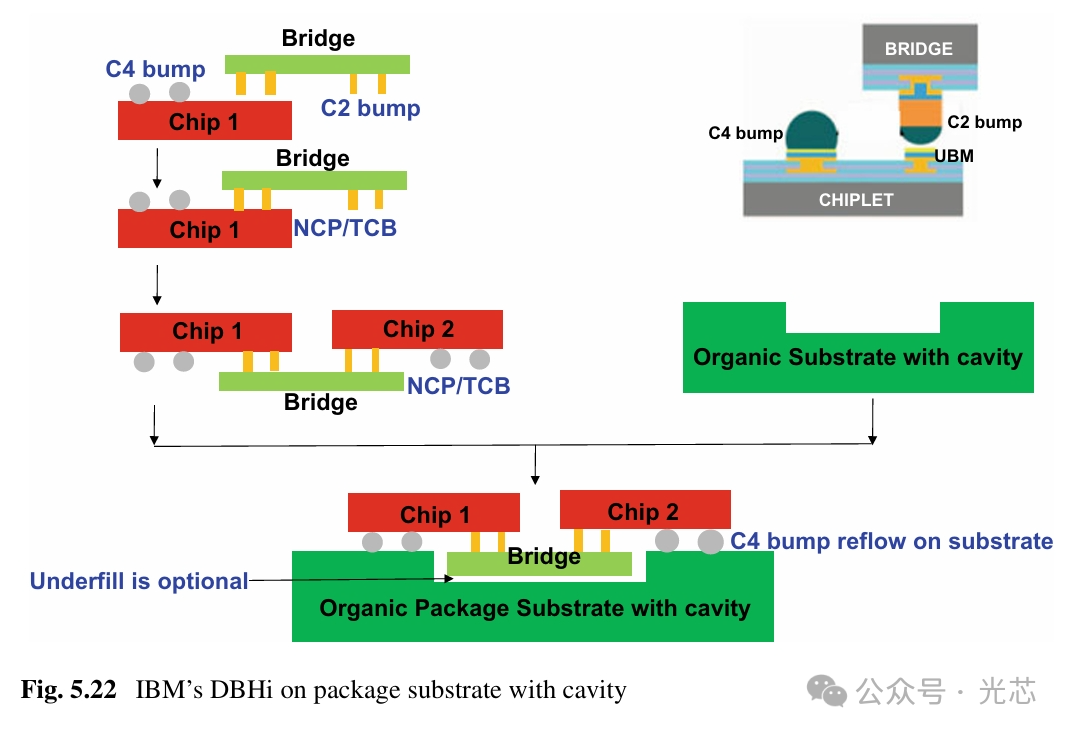

(b)对于Intel的EMIB,桥接结构用芯片粘接材料嵌入到积层基板的腔中,然后在上面层压另一build-up层。因此,基板制造非常复杂。对于IBM的DBHi,基板只是一个带有顶部腔结构的常规基板,如图5.22所示。

DBHi的键合组装过程非常简单(图5.22)。首先,使用非导电浆料(NCP)和热压缩键合(TCB)将芯片1和桥bonding。然后,使用NCP和TCB将芯片2和桥键合。这些步骤之后,将模块(芯片1+桥+芯片2)放在带有腔结构的有机基板上,然后进行标准的倒装焊reflow组装过程。桥下的填充是可选的。图5.21展示了IBM的DBHi实物图。

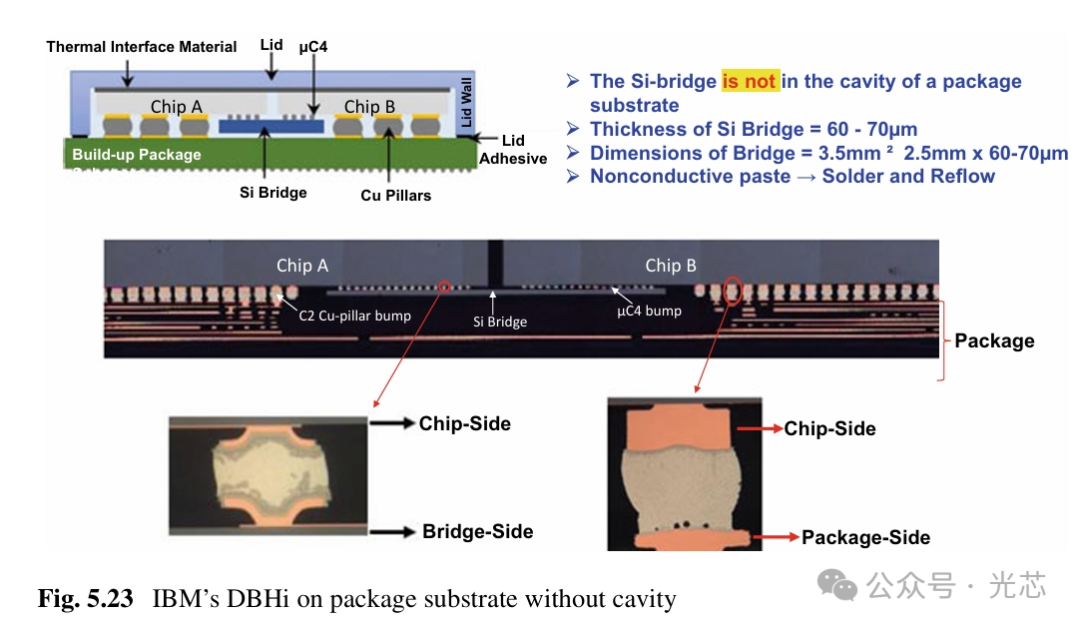

在IEEE/ECTC 2023期间,IBM发表了一篇关于“直接键合异构集成(DBHi):用于芯片拼贴的表面桥技术”(英文标题是Surface bridge approach for die tiling)的论文。作者提出对于他们的Si桥技术来说甚至可以不需要在基板上加工腔结构,如图5.23所示。

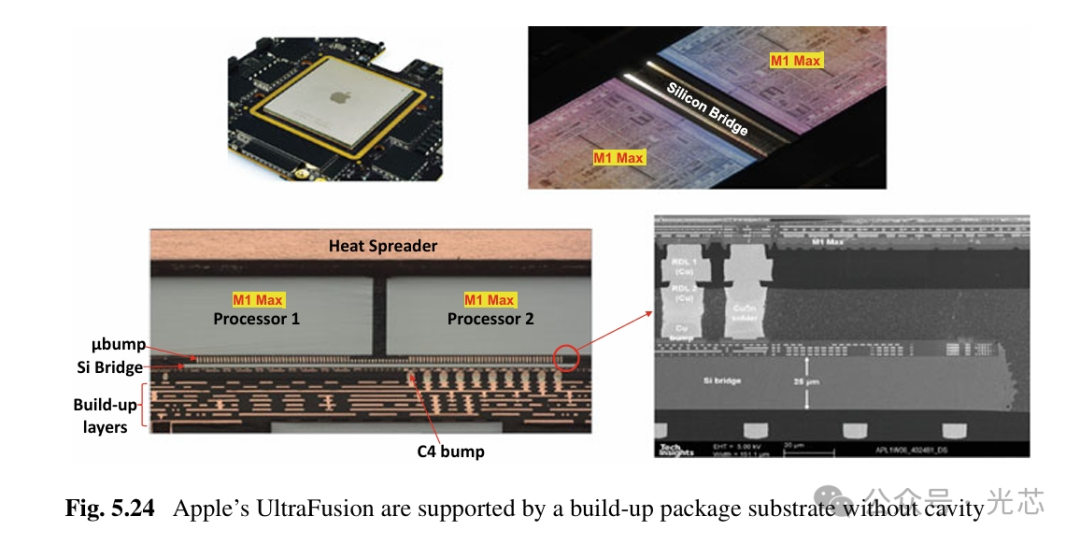

5.7 Apple的UltraFusion

UltraFusion是Apple的创新封装架构,它通过“硅桥”连接两个M1 Max芯片的裸片,创建一个具有前所未有的紧凑设计、广泛连接性、超强性能的SoC。这种架构不仅将两个M1 Max裸片组合成一个单一的芯片封装——它还使2个裸片表现得与1个单一的芯片无异。两个M1 Max裸片之间的互连是通过“硅桥”实现的,如图5.24所示。芯片和Si桥由没有腔的普通积层基板支撑。

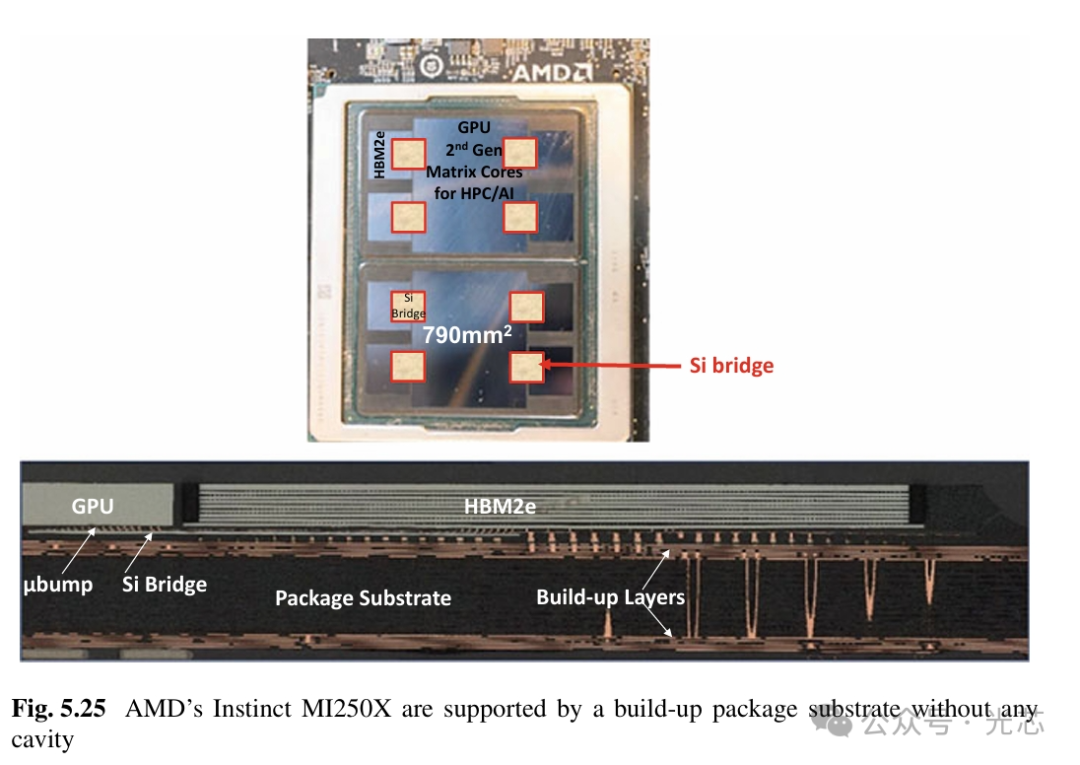

5.8 AMD的Instinct MI250X计算加速器

图5.25显示了AMD Instinct MI250X计算加速器。可以看出,有两个大小为790 mm²的高性能AI计算GPU,每个GPU通过Si桥连接到四个HBM2e。GPU和HBM2E由没有腔的封装基板支撑。

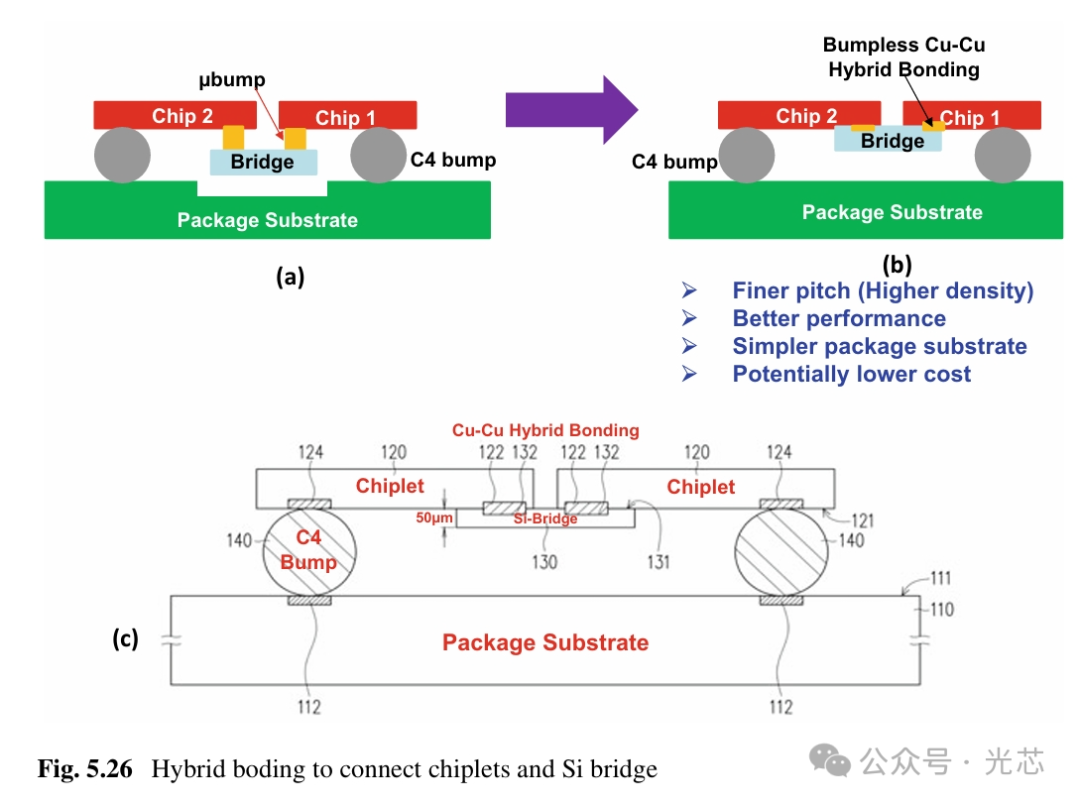

5.9 基于混合键合的桥接技术

Unimicron提出了使用Cu-Cu混合键合桥互连chiplet设计和异构集成封装中的芯片(图5.26)。这种结构的优点是:(1)更高的密度,(2)更好的性能,以及(3)普通的封装基板。可以有两种形式,一种在封装基板上做C4 bump,另一个在芯片晶圆上做C4 bump。

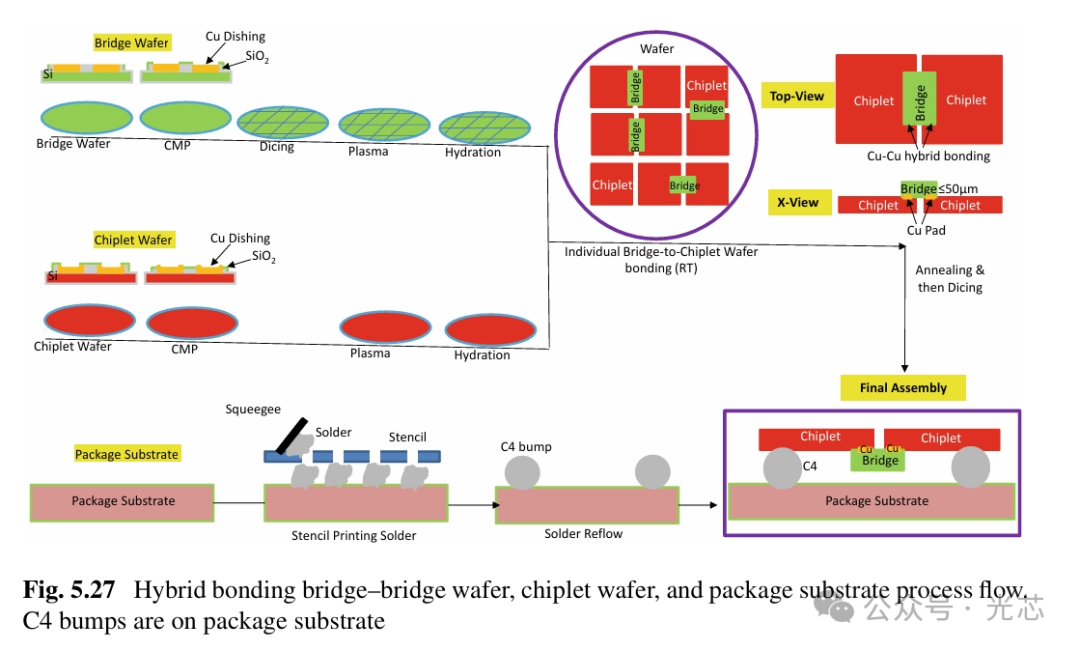

5.9.1 封装基板上带有C4 bump的混合键合桥

图5.27显示了封装基板上带有C4凸点的混合键合桥接的流程。对于桥接晶圆,首先通过化学气相沉积(CVD)制作二氧化硅等介质材料,然后通过优化的化学机械抛光(CMP)过程平整化以制作Cu凹坑。然后,在晶圆表面施加保护涂层以防止在后续键合过程中可能引起界面空洞的颗粒和污染物。这些步骤之后,通过等离子体和水合作用激活键合表面,以获得更好的亲水性和更高密度的羟基团。

对于芯片晶圆,重复CVD工艺用于SiO2,CMP用于Cu凹坑,以及等离子体和水合用于激活键合表面。然后,将单个桥芯片拾取并放置到芯片晶圆上,并在室温下执行SiO2到SiO2键合。这些步骤之后,进行退火以实现氧化物层之间的共价键合以及Cu-Cu接触和Cu原子扩散之间的金属键合。

对于封装基板,通过网板印刷的方式将焊膏涂抹到基板上,然后回流形成C4 bump。对于最终组装,将桥+芯片模块拾取并放置在封装基板上,然后回流C4 bump。

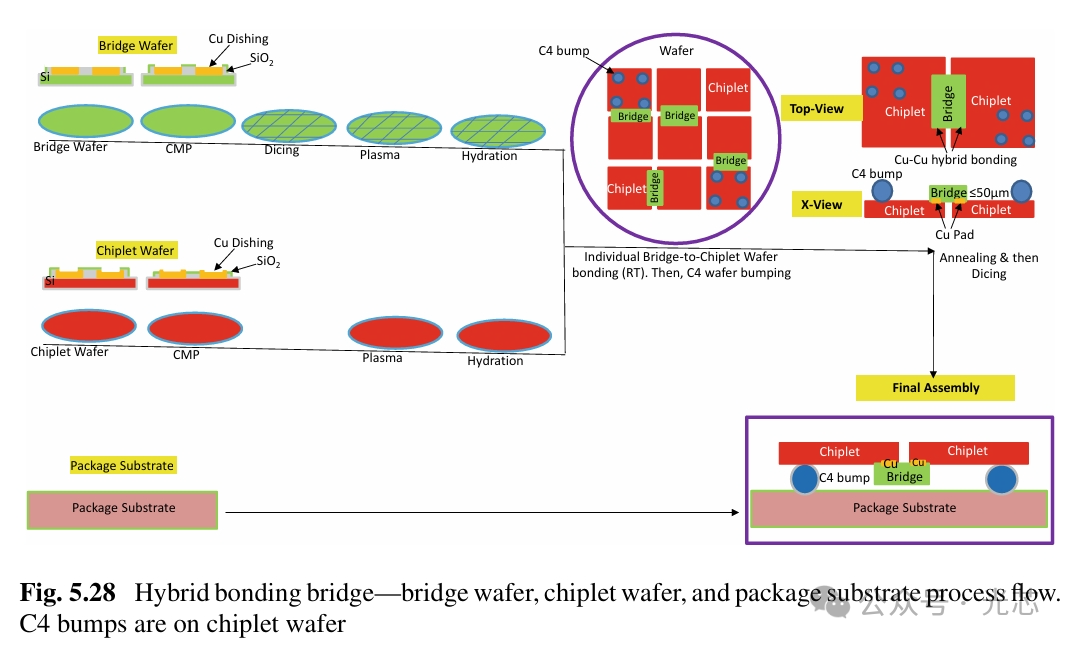

5.9.2 chiplet晶圆带C4 bump的混合键合桥

图5.28显示了chiplet晶圆上带C4 bump的混合键合桥的流程。可以看出,与带C4 bump的封装基板方案相比,桥晶圆和芯片晶圆的步骤直到晶圆键合步骤都是相同的。键合之后,通过晶圆凸点工艺在芯片晶圆上制造C4 bump。然后,将芯片晶圆分割成单独的模块(桥+带C4 bump的芯片)。最终组装是通过在封装基板上拾取并放置单独的模块并回流C4焊点来完成的。

5.10 嵌入式扇出EMC中的脊桥与RDL

Intel、IBM、Apple等公司的刚性桥要么嵌入在有机封装基板中,要么在没有腔的有机封装基板上。还有另一类刚性桥,它嵌入在扇出EMC(环氧模塑材料)中,并连接到扇出RDL基板。

5.10.1 Applied Materials的桥优先Bridge-first和face-up过程

2020年5月12日,应用材料获得了美国专利10,651,126。该公司的设计通过扇出芯片(桥)优先和芯片面朝上过程将桥嵌入EMC中(图5.29)。这可能是刚性桥嵌入扇出EMC的第一个专利。

5.10.2 Unimicron的桥优先和face-down过程

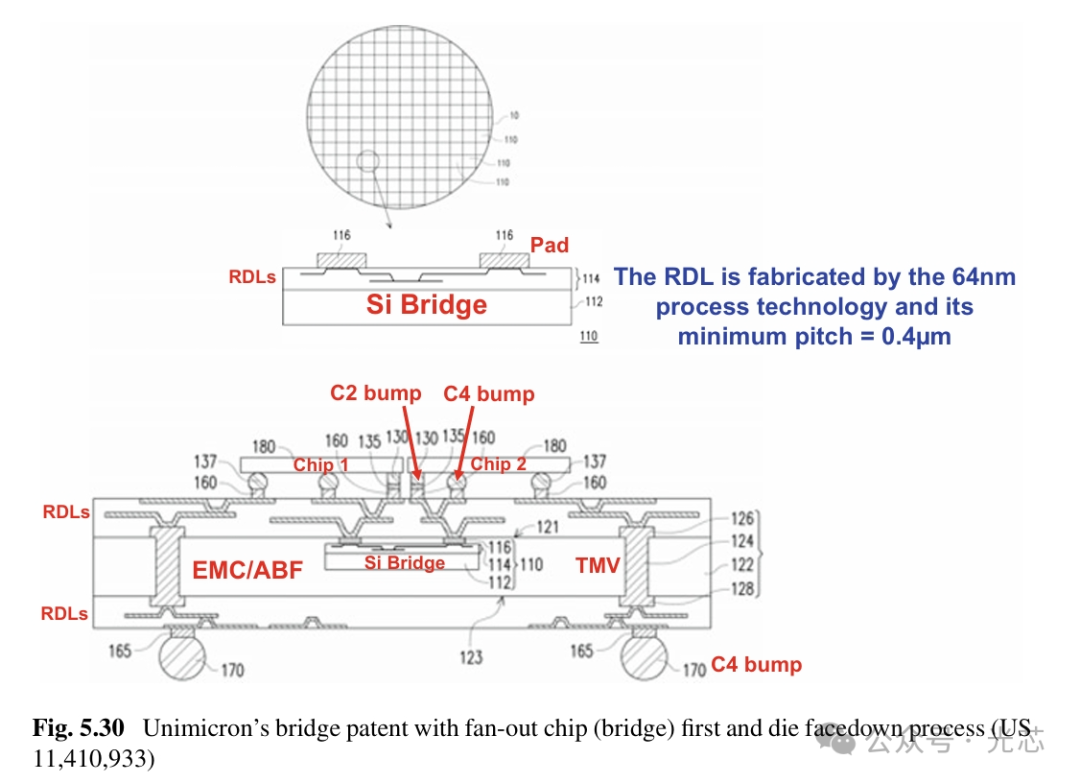

2021年5月7日,Unimicron提交并于2022年8月9日获得了美国专利U.S. 11,410,933,通过芯片(桥)优先和芯片面朝下过程嵌入EMC中(图5.30)。

5.10.3 台湾IME的桥后置(bridge-last)过程

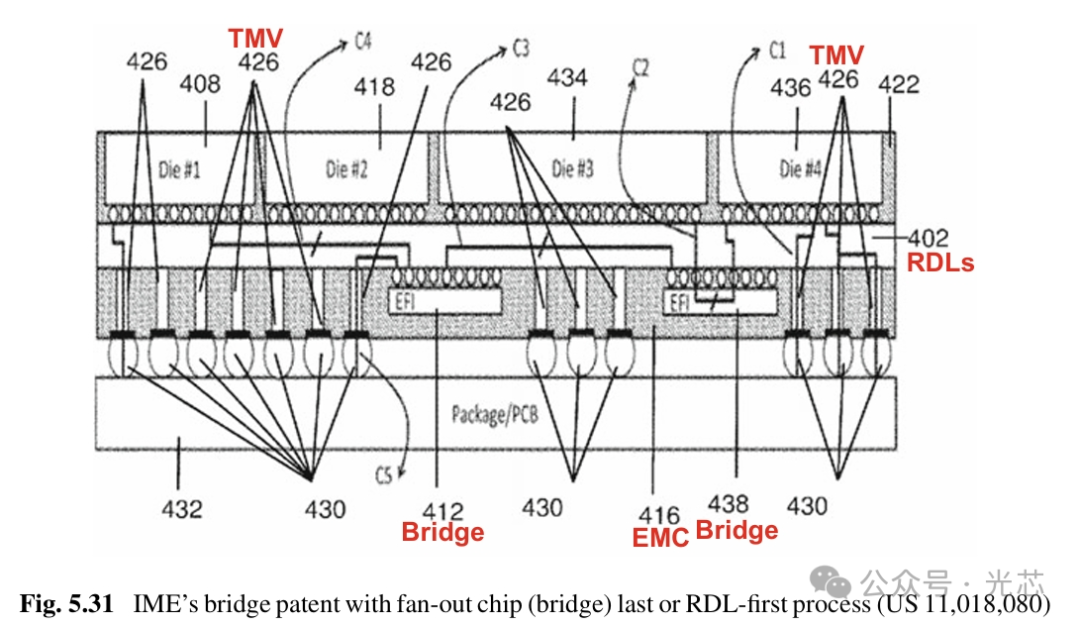

2021年5月25日,IME获得了美国专利U.S. 11,018,080,通过桥接工艺后置或RDL优先扇出的工艺,将桥结构嵌入到EMC中并连接到RDL基板(图5.31)。

5.10.4 TSMC、日月光ASE、安靠Amkor、矽品SPIL和IME的论文

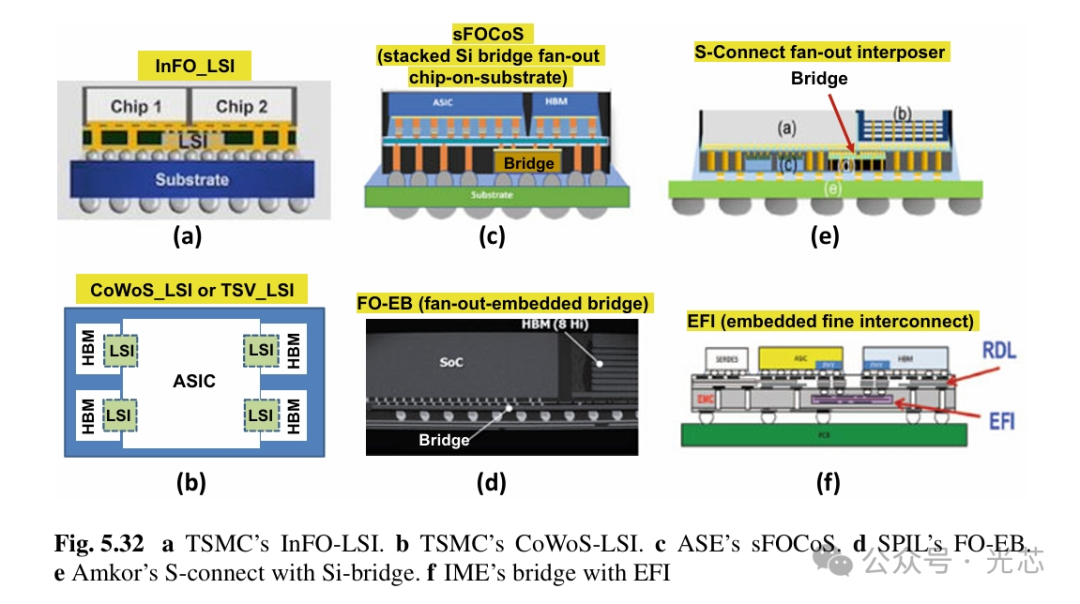

在过去的几年里,有许多关于将刚性桥嵌入EMC中并与RDL互连的论文。例如,在2020年8月25日的TSMC年度技术研讨会上,该公司宣布了其集成扇出局部硅互连(InFO_LSI)和芯片-晶圆-基板局部硅互连(CoWoS_LSI)(图5.32a和b)。

在IEEE/ECTC(2021年6月)期间,至少有四篇论文发表了关于将扇出封装技术应用于嵌入EMC中的刚性桥与RDLs实现横向芯片互连的应用。这四篇论文讨论了非常相似的技术。ASE使用扇出封装方法将桥嵌入EMC,并称之为堆叠Si桥扇出芯片-基板(sFOCoS)(图5.32c)。SPIL将其类似技术称为扇出嵌入式桥(FO-EB)(图5.32d)。Amkor将其技术称为S-Connect扇出中介层(图5.32e)。IME则称之为嵌入式精细互连(EFI)(图5.32f)。

5.11 人工智能(AI)驱动的封装技术

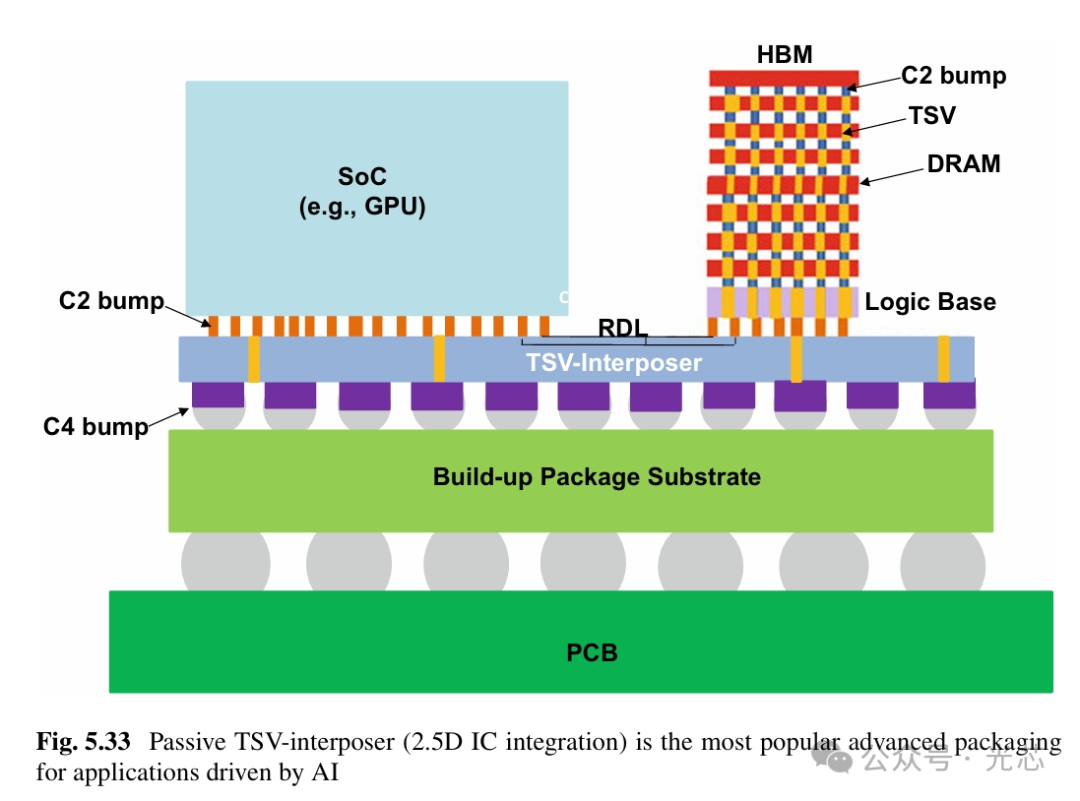

最近,由于AI以及5G/6G的推动,高性能计算(HPC)、自动驾驶汽车、物联网(IoTs)、大数据(用于云计算)和即时数据(用于边缘计算)等应用需求更加先进的半导体封装技术。其中最受欢迎的先进封装技术之一是2.5D或3D集成电路(IC)集成,如图5.33所示。

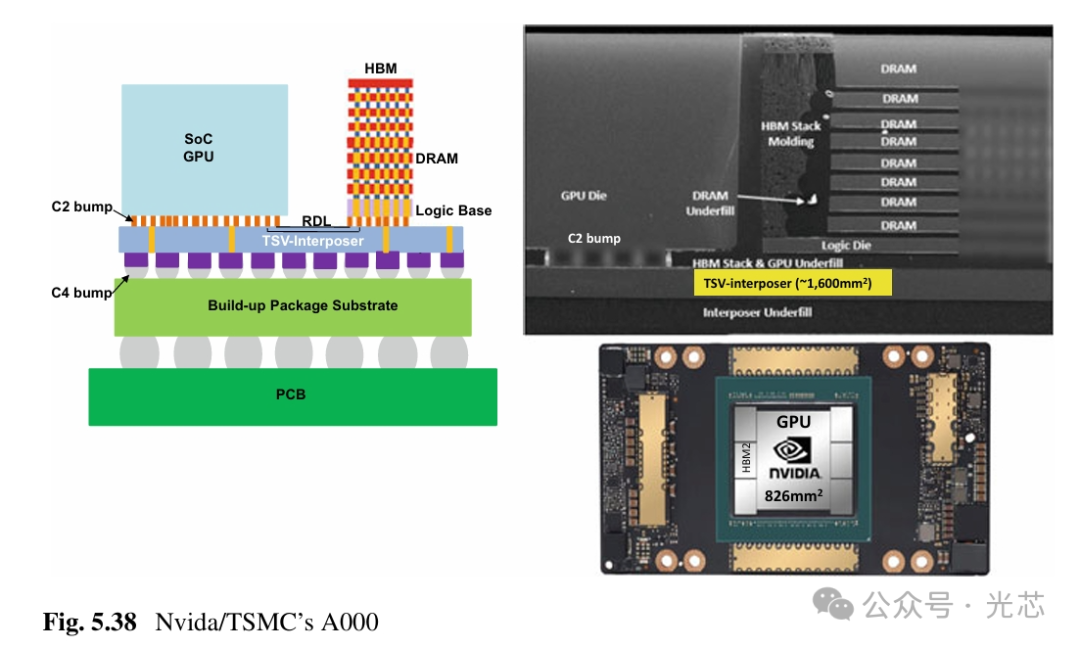

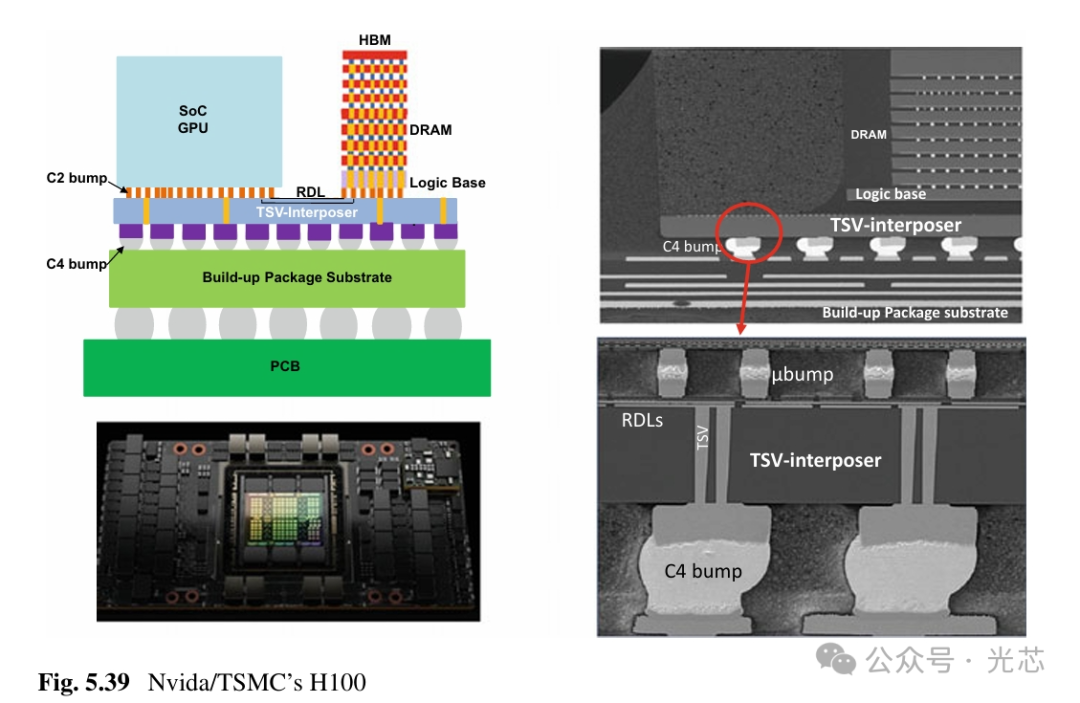

可以看出,系统级芯片(SoC)如CPU、GPU,以及HBM由无源(2.5D)或有源(3D)硅通孔(TSV)中介层和封装基板支撑。最后,整个模块通过球栅阵列(BGA)焊球和焊膏附着在印刷电路板(PCB)上。这种多芯片系统和异构集成封装是由性能和形态因素驱动的,适用于极高密度和高性能应用。

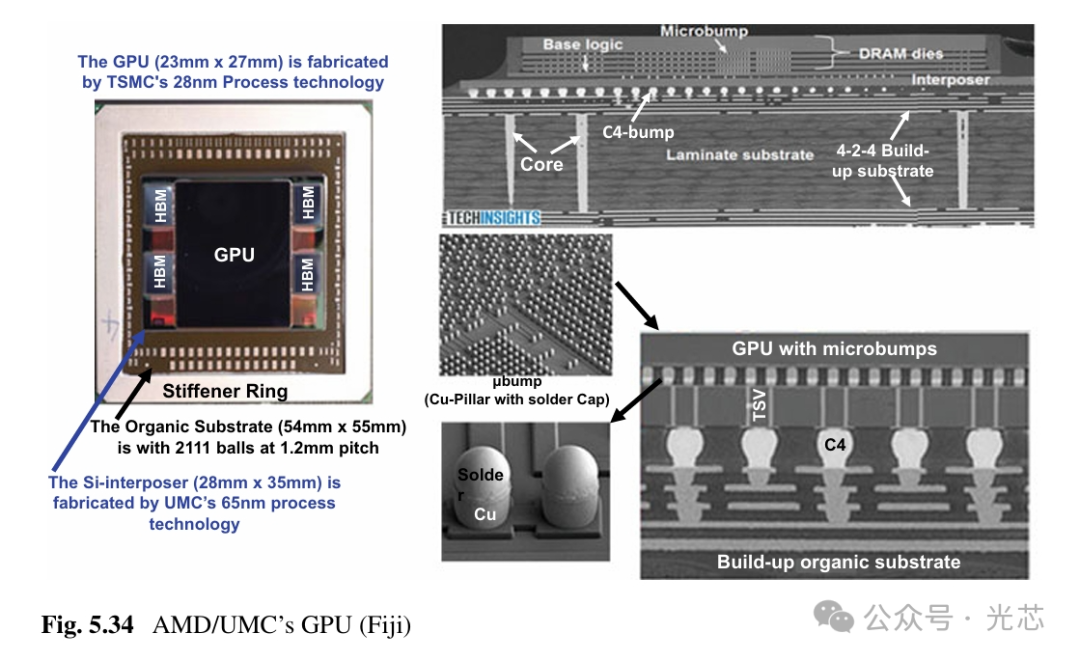

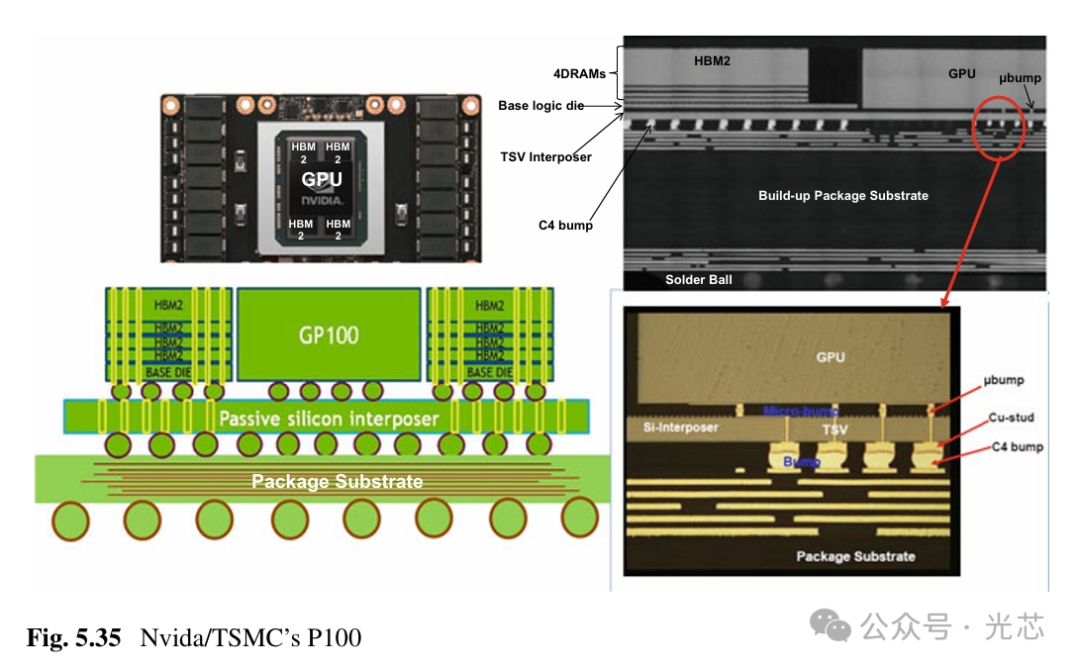

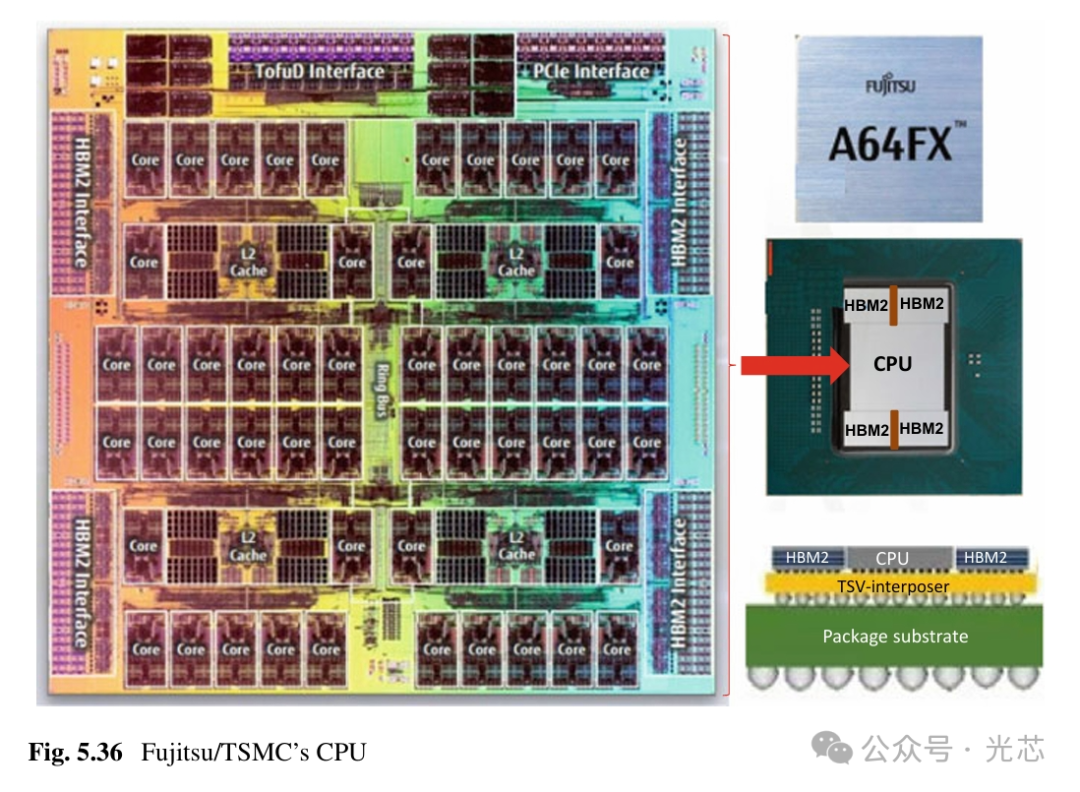

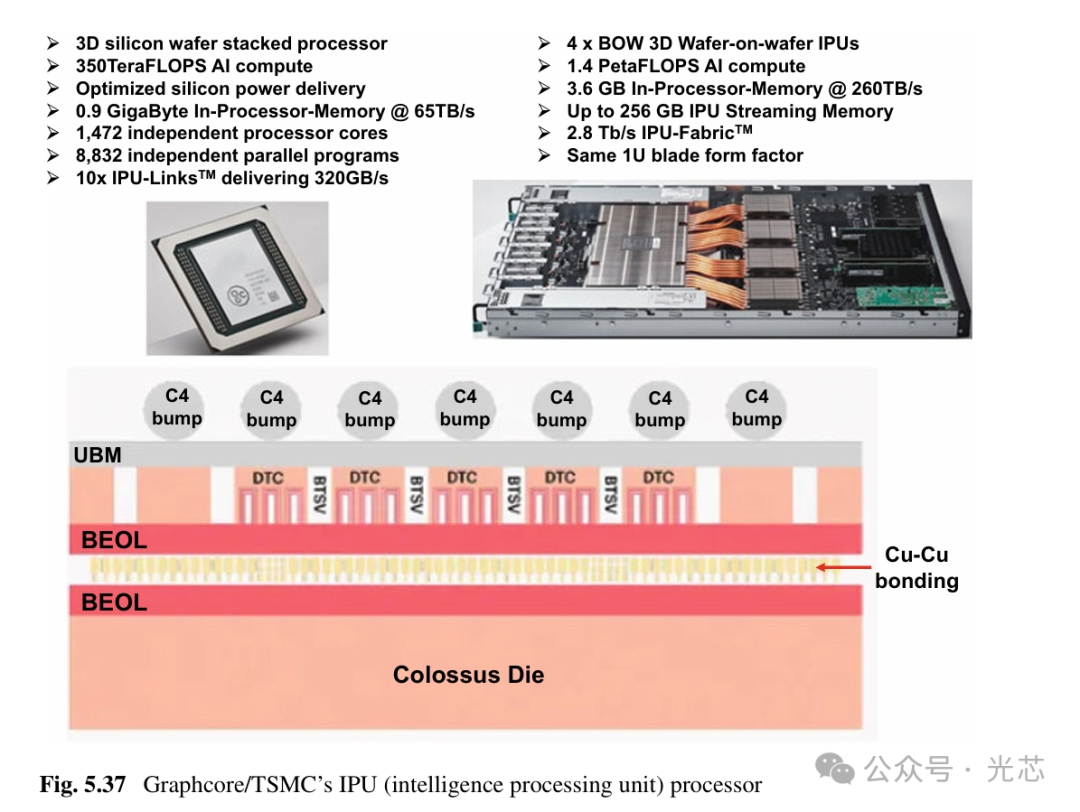

2.5D IC集成技术的历史可以追溯到CEA-Leti在IEEE/ECTC 2005和IEEE/ECTC 2006上发表的首批论文。图5.33展示了2.5D IC集成的一个典型例子。2.5D技术的首个产品(Virtex™-7 HT系列)由Xilinx和TSMC在2013年推出。自那以后,AMD推出了其Radeon R9 Fury X GPU(图5.34),Nvidia推出了其Pascal 100 GPU(图5.35),富士通推出了其Fugaku(A64FX CPU)(图5.36),Graphcore推出了Bow(一款智能处理单元)(图5.37)等。最近,Nvidia推出了其A100 GPU(826mm²),该产品配备了六个HBM2,由一个非常大的TSV中介层支持(图5.38),以及其H100 GPU(图5.39),后者专为AI应用设计。

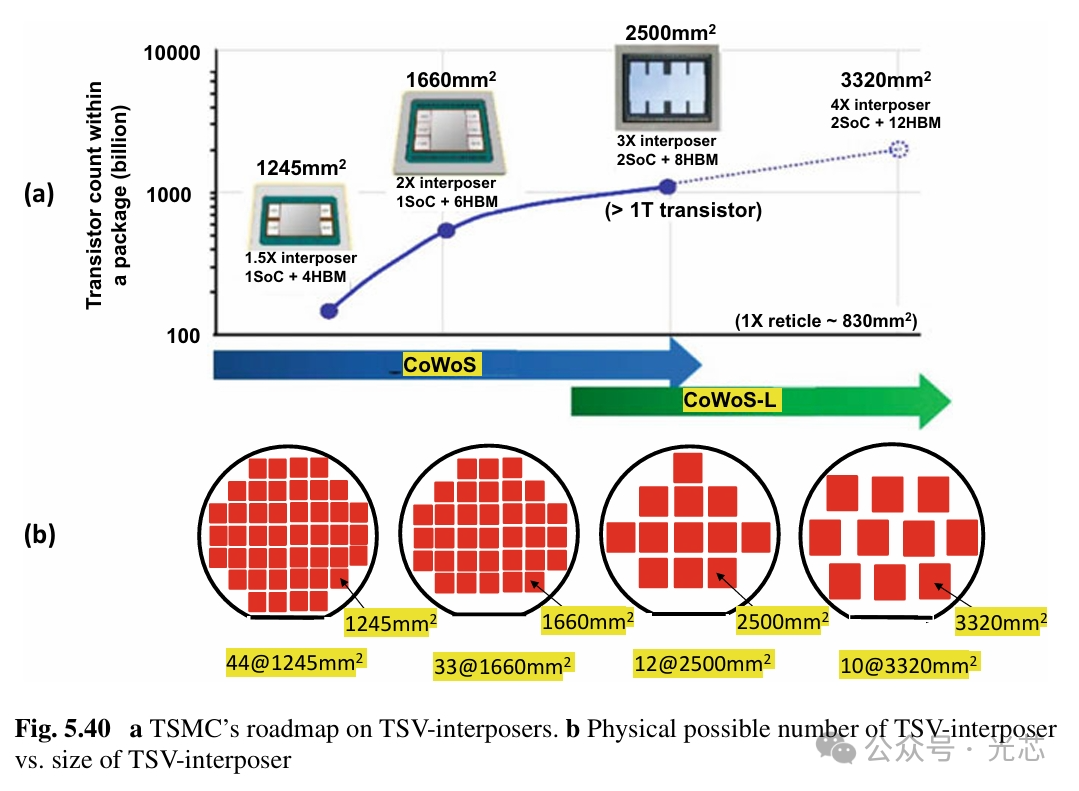

TSMC将2.5D IC集成技术称为芯片-晶圆-基板(CoWoS)。2.5D或3D技术中使用TSV中介层成本很高,这种高成本的主要原因之一是TSV中介层的制造(采用64nm工艺技术)中,由于其加工尺寸较大而导致良率损失高。本节会介绍一些最近在用硅桥替代TSV中介层方面的进展。

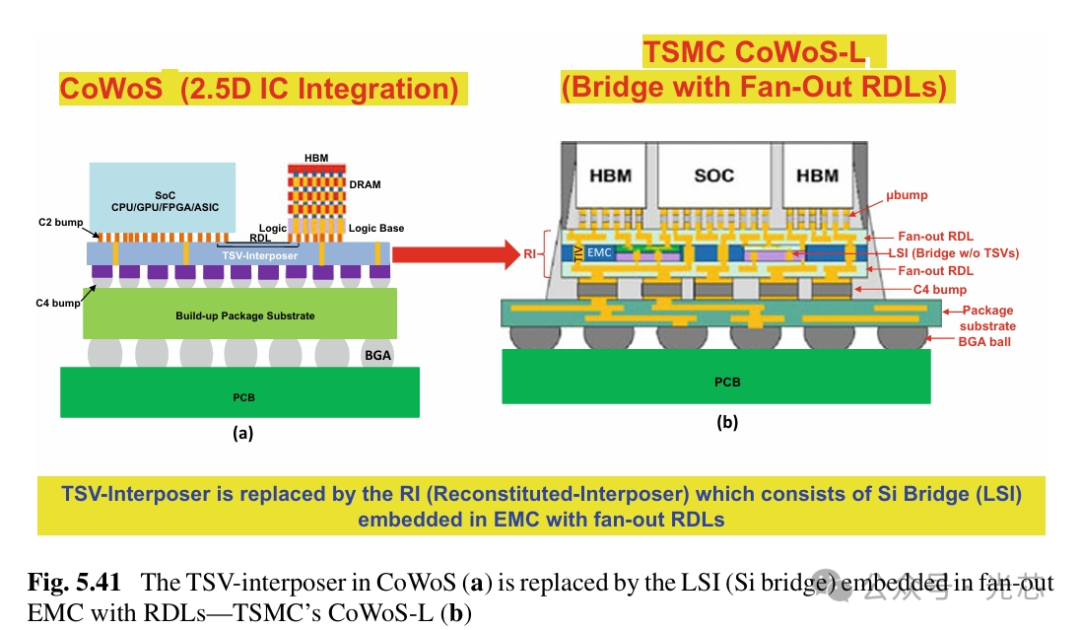

5.12 TSMC的CoWoS-L

在IEEE/ECTC 2023期间,TSMC发表了两篇关于用局部硅互连(LSI)或嵌入在环氧模塑化合物(EMC)中的硅桥(Si-bridge)和扇出重分布层(RDLs)替代其TSV中介层的论文,以解决日益增大的TSV中介层尺寸导致的制造产量损失的问题。

以下是两个例子:TSMC一直在使用CoWoS与1X光罩(830mm²)为Xilinx服务,以及使用2X光罩(1660mm²)为Nvidia服务。对于3X光罩(2500mm²),产量损失太高,因此TSMC引进了一种新的CoWoS-LSI中介层(CoWoS-L),如图5.40a所示。图5.40b显示了在300mm晶圆上可能的TSV中介层数量与TSV中介层尺寸的关系,3X光罩一个12寸晶圆才能做12片基板。TSV中介层尺寸对晶圆产量的影响是显而易见的。

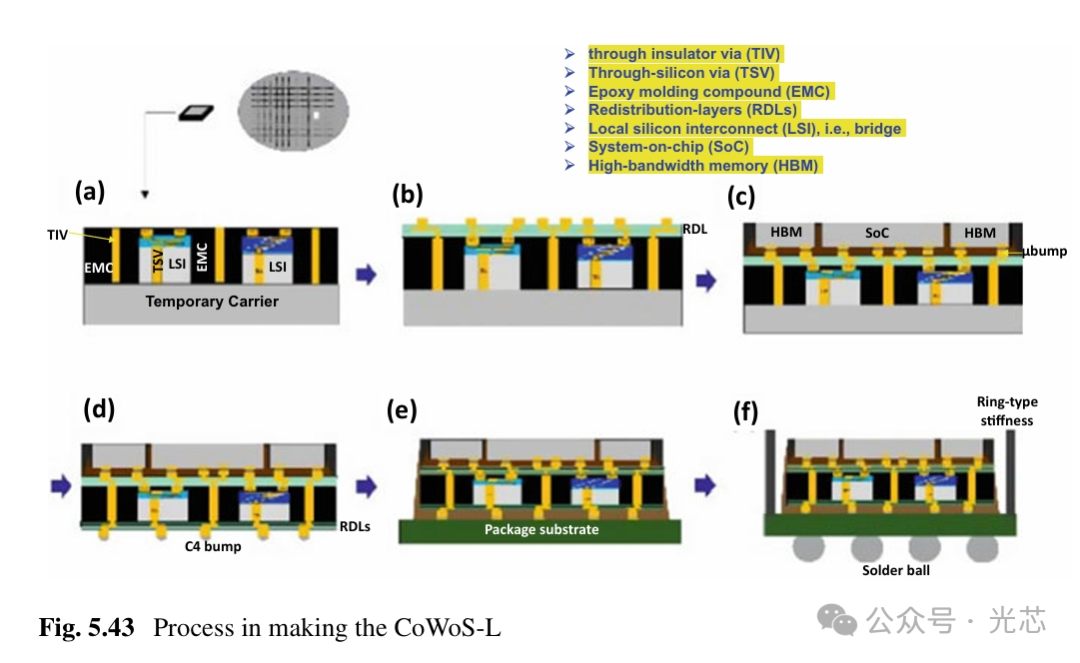

图5.41展示了CoWoS中的TSV中介层(图5.41a)被LSI替代的情况。图5.41b展示了嵌入EMC中的带有扇出RDL的Si桥(CoWoS-L)。CoWoS-L是一种新型中介层,由至少一个LSI(或Si桥)组成,可能包含TSVs和集成扇出(InFO)RDLs,形成一个重构中介层(RI)。

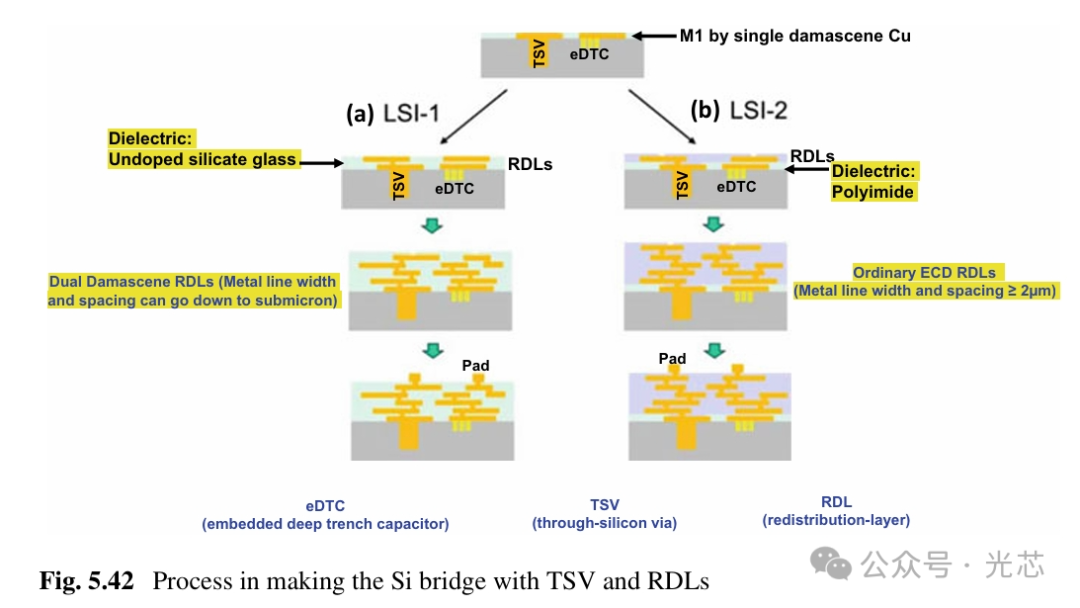

小尺寸LSI继承了TSV中介层的所有优点,保留了亚微米Cu互连(RDLs)、TSVs和嵌入式深沟槽电容器(eDTCs),以确保良好的系统性能。同时,小尺寸LSI避免了与大尺寸TSV中介层相关的问题,例如制造产量损失。小尺寸桥(LSI)的金属L/S节距(最小)= 0.4微米。大尺寸TSV中介层未来会被RI替代,RI由EMC、小尺寸桥(LSI)和可能包含TSV+InFO RDLs组成。RDL和TSV的制造过程如图5.9-5.15和5.42所示,CoWoS-L的制造过程如图5.43所示。

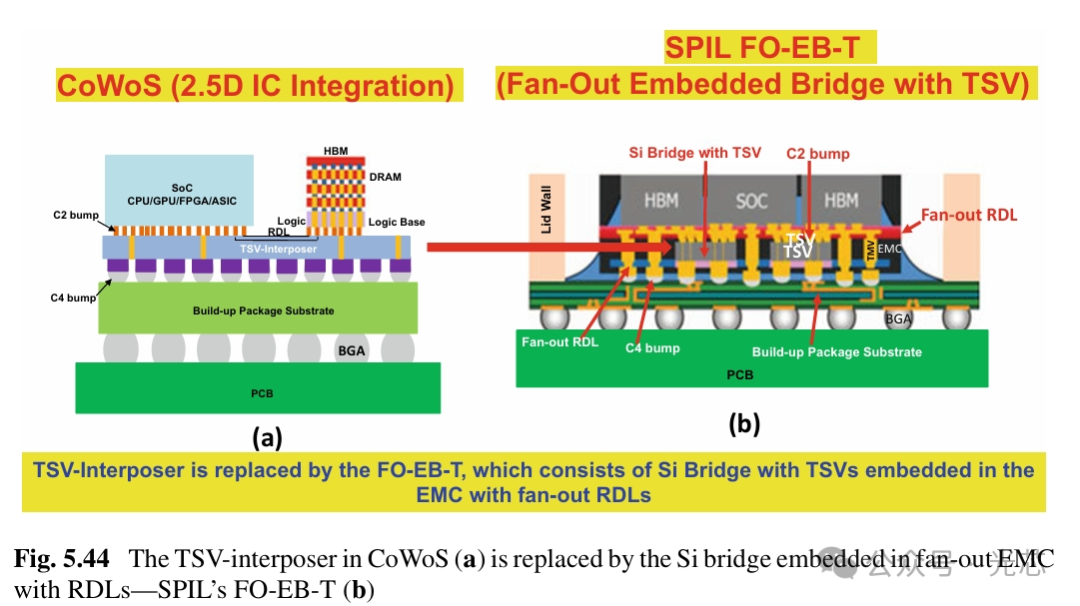

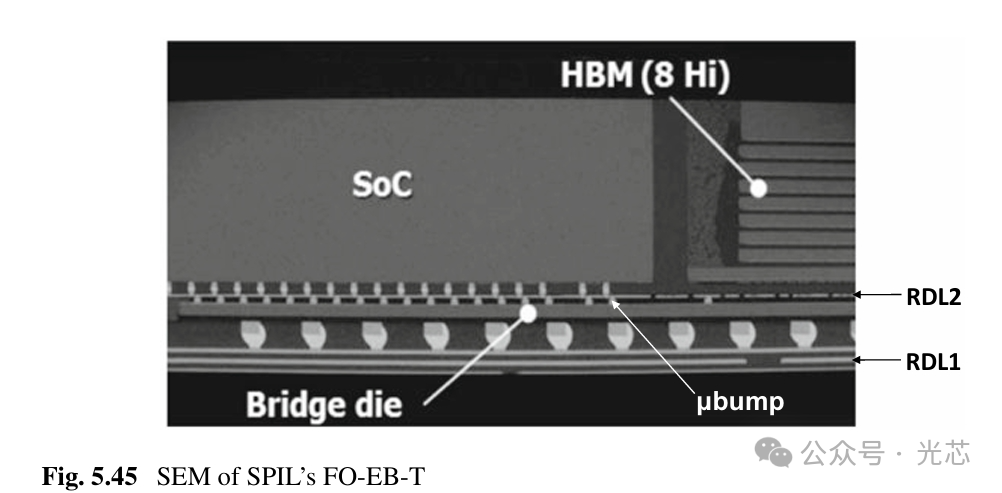

5.13 SPIL的带TSV的扇出嵌入式桥互连(FO-EB-T)

在IEEE/ECTC 2023期间,SPIL发表了两篇关于FO-EB-T的论文。与TSMC的CoWoS-L架构非常相似,SPIL用嵌入EMC中的Si桥和RDLs替代了TSV中介层,如图5.44所示。FO-EB-T的典型横截面如图5.45所示。

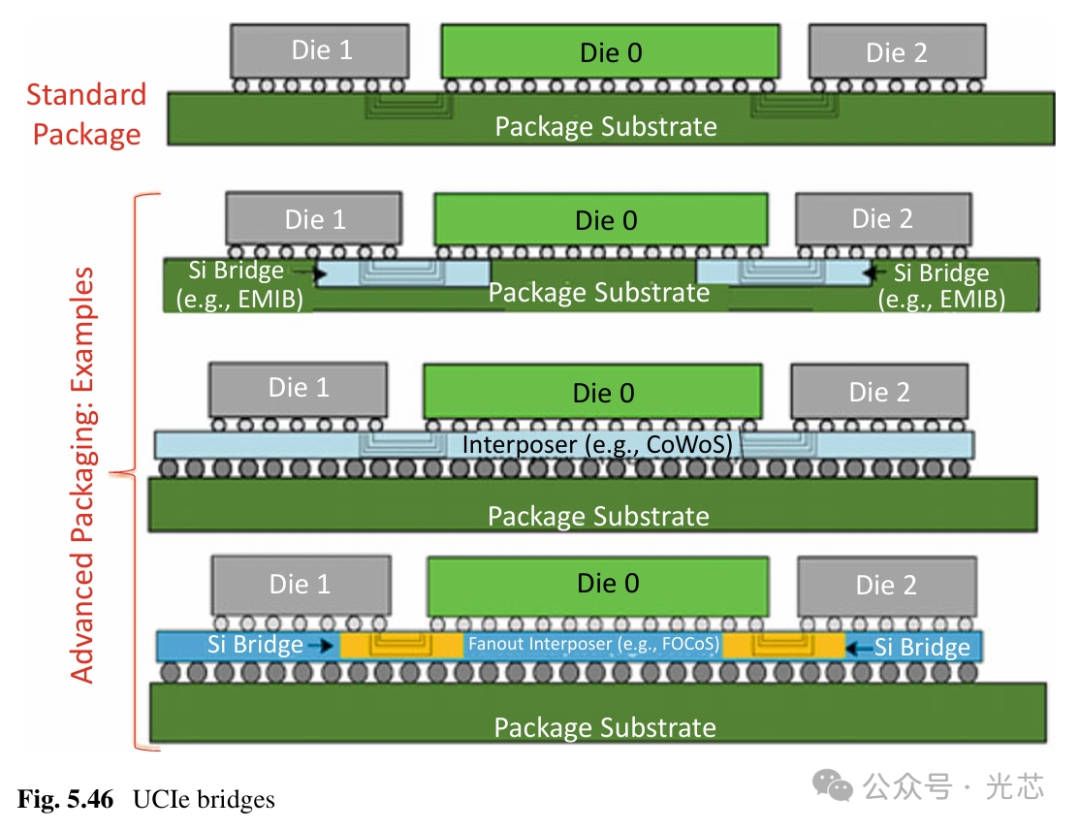

5.14 UCIe产业联盟

与桥接技术相关的一个重要联盟是UCIe产业联盟,如图5.46所示。根据联盟的网站,该组织通过结合了来自可互操作的多供应商生态系统中的最佳die-to-die互连和协议连接,旨在解决了客户对更加可定制化的的封装级集成的需求。这一新的开放行业标准在封装层面建立了一个通用互连标准。UCIe董事会和领导层(推动者)包括创始成员ASE、AMD、Arm、Google Cloud、Intel Corporation、Meta、Microsoft Corporation、Qualcomm Incorporated、Samsung Electronics和TSMC,以及新当选的成员阿里巴巴和NVIDIA。Intel发布了UCIe 1.0规范,提供了一个开放的行业标准,用于在芯片级别实现高速、低功耗的互连,以支持各种高性能计算、人工智能、云计算和网络应用。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2024-11-12,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读