氮化硅SiN集成光波导平台(一):SiN-on-SOI平台

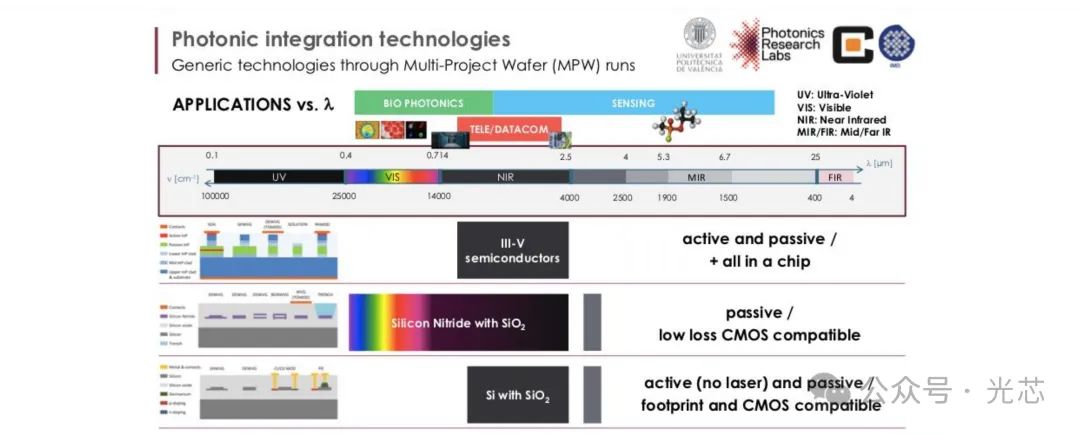

基于氮化硅SiN的集成光波导平台发展历史挺久了,这几年不管是学术界还是产业界,SiN都扮演着越来越重要的角色,包括硅光集成的氮化硅(SiN on SOI),异质集成的氮化硅(Hybrid X/SiN)还有应用于非线性、传感等领域的氮化硅平台等。这里尝试对SiN波导平台做一个总结,分享一些个人观点。第一篇先从目前大规模量产的硅光SiN-on-SOI平台入手,讲讲硅光集成里的氮化硅的必要性以及好处和可能的发展方向。

一、 SiN的必要性和收益

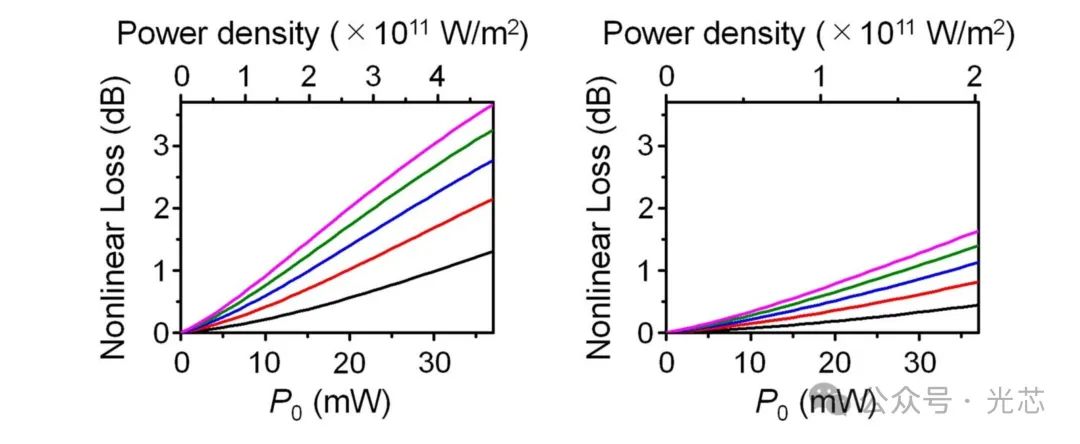

1. 可承受高光功率输入 SiN材料的高功率耐受性,是其必须存在的最大理由。由于硅材料本身存在双光子吸收和载流子吸收效应,吸收导致局部温度升高,达到硅的熔点时,波导就会发生熔断。对于单模硅波导(TE mode,1310nm)来说,普遍认为在9dBm以上时就逐渐有双光子吸收效应的体现,12dBm开始有载流子吸收效应,20 dBm左右硅波导就会发生肉眼可见的波导烧断的现象了。

上图是高功率下单模硅波导的非线性损耗曲线(APE 14,122008,2021)。黑色到红色的曲线代表波导长度1 - 5mm,可以看到在30mW的时候,1mm长的硅波导非线性损耗就达到了1dB。

相比之下,氮化硅材料就耐造的多了,至少30dBm都不会发生问题。像Ligentec的那种致密度高的厚氮化硅波导,官网给的是在10W的光输入依然坚挺。

为什么耐受高功率这么重要呢?对于短距光DR4/DR8模块来说,硅光SiPh相比III-V最大的优势就是可以通过多路集成减少激光器的数量实现成本优势。按照链路预算和典型调制损耗推算,1拖4对应的DFB发光功率是70mW,1拖8的发光功率也达到了100mW。这都接近达到了硅波导生命所不能承受之重。

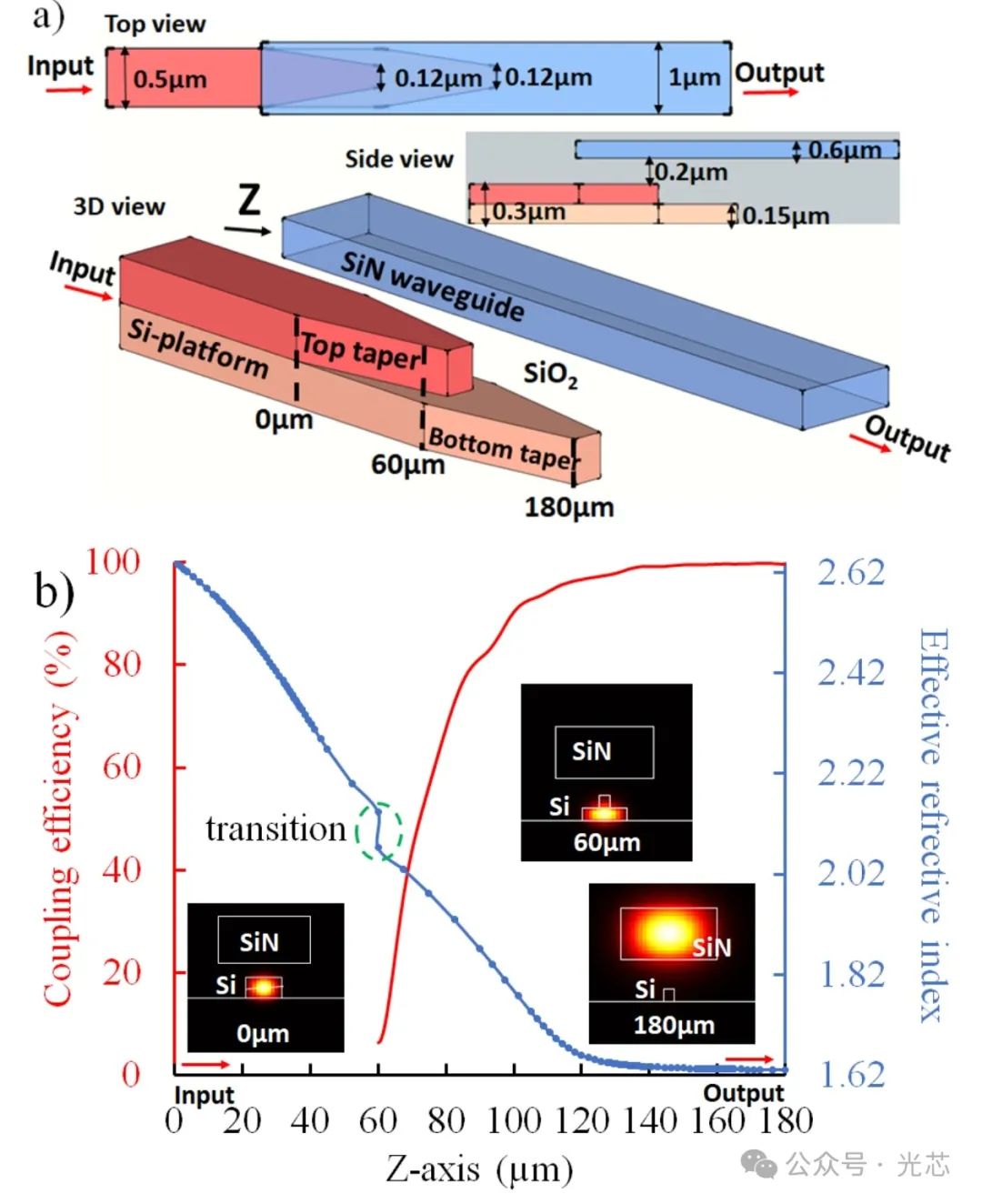

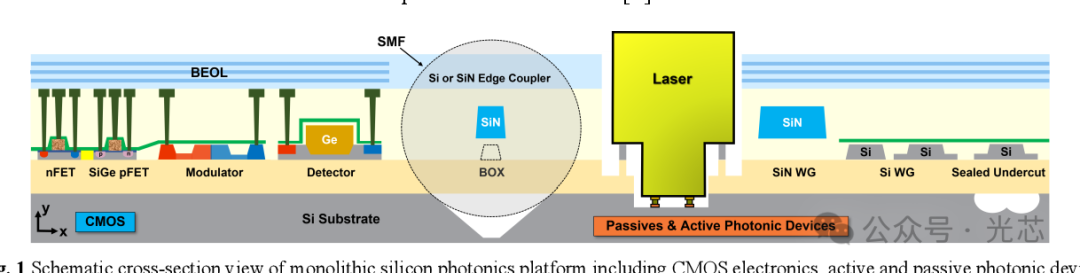

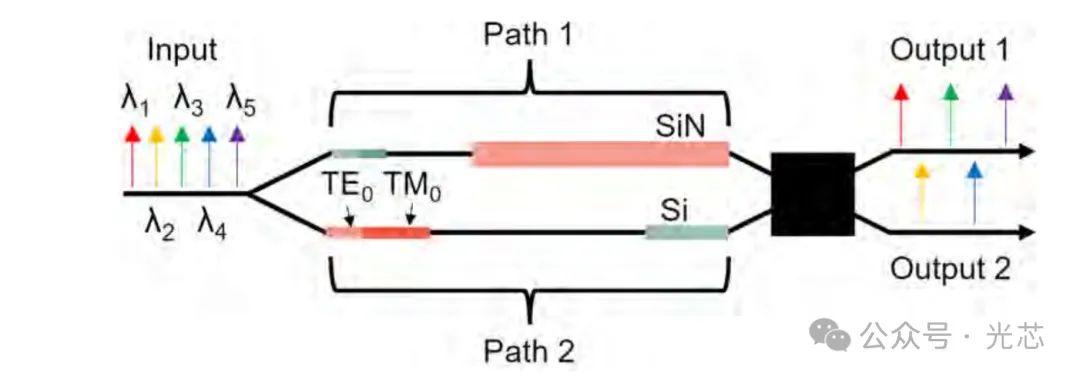

因此,与硅光工艺兼容的氮化硅材料成为了很好的解决方案。实际应用中,激光器的光先通过SiN光纤耦合器+SiN功率分束器,达到安全的功率之后再通过Si-SiN层间耦合器,输入到硅光MZ调制器中完成信号编码。下图是CEA LETI报道的一种层间耦合器的方案,目前各大Foundry的层间耦合性能基本都可以达到<0.1dB的水平(TE mode)。

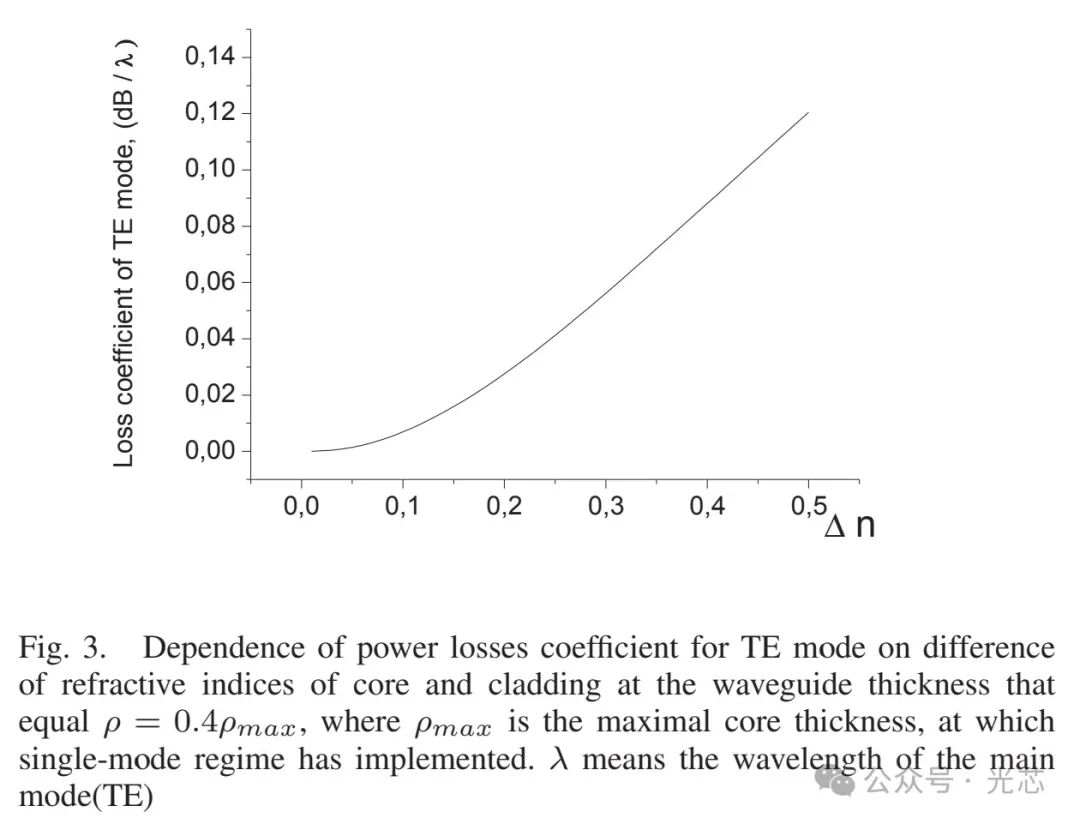

2. 折射率适中:实现低损耗的关键 谈起氮化硅vs硅的最大优势,一般会说损耗低是最大的优势。而这个优势的来源,其实我认为是材料折射率适中所带来的。集成光波导器件损耗的来源,包括了波导本身吸收和散射带来的传输损耗,以及器件侧耦合损耗、偏振相关损耗PDL、波长相关损耗WDL等的插入损耗两部分。 对于波导传输损耗来说,在低功率下,光波导材料选取的都是透明窗波段,吸收损耗几乎可以忽略。而散射损耗则与折射率差强相关。折射率差越大,界面处(上下表面、侧壁)的不平坦都会对光场有明显的散射。相反,折射率差越小,倏逝波的拖尾更长更平缓,芯层和包层的界面就越“模糊”,对光场的影响就越小了。

除了走线波导的散射损耗差异,对于定向耦合器、MMI等器件来说,SiN波导器件界面的散射变小,波导间的耦合也更容易,对于最小波导间距的控制及加工误差也放松了,尺寸有一定增加,但损耗明显降低了。 再来说说其他类型的插入损耗。对于耦合损耗来说,由于单模波导的物理截面尺寸比单模光纤是小很多的(<0.5um² vs 16um²),因此耦合处需要通过将波导物理尺寸减小(taper)实现模斑的扩大,与光纤实现模斑匹配。Taper尖端尺寸选取的关键,就是寻找有效折射率能够接近光纤折射率所对应的宽度。折射率差越大,对应的taper宽度就越窄,加工上就更为困难/对工艺敏感。比如O波段,硅波导要想把折射率降低到1.45(TE & TM),对应的尺寸需要到100nm左右,而氮化硅只需要150nm左右,这两个尺寸的区别就对工艺节点、良率、工艺误差(都反映在成本上)带来了显著的区别。

同样,对于降低PDL和WDL,低折射率差同样有显著的贡献。首先,偏振对于标准的单模硅波导(410nm x 220nm)是比较难受的,TE模和TM模的有效折射率差Δn>0.8,传输损耗(线性和非线性)也有显著的差异。而SiN波导的模式双折射则小了很多(Δn<0.1),这对器件的双偏性能就比较友好了。

而波长相关损耗同样是因为SiN波导模式有效折射率的色散更为平缓,因此对于无源器件比如波分器件、功分器件的设计更简单,器件插损/工作带宽性能也更好。尤其在O波段,Si和SiN的材料色散系数dn/dλ分别为-0.15 和-0.03 (um-1),有着5倍的差异。因此Si的宽带器件通常需要比较精细的设计,通过比较复杂的截面设计用波导色散补偿材料色散。而SiN宽带器件的设计就简单了很多。

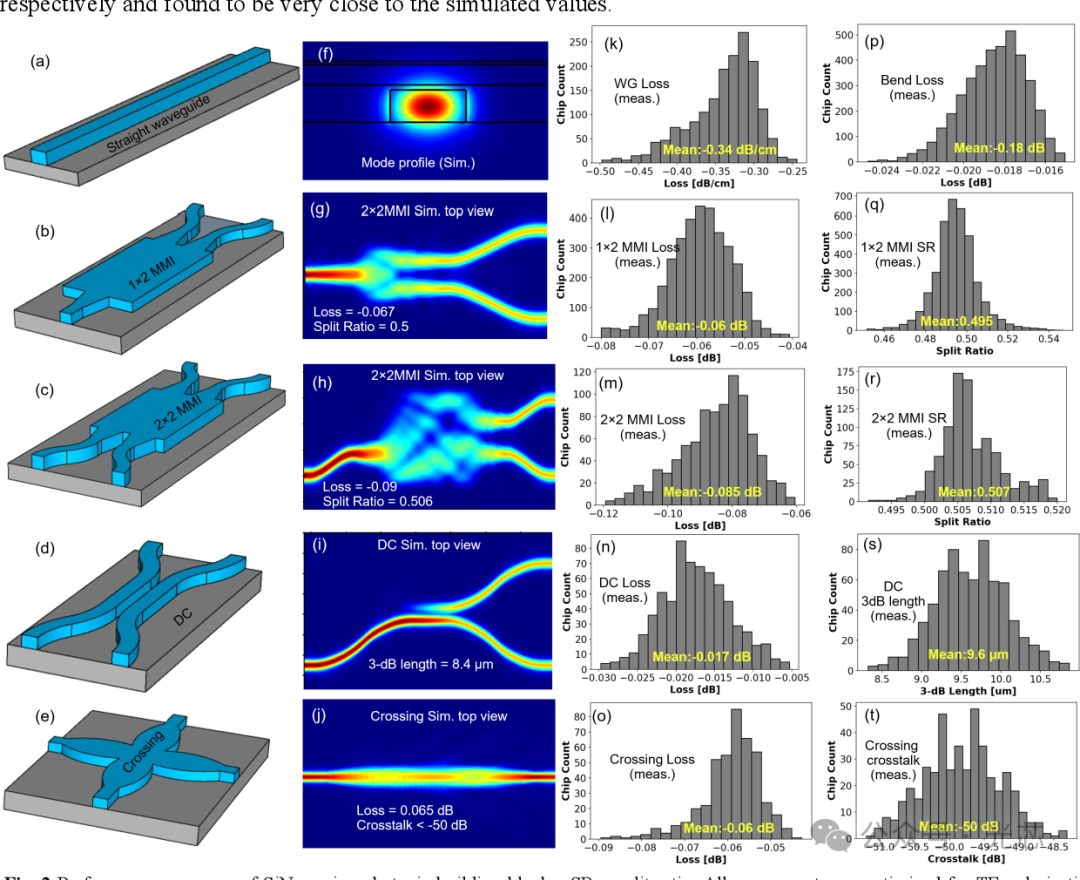

今年的OFC上,GlobalFoundries和AIM photonics都提到了利用SiN来制备无源器件,可以获得比Si好得多的性能。比如氮化硅的MMI器件插损都可以做到<0.1dB,分光比也控制得相当好。

3. SiN和Si的混合波导:更大的设计自由度

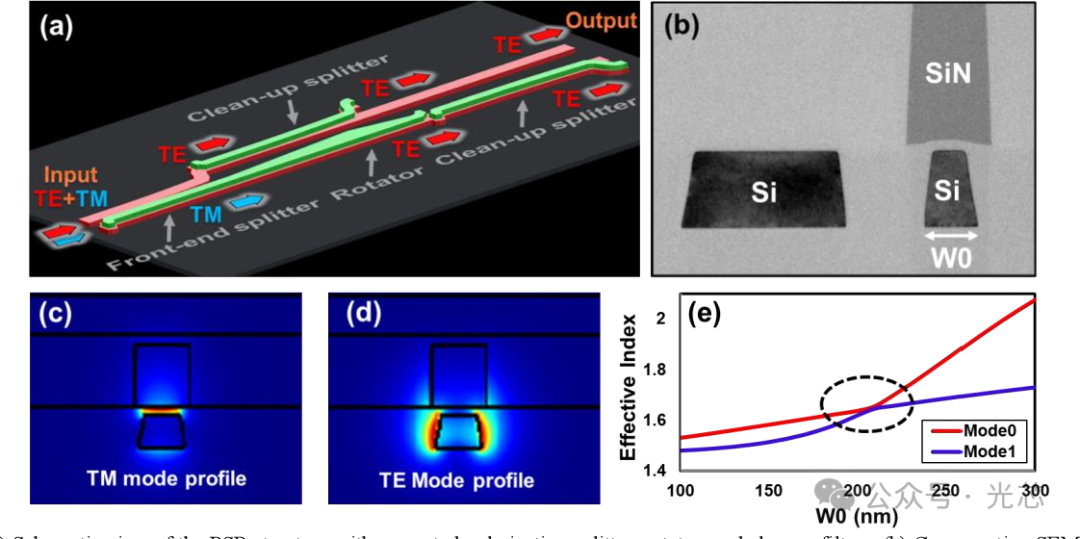

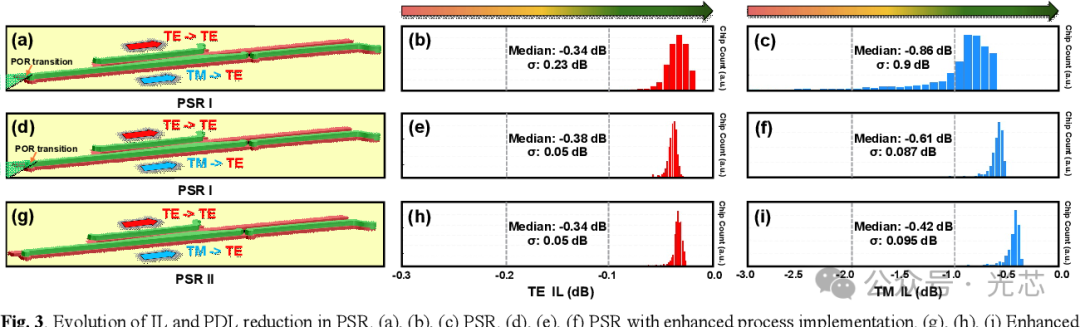

除了拿纯氮化硅做无源器件以外,由于SiN也会对Si的模场分布产生影响,因为还可以利用SiN来实现更灵活/更稳定的模场/色散调控。像GF报道的偏振分束旋转器PSR,就是利用了混合波导的模式特性,从而实现了<0.4dB的损耗。

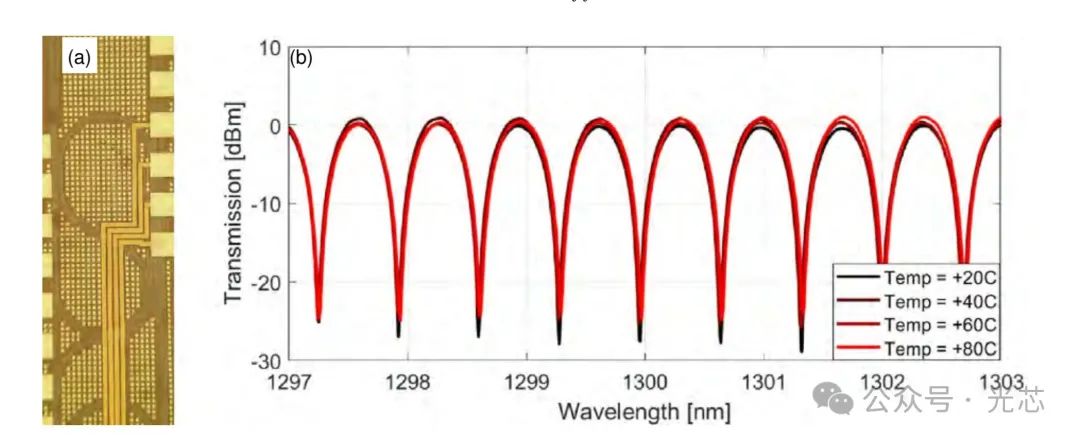

利用两种材料不同的热光系数,J. Bowers报道了利用Si/SiN混合波导相位补偿,实现了无热化且加工不敏感的interleaver滤波器,在20-70℃的范围内波长都不漂。

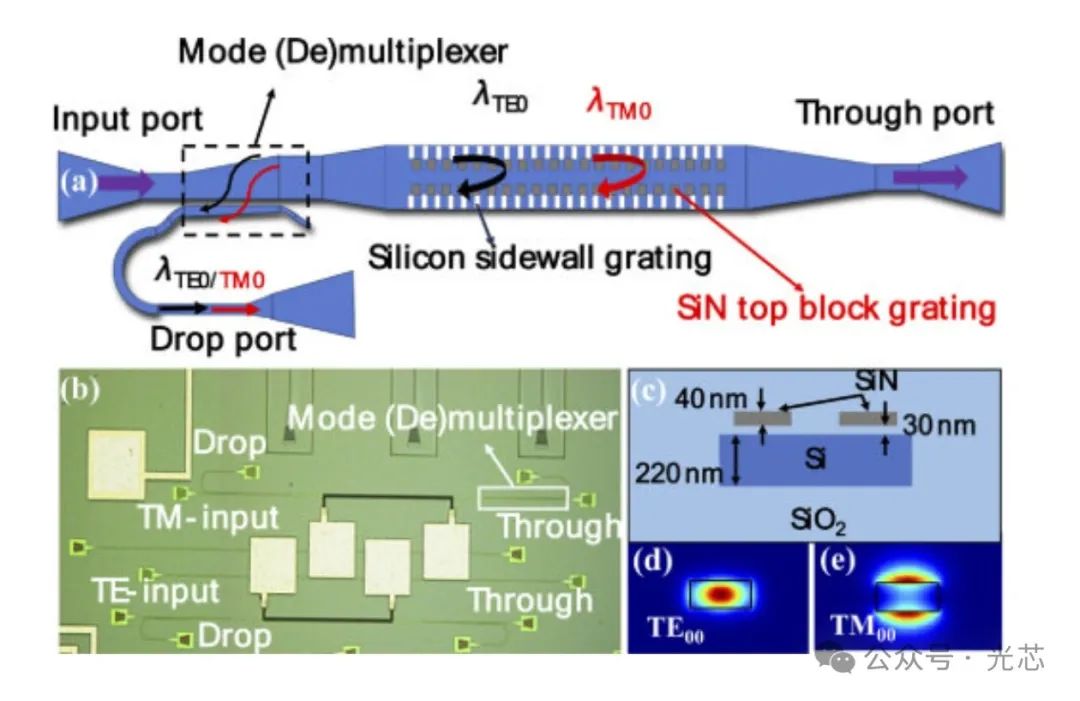

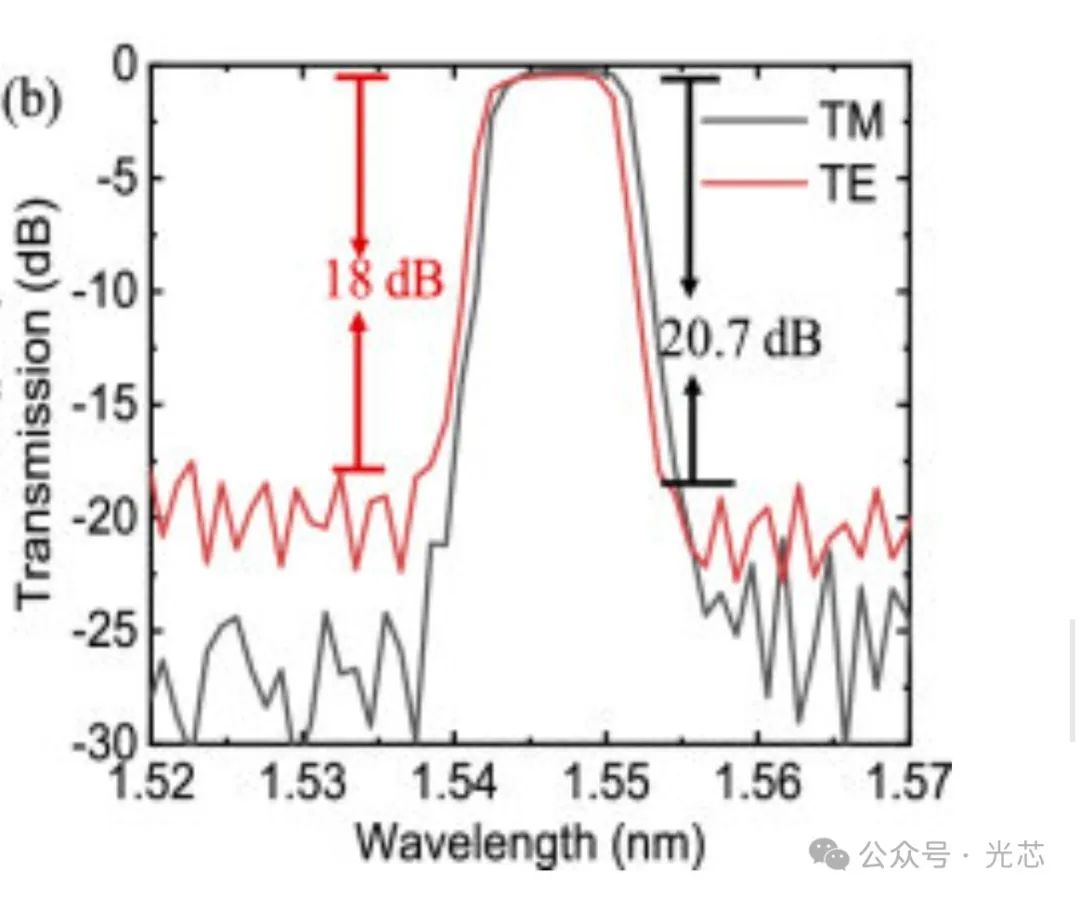

浙大余老师、杨老师组报道了利用Si/SiN波导的高阶模式调控,实现了一种偏振无关的滤波器。这几个案例都是单独的Si和SiN都难以实现或实现得不太好,两者结合之后,利用新的调控维度,产生了1+1>2的效果。

二、SiN-on-SOI平台可能的发展方向

1. 高质量SiN波导的加工

SiNOI波导已经有很多家可以实现很低的损耗(<5dB/m),但SiN-on-SOI的损耗挺多都还是要达到0.5dB/cm以上甚至更大。这是因为高质量的低损耗SiN波导需要通过>1100℃的高温退火工艺来驱除氢键以及减少薄膜的缺陷,而高温工艺的引入与原本硅光工艺里边的离子注入以及金属工艺是不兼容的,因此很多Foundry采用的都是PECVD低温沉积SiN(与用于做阻挡层的SiN工艺相同)。低温沉积无退火得到的氮化硅薄膜致密度较低,厚度和折射率均匀性较差,光学性能的长期稳定性未知,做阻挡层OK,做光波导就不咋地了。

当然,也有foundry比如Tower是可以提供高质量的SiN-on-SOI工艺,猜测大概是调整了工艺步骤,将高温退火工艺置于前端,避免了对后续工艺的影响。随着氮化硅重要性的提升,以后能提供低损耗SiN-on-SOI工艺的流片资源应该也会逐渐增加。

2. SiN规格的标准化

SOI是单晶材料bonding到氧化硅衬底,折射率固定,厚度大家也都统一到了220nm(虽然GF也有些其他厚度规格的硅光器件)。但是非晶态、沉积型的SiN就不一样了,各个Foundry提供的薄膜折射率、厚度、均匀性、与Si层的氧化层间距、加工规则等都存在不小的差异,更换流片厂意味着一切SiN的设计从头再来。由于SiN-on-SOI平台的潜力还没有全部被挖掘,学术界和工业界暂时也无法讨论出最佳的参数,不知道未来是否在某个参数区间内达成共识。

3. 多层SiN工艺

Foundry所提供的Si波导刻蚀一般都有三层,分别用于条形波导、脊波导以及光栅耦合器结构。相比之下,氮化硅光波导层就比较寒酸了,仅有少量Foundry能提供两层SiN的工艺,大多都还是单层、单次刻蚀的工艺。假如可以从多层SiN或者浅脊SiN波导等结构中获得新的收益(比如多层波导走线实现更高密度的集成、异质集成等),相信大家也愿意去发展这个方向。

三、总结

1. 优势:扛高功率的绝佳选择、更好的无源性能、额外的设计自由度

2. 可能的发展方向:高质量的加工工艺实现更好更稳定的无源性能、规格的统一、更丰富的工艺选择提供更多的设计优化空间

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2024-10-09,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读