无法在active -hdl 10中使用组件

无法在active -hdl 10中使用组件

提问于 2017-12-09 16:28:36

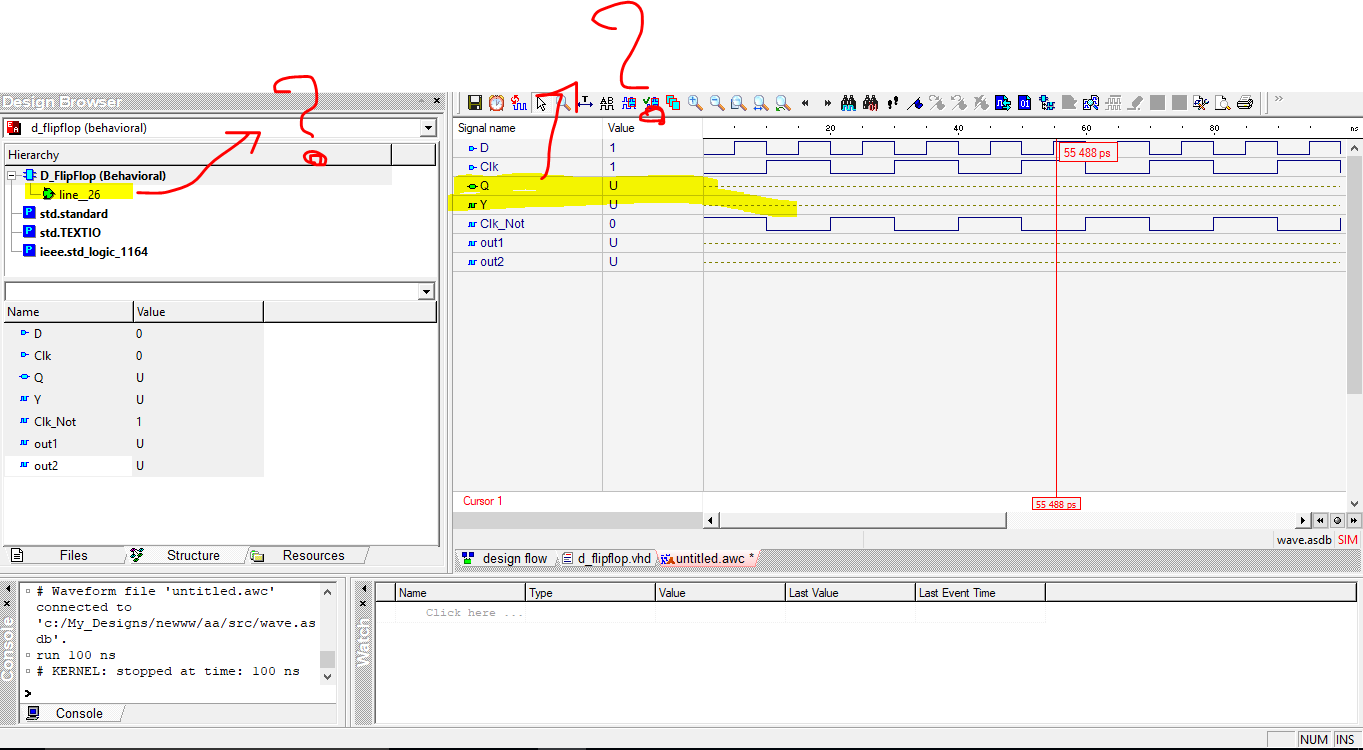

我使用active-hdl 10来编译和模拟一个DFlipFlop结构。我的代码编译成功,没有任何错误或警告,但是当我模拟它时,我的输出有未知的值。

(点击放大)

我在xilinx和active-hdl 8中编译并模拟了这段代码,没有任何问题。

D_FlipFlop代码:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity D_FlipFlop is

Port ( D : in STD_LOGIC;

Clk : in STD_LOGIC;

Q : inout STD_LOGIC);

end D_FlipFlop;

architecture Behavioral of D_FlipFlop is

component DLach Port ( D : in STD_LOGIC;

C : in STD_LOGIC;

Q : inout STD_LOGIC;

Qprim : inout STD_LOGIC);

end component;

Signal Y : STd_logic;

Signal Clk_Not : Std_Logic;

Signal out1 : Std_Logic;

Signal out2 : Std_Logic;

begin

Clk_Not<=not(clk);

h1 : DLach port map(D=>D,C=>clk,Q=>Y,Qprim=>out1);

h2 : DLach port map(Y,Clk_Not,Q,out2);

end Behavioral;Dlach代码:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity DLach is

Port ( D : in STD_LOGIC;

C : in STD_LOGIC;

Q : inout STD_LOGIC:= '0';

Qprim : inout STD_LOGIC:= '1');

end DLach;

architecture Behavioral of DLach is

Signal first : Std_logic ;

Signal second : Std_logic ;

Signal D_not : Std_logic ;

begin

D_Not <= not(D);

first <= D Nand C;

second <= D_not nand C;

Q <= first nand Qprim;

Qprim <= second nand Q ;

end Behavioral;我做了很多研究,但找不到答案。所以我认为这个剂量对于他们使用活性-hdl的试用版本是有效的。

回答 1

Stack Overflow用户

回答已采纳

发布于 2018-11-14 11:51:21

我搜索了很多关于这个问题,似乎没有人出现这个问题。因此,我认为这个问题发生在试用版的active -hdl 10或破解版本。

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/47730637

复制相关文章

相似问题