此设计包含一个或多个与Spartan6体系结构直接不兼容的寄存器/闩锁。

此设计包含一个或多个与Spartan6体系结构直接不兼容的寄存器/闩锁。

提问于 2017-08-30 21:34:38

我是这个世界上的新人。

事实上,我在学习VHDL。我编写了以下代码:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity Problems is

port(

S : in std_logic;

D : in std_logic;

CLK : in std_logic;

R : in std_logic;

Q : out std_logic;

Q_n : out std_logic

);

end Problems;

architecture Behavioral of Problems is

signal t_tmp1 : std_logic;

begin

DFF: process (S,R,D,CLK)

begin

if (S = '0' and R = '0') then

t_tmp1 <= not t_tmp1;

elsif (S = '0' and R = '1') then

t_tmp1 <= '1';

elsif (S = '1' and R = '0') then

t_tmp1 <= '0';

elsif (rising_edge(CLK)) then

t_tmp1 <= D;

end if;

end process DFF;

Q <= t_tmp1;

Q_n <= not t_tmp1;

end Behavioral;当我合成时,出现以下警告:

警告: the编译器:92- "/home/joseph/ISEProjects/Exercise_BasicMemoryElements/Problems.vhd“第41行: t_tmp1应该在进程的敏感性列表中 警告:Xst:3002-此设计包含一个或多个与Spartan6体系结构直接不兼容的寄存器/锁存器。造成这种情况的两个主要原因要么是异步集和异步复位所描述的寄存器或锁存,要么是由异步集或复位描述的寄存器或锁存,而后者具有相反极性的初始化值(即初始化值为1的异步复位)。

模拟效果很好。

我想知道为什么要发出警告,我要学些什么来解决这样的问题。

致以敬意,

约瑟夫·培尼亚。

回答 1

Stack Overflow用户

回答已采纳

发布于 2017-08-30 23:30:45

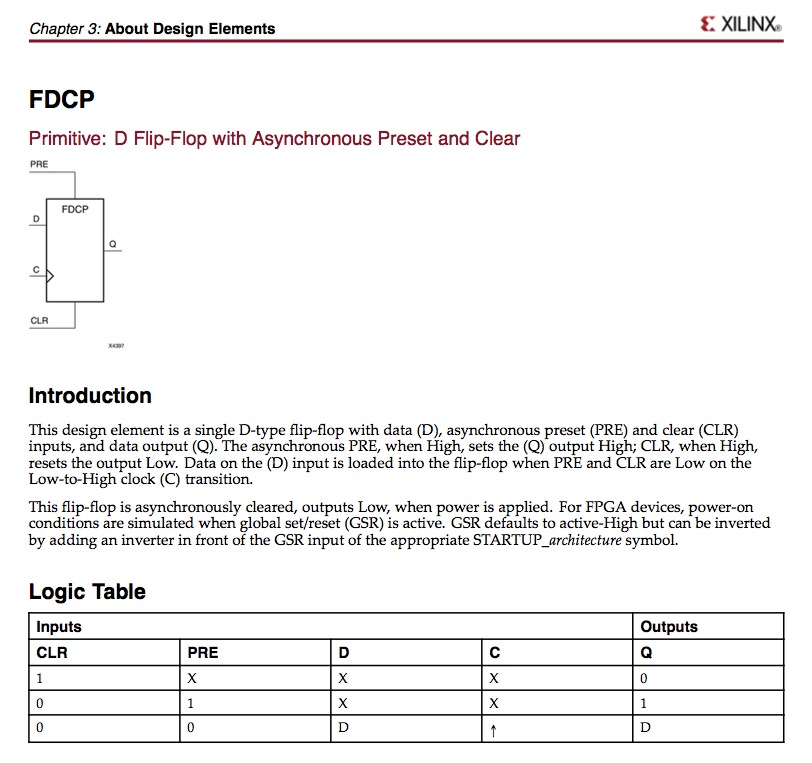

如果你要阅读斯巴达-6图书馆指南的原理图设计,你会发现一个D触发器的异步预置和异步清除都不是由斯巴达6(或更高版本的设备系列)。

您的if语句的第一个条件语句的行为似乎并不代表如果同时重置和集合都是真的话会发生什么。你可以模拟的东西和你可以通过合成绘制的技术之间的区别。

例如,在Spartan-3e中,重置将覆盖该集合:

目标技术中用于映射到寄存器传输逻辑元素的VHDL语言的综合合格子集的约束已在IEEE 1076.6-2004中找到,目前已被撤销,并且可以在ISE用户指南或Vivado设计套件用户指南(ug901)中找到Xilinx。

映射VHDL描述的能力取决于设备家族有一个受支持的目标。

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/45970044

复制相关文章

相似问题