右移(srl)在VHDL Quartus II上出错

右移(srl)在VHDL Quartus II上出错

提问于 2016-06-06 19:06:40

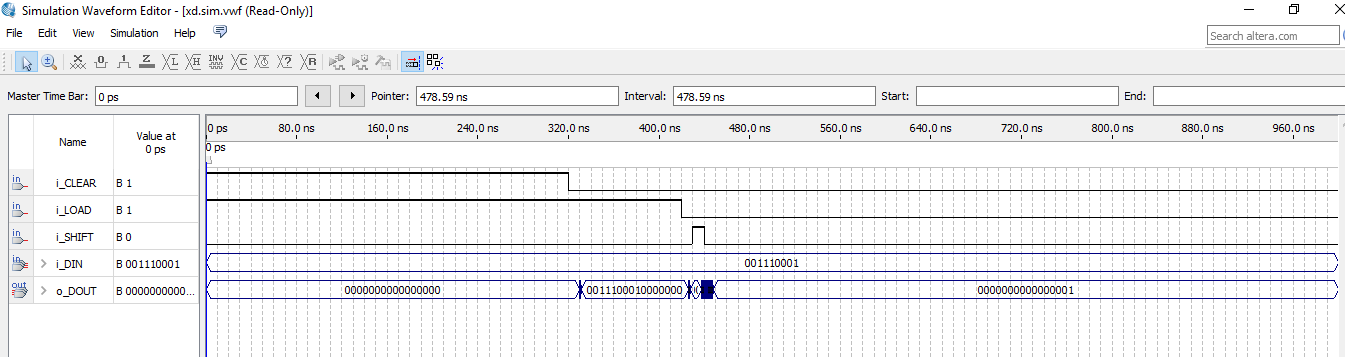

我试着在Quartus II上做一个8位的顺序乘法器。我对所有的块做了所有的模拟,但是其中一个在VWF仿真上出现了错误。sum_reg块,它在很小的时间间隔内做了无限的移位。

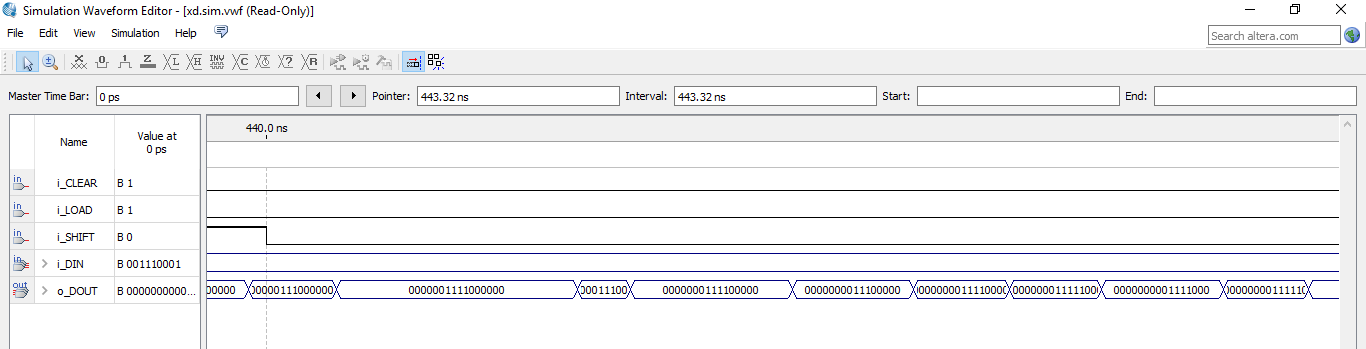

在波形模拟的“深蓝色”部分,在o_DOUT上,这是当位移信号无限大,直到MSB到达LSB为止。下图显示了模拟的深蓝色部分所发生的情况:

有人知道发生了什么吗?

守则如下:

和寄存器(模拟出错的地方):

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

entity sum_register is

port (

i_DIN : in UNSIGNED(8 DOWNTO 0);

i_LOAD : in STD_LOGIC;

i_CLEAR : in STD_LOGIC;

i_SHIFT : in STD_LOGIC;

o_DOUT : buffer UNSIGNED(15 downto 0)

);

end sum_register;

architecture arch_1 of sum_register is

begin

process(i_CLEAR,i_LOAD,i_SHIFT, i_DIN)

begin

IF (i_CLEAR = '1') THEN

o_DOUT <= "0000000000000000";

ELSIF (i_LOAD = '1') THEN

o_DOUT(15 downto 7) <= i_DIN;

ELSIF (i_SHIFT = '1') THEN

o_DOUT <= o_DOUT SRL 1;

END IF;

end process;

end arch_1;回答 1

Stack Overflow用户

回答已采纳

发布于 2016-06-10 19:03:20

您需要在电路中使用时钟信号来实现同步,您需要在实体中输入如下所示:

i_CLOCK : in STD_ULOGIC;在此之后,您将需要使您的过程敏感的时钟:

process(i_CLOCK)你的架构会变成这样:

architecture arch_1 of sum_register is

SIGNAL r_DOUT : unsigned(15 downto 0);

begin

process(i_CLOCK)

begin

IF rising_edge(i_CLOCK) THEN

IF (i_CLEAR = '1') THEN

r_DOUT <= "0000000000000000";

ELSIF (i_LOAD = '1') THEN

r_DOUT(15 downto 8) <= i_DIN;

ELSIF (i_SHIFT = '1') THEN

r_DOUT <= r_DOUT SRL 1;

END IF;

END IF;

end process;

o_DOUT <= r_DOUT;

end arch_1;使用此架构,您将需要一个无符号信号来为您的输出o_DOUT进行分配,这样您就可以再次将您的o_DOUT输出更改为输出类型(而不是缓冲区)。

注:时钟信号必须是相同的所有块!

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/37665070

复制相关文章

相似问题