一阶IIR滤波器的设计

我正在为我的斯巴达-6设计一个简单的一阶IIR滤波器,但我在挣扎于总线宽度和系数量化。

输入数据为16位宽,来自集成ADC,量化噪声是前端噪声的主要来源。

输入信号在大约300 1kHz处被滤波,我想在1Hz、10 1Hz、100 1Hz、1 1kHz、10 1kHz的可调谐频率上实现一阶IIR滤波器:让我们集中讨论1Hz滤波。理论上,我应该能够获得N=log2(300 K)= 18位分辨率。

我计算了滤波器系数:

增益: 3.1416e-6

分子:11

分母:1 -0.999993717

如何处理分数系数?我想把系数乘以2^N,然后剪掉N个LSB,选择N对系数有一个合理的近似。

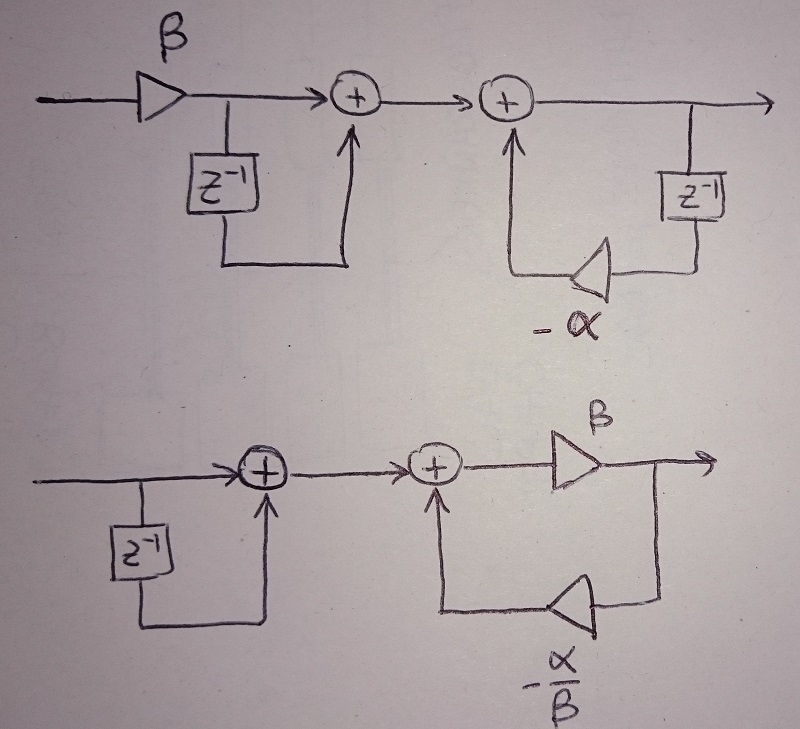

假设我使用这个结构:

使用这种乘法方法,z-1寄存器和y输出的总线宽度应该是多少?

感谢Jonathan的帮助,我仍然需要了解一些事情,所以让我们来实践一下:首先,您认为哪种结构是FPGA实现的最佳结构?

无论如何,假设我乘以:

b = 3.1416e-6 * 2^36 --> 110100101101001111

a = 0.999993716 * 2^17 --> 011111111111111111现在怎么办?:D

回答 1

Stack Overflow用户

发布于 2015-04-24 17:43:43

你把分数系数乘以2**N,就像你想的那样。这给你一个不动点表示与N位二进制小数位。你必须注意跟踪小数部分的宽度。

例如,如果您使用一个系数(1位整数,N位小数)来处理一个输入(16位整数,0位小数),那么您将得到一个17+N位数,它的整数为17位,N位为小数。添加数字时,请确保整数部分对齐.

至于N应该有多大,这取决于你!Matlab的fdatool可以帮助您可视化比特量化对滤波器的影响。Matlab/Simulink是分析量化影响的最好工具,无论它发生在过滤器中,海事组织。

然而,在FPGA中,我会把N放大到乘法器允许的范围内。例如,如果您使用18x18乘法器,只需使用18位(必须有符号)作为系数。如果这还不够,考虑一下预先标度您的输入,更大的乘数输入将花费更多,但也许你有足够的乘法器备用。

还请注意,当截断一个定点数时,您可以舍入以减少您的噪音.只需在截断之前添加0.5,这通常可以在管道上的某个地方以最小的成本完成。

更新

Xilinx有一个不错的IIR滤波的白皮书,它可以帮助你比我更好的解决问题。

否则,我刚刚意识到,你的过滤要求是相当激烈的(1赫兹截止300千赫)。我怀疑你能用18位乘法器实现稳定。您可能需要寻找另一种设计,例如,将输入抽取到一个较低的频率作为第一步操作。

如果需要保持当前需求不变,则必须使用更大的乘法器和加法器。

https://stackoverflow.com/questions/29853221

复制相似问题