如何实现inout参数?

如何实现inout参数?

提问于 2015-01-02 09:21:34

我知道inout参数是什么以及如何使用它们。假设我们有一个inout参数io,并希望创建一个双向静态RAM,如以下代码:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY sram IS

port(

clk : IN std_logic;

wr : IN std_logic;

io : INOUT std_logic;

addr : IN INTEGER RANGE 0 TO 7

);

END sram;

ARCHITECTURE behavioral OF sram IS

TYPE matrix IS ARRAY (0 TO 7) OF std_logic;

SIGNAL mem : matrix;

BEGIN

PROCESS(clk)

BEGIN

IF rising_edge(clk) THEN

IF wr = '1' THEN

mem(addr) <= io;

END IF;

END IF;

END PROCESS;

io <= mem(addr) WHEN wr = '0' ELSE 'Z';

END behavioral;我们可以创建一个sram实例并在其上写入如下代码:

io <= '1' WHEN wr = '1' ELSE 'Z';问:综合工具如何控制多个任务,判断多个驱动程序之间的关系?实现的硬件是什么?

谢谢你的评论和回答..。

回答 2

Stack Overflow用户

回答已采纳

发布于 2015-01-02 10:15:59

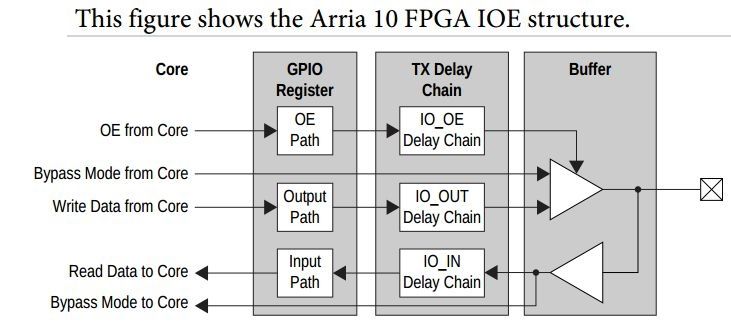

对于典型的FPGA和ASIC设备,只能在IO上实现三态功能,例如Altera Arria 10 FPGA:

因此,对于这样的设备,内部RAM总是使用专用的输入和输出端口来实现,因此不使用任何内部三状态功能。

即使RAM连接到支持三状态的外部IOs,内部RAM块仍然通常使用专用的输入和输出端口创建,因此,通过具有输出启用和三状态能力的输入-输出缓冲区处理到设备上具有三状态能力的引脚的连接。

如果内部设计试图在设备不支持时使用三状态功能或多个驱动程序,则合成工具将生成并出错,通常表示同一网络不支持多个驱动程序。

Stack Overflow用户

发布于 2015-01-02 11:39:55

在Xilinx设备上,原理图是相似的。

这是原始IOBUF的图像:

绿色部分是具有三状态控制的输出驱动程序;蓝色部分是输入驱动程序。完整的IOB (输入/输出块)由几个原语组成:

- IOB寄存器(输入、输出、三状态控制)

- 延迟链

- 将两个乳房组合成差动IOB的导线(**BUFDS)

- 驱动时钟网络的能力(CC时钟能力IOB)

- 拉,拉,拉.

- 司机(IOBUF)

- 针/球(IPAD,OPAD,IOPAD) -这包括ESD保护

合成是如何工作的?

- Xilinx合成工具(XST / Synth)为顶层组件的端口描述中的每条线添加IPAD或OPAD原语。pad只是表示FPGA封装下的物理引脚或球的原语。

- 如果启用了自动添加I/O缓冲区,该工具将添加IBUF、OBUF、IOBUF、IBUFDS、.每个衬垫和顶层端口之间的原语。它使用端口方向(in、out、inout)推断正确的缓冲区类型。如果禁用此选项(默认= on),则必须手动为每个I/O引脚添加缓冲区。在某些情况下,XST会被冒犯:我手工添加了一些带有三状态控制的IOBUF,因此XST拒绝推断缺少的缓冲区。所以我不得不手工添加所有的缓冲区..。

当使用Xilinx时,可以在顶层下使用三状态总线(端口方向= inout)。XST将报告它添加了(虚拟)三状态缓冲区。如果总线的每一个位的方向都有一个明显的方向,并且没有多个驱动程序问题,这些缓冲区就会被裁剪。

这在iSim中不起作用。

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/27739856

复制相关文章

相似问题