如何为原理图创建VHDL测试平台?

如何为原理图创建VHDL测试平台?

提问于 2013-10-15 06:13:20

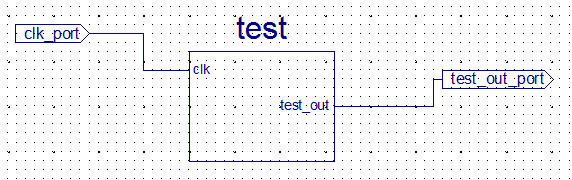

我有一个简单的VHDL模块测试

entity test is

port(

clk: in std_logic;

test_out: out std_logic

);

end test;

architecture Behavioral of test is

begin

main: process(clk)

variable tmp_buffer : std_logic:='0';

begin

if (rising_edge(clk) and tmp_buffer='0') then

test_out<='1';

tmp_buffer:='1';

end if;

if (rising_edge(clk) and tmp_buffer='1') then

test_out<='0';

tmp_buffer:='0';

end if;

end process;

end Behavioral;创建简单的原理图

以及用户约束文件(Spartan-3 XC3S200):

NET "clk_port" LOC = "C5";

NET "test_out_port" LOC = "B5";为示意图创建测试平台(!)

ENTITY main_main_sch_tb IS

END main_main_sch_tb;

ARCHITECTURE behavioral OF main_main_sch_tb IS

COMPONENT main

PORT( clk_port : IN STD_LOGIC;

test_out_port : OUT STD_LOGIC);

END COMPONENT;

SIGNAL clk_port : STD_LOGIC;

SIGNAL test_out_port : STD_LOGIC;

BEGIN

UUT: main PORT MAP(

clk_port => clk_port,

test_out_port => test_out_port

);

clk_port_proc : process

begin

clk_port <= '0';

wait for 10 ns;

clk_port <= '1';

wait for 10 ns;

end process;

-- *** Test Bench - User Defined Section ***

tb : PROCESS

BEGIN

WAIT; -- will wait forever

END PROCESS;

-- *** End Test Bench - User Defined Section ***

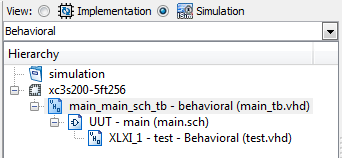

END;这是我的项目结构

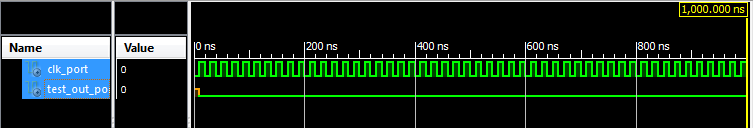

但我还是得到了错误的结果。test_out_port应随着时钟进程的变化而改变。

我找不到好的教程,所以可能太蠢了,但是给我点帮助吧

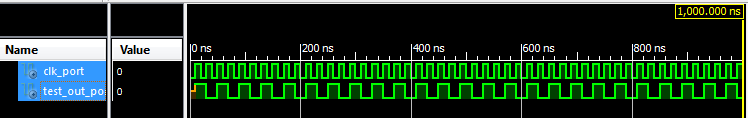

回答 1

Stack Overflow用户

回答已采纳

发布于 2013-10-15 06:47:12

这是愚蠢的错误与‘如果’的陈述。

if (rising_edge(clk) and tmp_buffer='0') then

test_out<='1';

tmp_buffer:='1';

else if (rising_edge(clk) and tmp_buffer='1') then

test_out<='0';

tmp_buffer:='0';

end if;

end if;

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/19374397

复制相关文章

相似问题