ice40时钟延迟,输出时序分析

ice40时钟延迟,输出时序分析

提问于 2020-07-14 23:55:54

我有一个ice40,它驱动ASIC的时钟和数据输入。

ice40用驱动The 40内部逻辑的时钟驱动ASIC的时钟。问题是,上升的时钟触发了its 40的内部逻辑,改变了its 40的数据输出数纳秒后,上升的时钟到达,因此,ASIC在其上升的时钟观察错误的数据。

我已经解决了这个问题,通过使用逆变链来延迟冰山40的内部时钟,而不延迟驱动ASIC的时钟。这样,上升的时钟到达ASIC之前,冰山40的数据输出改变。但这提出了几个问题:

- 是我的策略??使用逆变链延迟ice40内部时钟??一个好策略?

。

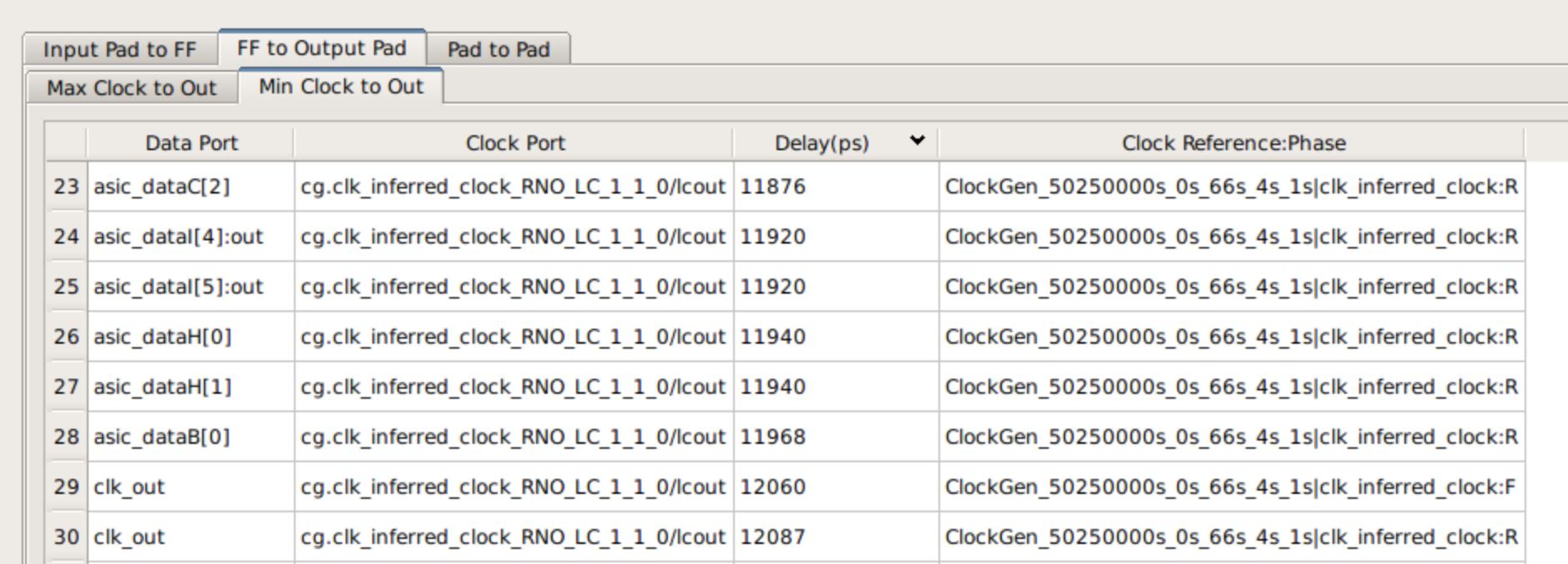

- 用于诊断问题,我使用格子的iCEcube2来分析内部时钟和输出引脚之间的最小/最大延迟:

注意,asic_dataX延迟比clk_out延迟短,这表明了问题所在。

有没有办法从yosys/nextpnr获得这些信息?

谢谢你的洞察力!

回答 1

Stack Overflow用户

回答已采纳

发布于 2020-07-18 08:36:49

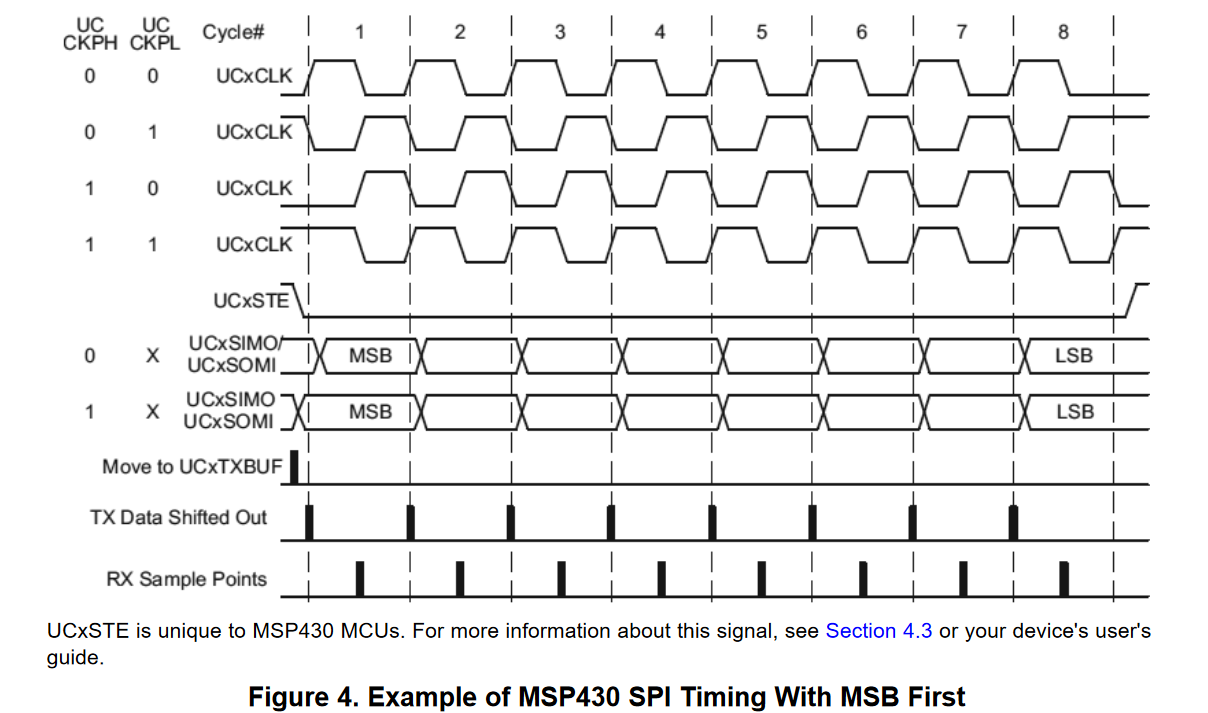

与其修补延迟,我建议使用已建立的技术。例如,SPI简单地将数据记录在一条边界上,并在另一条边界上更改它们:

。

实现这一点的逻辑相当简单。这里是SPI从服务器的一个示例实现:

module SPI_slave #(parameter WIDTH = 6'd16, parameter phase = 1'b0,

parameter polarity = 1'b0, parameter bits = 5) (

input wire rst,

input wire CS,

input wire SCLK,

input wire MOSI,

output reg MISO,

output wire data_avbl,

input wire [WIDTH-1:0] data_tx,

output reg [WIDTH-1:0] data_rx

);

reg [bits:0] bitcount;

reg [WIDTH-1:0] buf_send;

assign clk = phase ^ polarity ^ SCLK;

assign int_rst = rst | CS;

assign tx_clk = clk | CS;

assign data_avbl = bitcount == 0;

always @(negedge tx_clk or posedge rst) begin

MISO <= rst ? 1'b0 : buf_send[WIDTH-1];

end

always @(posedge clk or posedge int_rst) begin

if (int_rst) begin

bitcount <= WIDTH;

data_rx <= 0;

buf_send <= 0;

end else begin

bitcount <= (data_avbl ? WIDTH : bitcount) - 1'b1;

data_rx <= { data_rx[WIDTH-2:0], MOSI };

buf_send <= bitcount == 1 ? data_tx[WIDTH-1:0] : { buf_send[WIDTH-2:0], 1'b0};

end

end

endmodule正如人们所看到的,数据在正边缘被捕获,在负边缘被改变。如果要避免边缘敏感的混合,可以使用双倍时钟代替。

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/62905634

复制相关文章

相似问题