iCE40 Ultra Plus 5k -如何设置PLL (没有丙型GUI工具)(续)

iCE40 Ultra Plus 5k -如何设置PLL (没有丙型GUI工具)(续)

提问于 2021-06-24 09:30:06

在这个question中,我被建议使用现有的库来测试iCE40 Ultra Plus 5k的PLL。

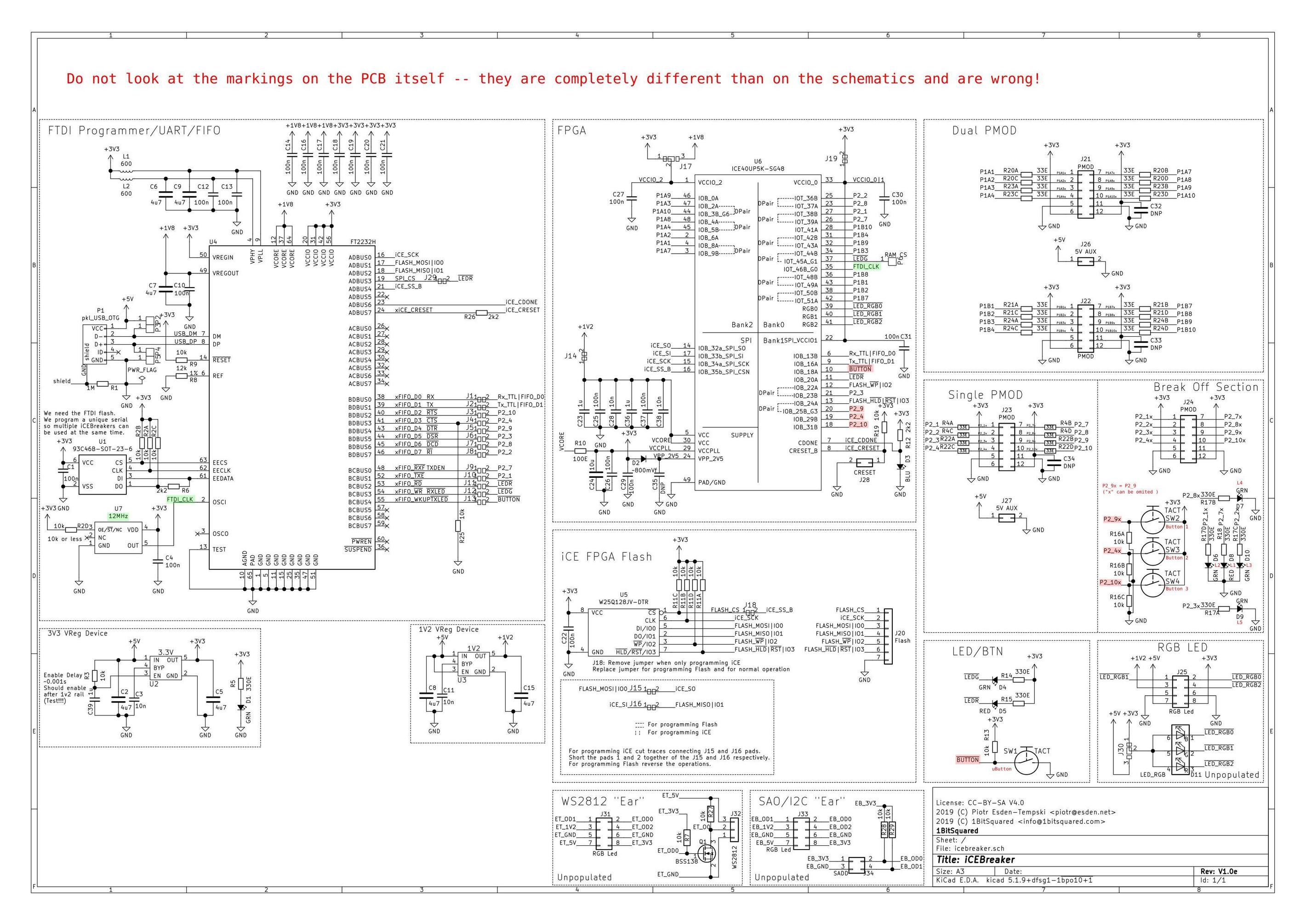

我买了破冰船V1.0e板,看起来是这样的:

外部12 MHz振荡器连接到格格iCE40UP5k (包SG48)的引脚35 (标记为绿色)。

Pin 35具有

IOT_46b_G0功能,类型:DPIO/GBIN0,位于银行:0)。

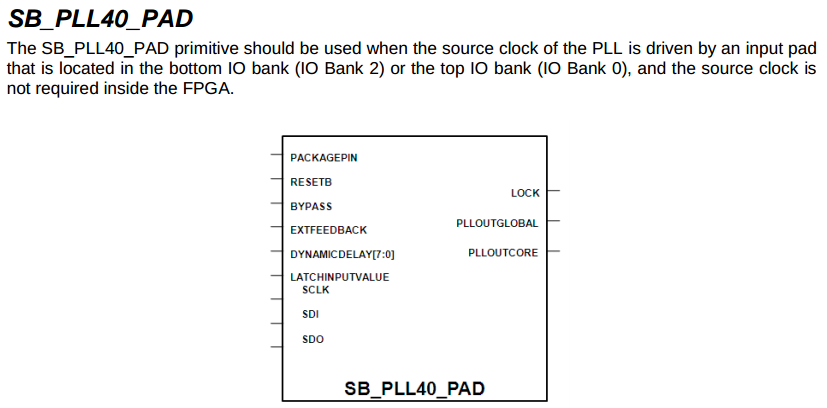

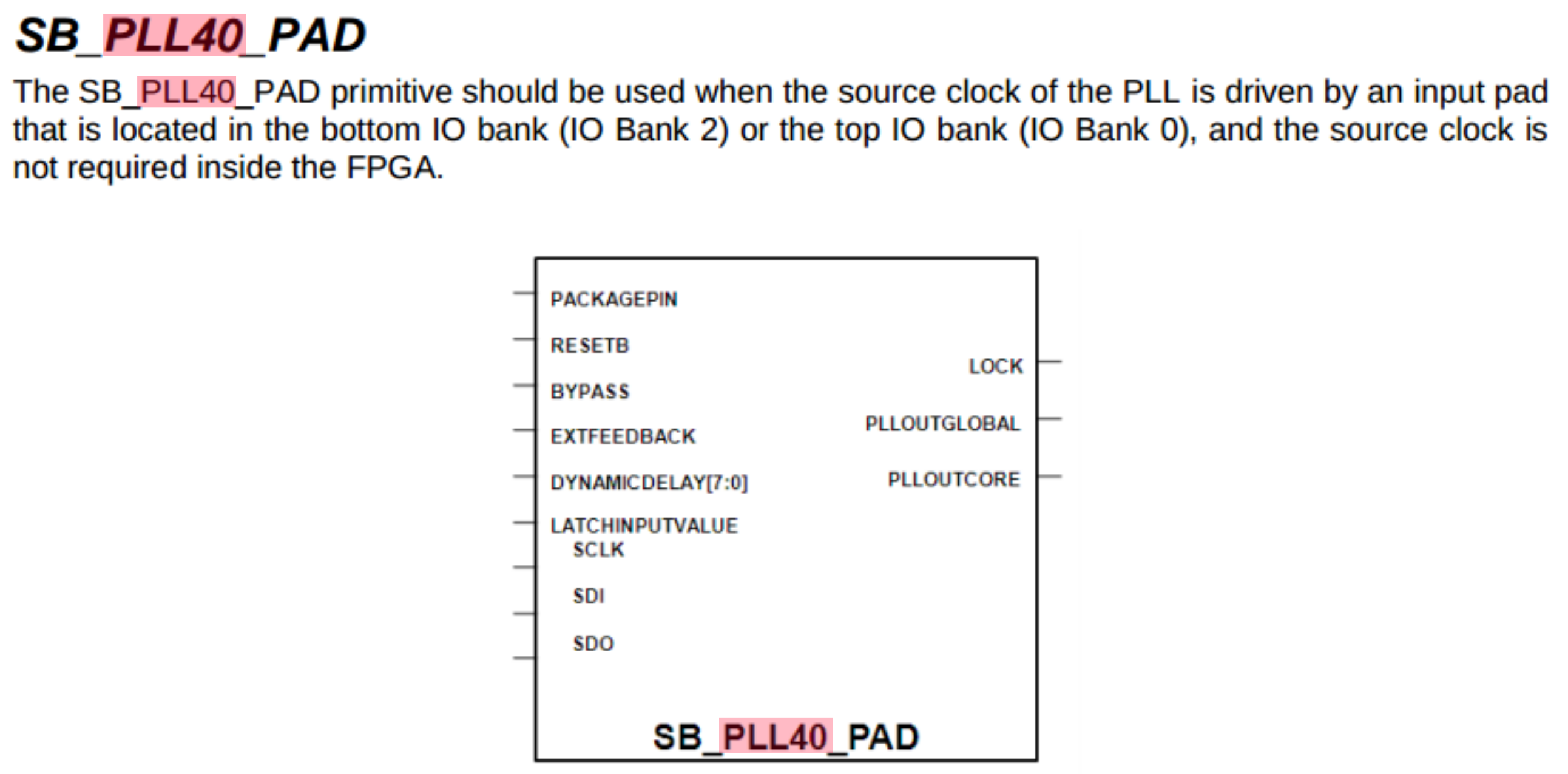

当我在上面发布的库中搜索时,我在第98页上找到了一个不错的原始SB_PLL40_PAD。这个原始人的描述完全符合冰断路器V1.0e的原理图。以下是描述:

请注意,它与上面的引脚描述相匹配!现在,我想在我的VHDL中使用它,所以在开始时,我只为这个原语编写了一个VHDL包装:

-- A:

library ieee;

use ieee.std_logic_1164.all;

-- B:

entity pll_icebreaker is port(

C1_1: in std_ulogic;

C1_2: out std_ulogic;

C1_3: out std_ulogic;

C1_4: out std_ulogic;

C1_5: in std_ulogic;

C1_6: in std_ulogic_vector (6 downto 0);

C1_7: in std_ulogic;

C1_8: in std_ulogic;

C1_9: in std_ulogic

);

end pll_icebreaker;

-- C:

architecture logic_001 of pll_icebreaker is

-- D:

component SB_PLL_40_PAD is port (

PACKAGEPIN: in std_ulogic;

PLLOUTGLOBAL: out std_ulogic;

PLLOUTCORE: out std_ulogic;

LOCK: out std_ulogic;

EXTFEEDBACK: in std_ulogic;

DYNAMICDELAY: in std_ulogic_vector (6 downto 0);

RESETB: in std_ulogic;

BYPASS: in std_ulogic;

LATCHINPUTVALUE: in std_ulogic

);

end component;

begin

-- E:

C1: SB_PLL_40_PAD port map(

PACKAGEPIN => C1_1,

PLLOUTGLOBAL => C1_2,

PLLOUTCORE => C1_3,

LOCK => C1_4,

EXTFEEDBACK => C1_5,

DYNAMICDELAY => C1_6,

RESETB => C1_7,

BYPASS => C1_8,

LATCHINPUTVALUE => C1_9

);

end architecture logic_001;现在,我尝试使用这个makefile目标all编译这个VHDL设计(只使用FOSS工具)。

# A:

file_main = pll_icebreaker

file_pcf = icebreaker

module_top = pll_icebreaker

entity_top = $(module_top)

####################################################################################################

# B:

all:

yosys \

-m ghdl \

-p "ghdl $(file_main).vhdl -e $(entity_top); write_verilog $(file_main).v"

yosys \

-p "synth_ice40 -top $(module_top) -blif $(file_main).blif" \

$(file_main).v

arachne-pnr \

-d 5k \

-P sg48 \

-o $(file_main).asc \

-p $(file_pcf).pcf $(file_main).blif

icepack $(file_main).asc $(file_main).bin我的工具链抱怨它找不到模块SB_PLL_40_PAD

2.2.1. Analyzing design hierarchy..

Top module: \pll_icebreaker

ERROR: Module `\SB_PLL_40_PAD' referenced in module `\pll_icebreaker' in cell `\c1' is not part of the design.

make: *** [makefile:81: all] Error 1怎么会这样?格子技术库不是用Yosys的工具实现的吗?我有点困惑..。我该如何解决这个问题?

回答 1

Stack Overflow用户

回答已采纳

发布于 2021-06-24 12:04:33

看上去我看不懂。点阵技术库提到SB_PLL40_PAD

我用了SB_PLL_40_PAD..。所以当然不能用了!现在它编译了!

因此,我在这里有一个开始,以便创建一个很好的PLL示例,即使用FPGA内已有的硬件!

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/68113130

复制相关文章

相似问题