你就大胆做,我拿LHA7879 给你撑腰(一颗专为电能采集设计的 ADC)

你就大胆做,我拿LHA7879 给你撑腰(一颗专为电能采集设计的 ADC)

云深无际

发布于 2026-04-20 13:35:53

发布于 2026-04-20 13:35:53

好久没见领慧立芯发新品了,不过还好,最近有发,终于档期排到了这里。

不仅仅是 ADC,这次还特意专门为场景做了优化

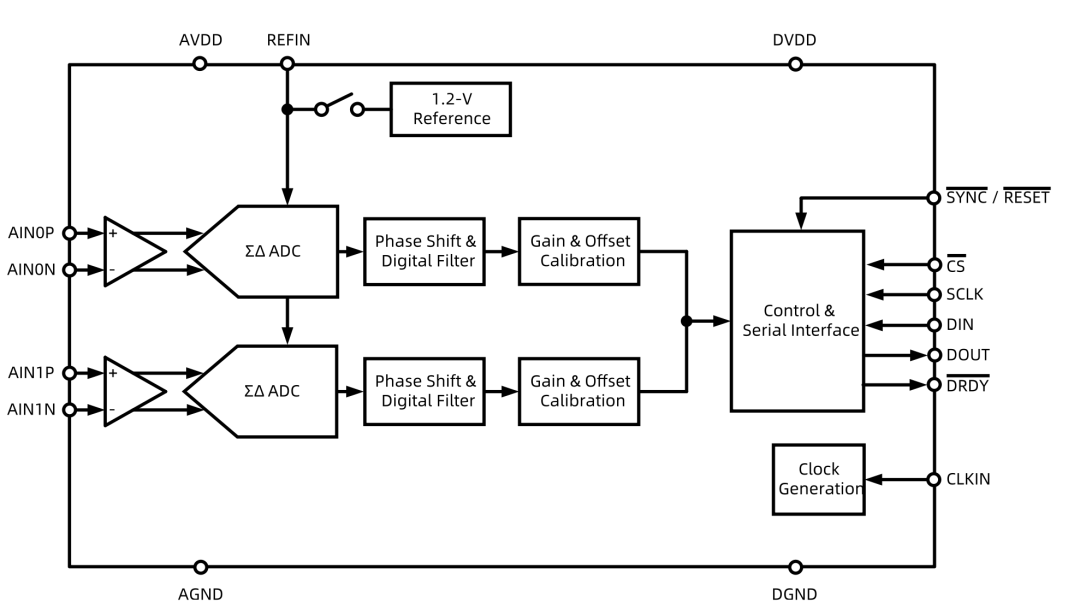

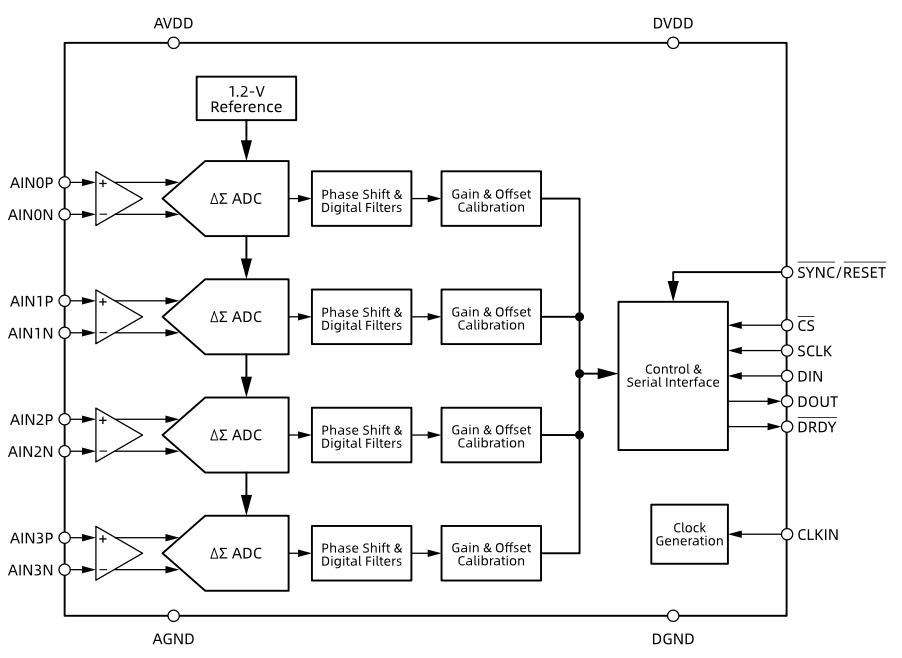

LHA7879-2 是一颗面向电能计量/保护测量场景的双通道、同步采样、24 位 Δ-Σ ADC 前端芯片,它把高增益前置放大、同步采样、数字抽取滤波、相位校准、增益/失调校准、内部基准、CRC 通信保护这些功能集成到了一起,所以很适合直接接电压/电流传感器,组成一个比较完整的测量方案。

“强”在哪里?

手册首页给出的关键卖点是:双通道同步采样差分输入、最高 64 kSPS、PGA 增益最高 128、增益 1 且 4 kSPS 时动态范围 107 dB、THD -100 dB、通道串扰 -120 dB、内部 1.2 V 低漂移参考、支持外部参考、支持 CRC、支持负输入到地以下、3 V 供电下最低功耗 2.1 mW。这些指标组合在一起,说明不是那种单纯追求“超高速”的 ADC,而是一个更偏高动态范围、同步多路、低功耗、强鲁棒性的工业测量型 Δ-Σ ADC。

占位

占位

应用方向很明确:商业/住宅电表、断路器、保护继电器、电能质量监测、电池测试设备、电池管理系统。也就是说,厂家预设的典型场景就是:一边测电压,一边测电流,而且这两个量必须严格同步,再在数字域算功率、能量、相位、谐波、故障特征,这正是“同步采样双通道 ADC”最典型的价值。

从结构上看,这颗芯片每个通道前面都有输入级和 PGA,然后进入各自的 Δ-Σ ADC,再进入各自的“相位偏移 + 数字滤波”,后面还有“增益与失调校准”,最后通过控制与串行接口读出来。上方还有参考源模块,下方有时钟发生和数字接口模块。这个框图其实非常重要,因为:这不是一个裸 ADC 内核,而是一个带完整测量链路补偿能力的 AFE。尤其是“相位校准”和“增益/失调校准”这两块,对电能计量非常关键,因为电压通道和电流通道哪怕有很小的相位差、增益差,最后算有功/无功功率时都会出误差。

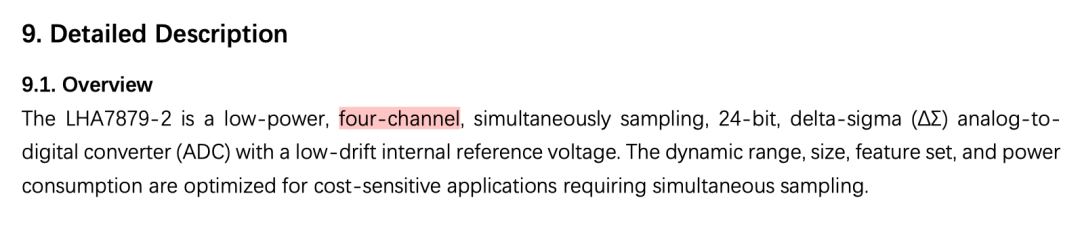

手册大部分地方都写的是 2 通道,首页标题也是 “2 通道、同步采样、24 位 Δ-Σ ADC”,引脚也只有 AIN0P/N 和 AIN1P/N 两组输入;但在详细描述页有一句英文写成了 “four-channel”。

这里是 4 通道

这里是 4 通道

当然也不需要大惊小怪:

因为本来就有 4 通道测量的型号

因为本来就有 4 通道测量的型号

简直了

简直了

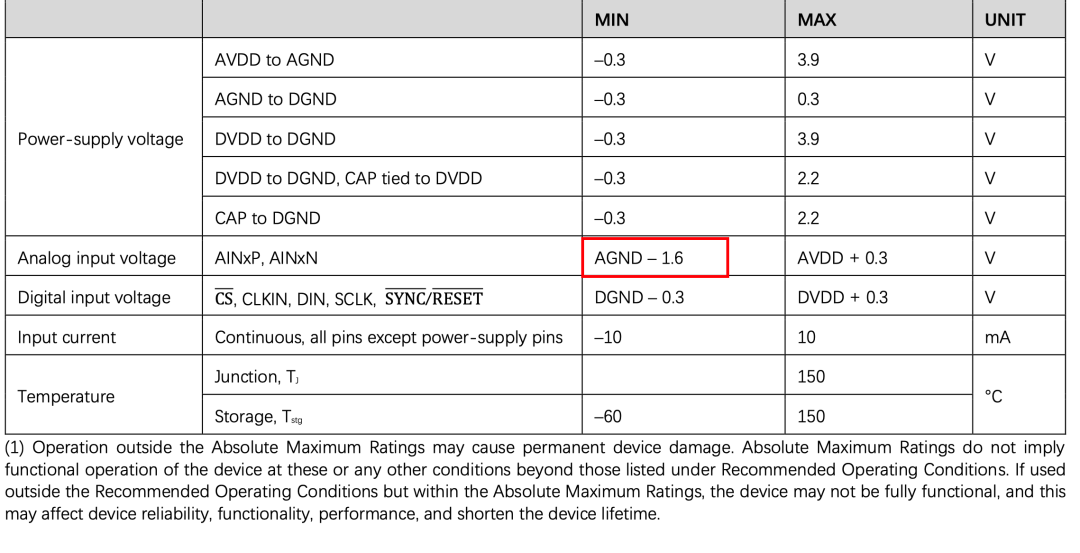

再说输入端;它是差分输入,每个通道一对输入脚。推荐工作条件里给出:输入绝对电压最低可以到 AGND - 1.3 V,最高到 AVDD;差分输入范围是 ±VREF/Gain。

这意味着什么?意思是它不仅能测普通正向差分信号,而且在单电源系统下,它靠内部的负压电荷泵,允许输入端电平略低于地,这对测量围绕地摆动的交流量很有用,特别是电流互感器、Rogowski 线圈、某些分流信号链。

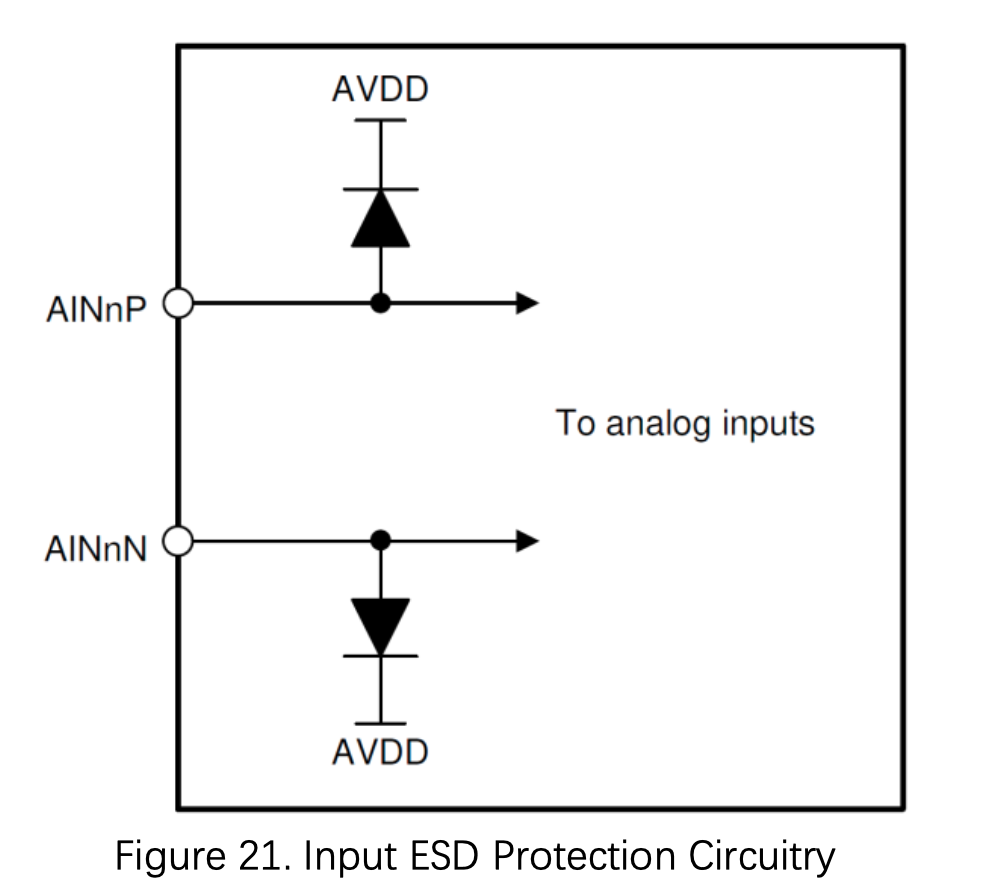

这个“能到地以下”不是一句简单宣传,会直接影响设计的时候前端保护的设计思路;手册专门说了,因为内部有负压电荷泵,不能像很多普通 ADC 那样简单用输入对地的箝位二极管去限制负向过压;对于低于 AGND 的输入,器件内部不是靠对地钳位,而是靠同一套过压路径在反向击穿条件下工作。所以如果前端可能出现较大浪涌、互感器开路过压、瞬态尖峰,外部保护网络一定要仔细设计,不能照搬普通单电源 ADC 的“对地二极管钳位”习惯做法。

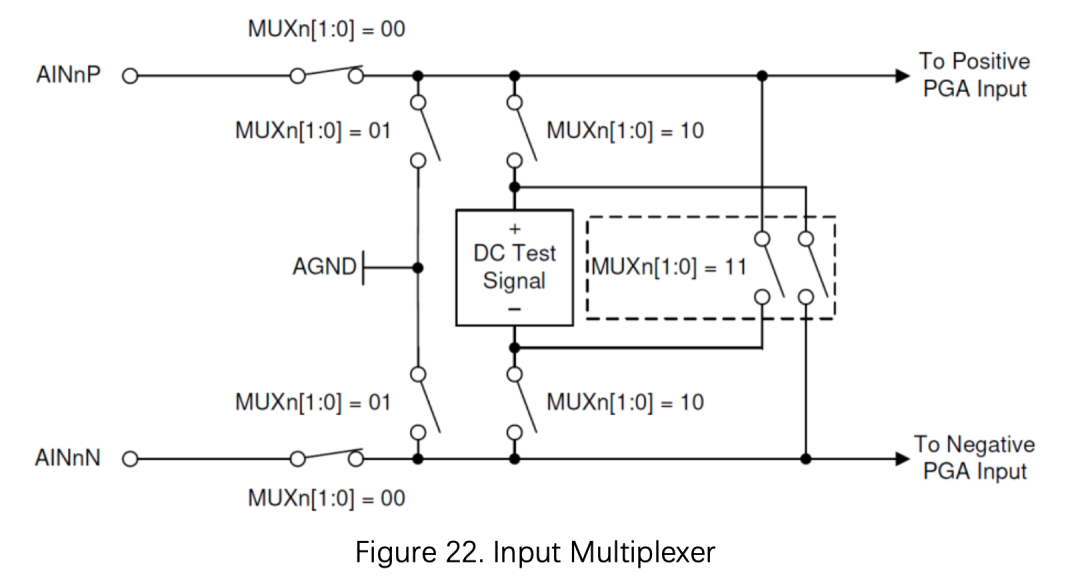

它的输入多路选择器也很实用。每个通道不只是能接外部模拟输入,还可以切到 AGND,也可以切到内部正/负 DC 测试信号;支持比较方便的自检、偏移标定、链路检查。对实际系统来说,这种内部测试路径非常值钱,因为很多时候想区分“传感器坏了”还是“ADC 链路坏了”,内部测试源快速做健康检查。

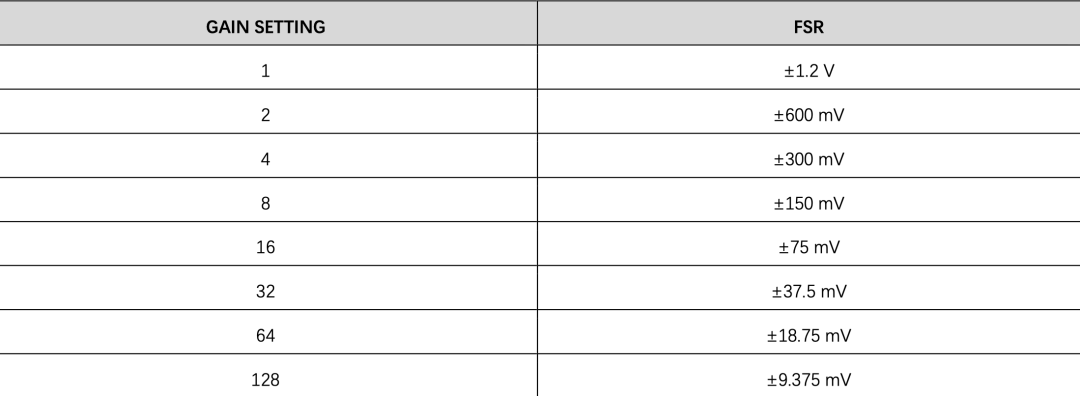

然后是 PGA。这个器件每通道可编程增益有 1、2、4、8、16、32、64、128;它对应的差分满量程范围是:

Gain=1 时 ±1.2 V,Gain=2 时 ±600 mV,Gain=4 时 ±300 mV, 一直到 Gain=128 时只有 ±9.375 mV;这说明它既能直接测相对较大的分压信号,也能直接吃比较小的传感器信号;在增益开大以后,满量程会迅速变窄;如 Gain=128 时只有 ±9.375 mV,这对微弱分流、电桥、互感器二次侧小信号很友好,但也意味着前端任何失调、共模耦合、浪涌余量、传感器零漂都更容易把 ADC 顶满。

输入阻抗方面,典型值给的是 380 kΩ,而且文中还说明 PGA 输入阻抗会主导整个输入特性,并给出与调制器频率相关的表达式。这个数值有两个含义:第一,它不是那种几兆欧到几十兆欧的“近乎理想无限大输入”,所以前级驱动源阻抗不能太大;第二,手册直接提醒,驱动该 ADC 的外部电路输出阻抗要尽量小,否则会恶化增益误差、INL 和失真。换句话说,这颗器件虽然支持“直接传感器连接”,但并不代表随便拿信号源直接怼进去,尤其在高增益和高精度场景下要谨慎。

只能算个基准

只能算个基准

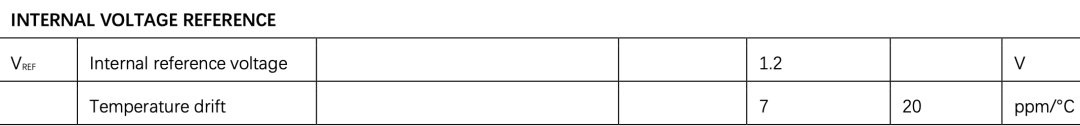

芯片内置 1.2 V 参考,漂移典型 7 ppm/°C、最大 20 ppm/°C;也支持外部参考输入,标称外部参考是 1.25 V。文中还说,外部参考下 ADC 的满量程会按 1.2/1.25 这个比例去缩放,比如外部给 1.3 V 时,满量程会变成 1.248 V / Gain。这说明它内部的量程定义不是“绝对固定 ±1.2V”,而是按参考比例换算出来的。如果追求绝对精度、温漂、长期稳定性,可以考虑外部更好的参考;如果更看重简单和集成度,内部参考已经够用很多工业场景。

这个受温度影响不小

这个受温度影响不小

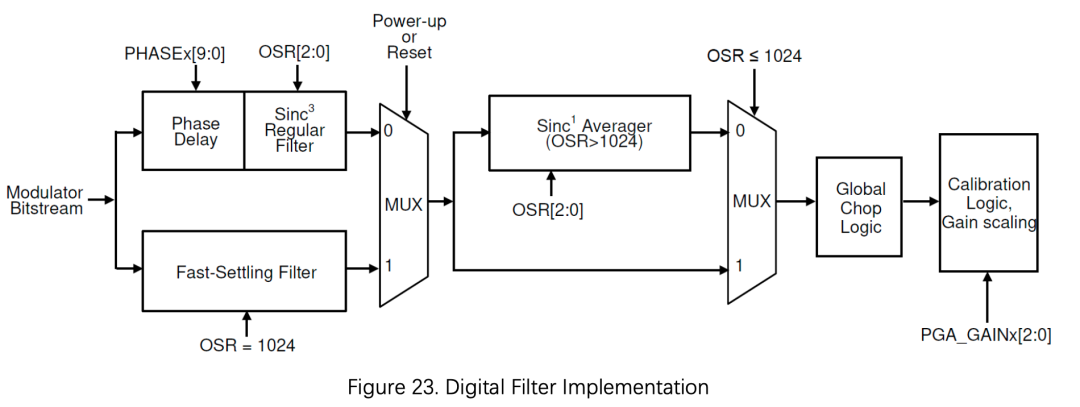

器件是典型 Δ-Σ 调制器 + 数字抽取滤波器 架构。调制器频率 fMOD = fCLKIN / 2,然后数字滤波把高频噪声压下去,并把高速比特流降采样成最终输出数据。它的本质逻辑就是:用过采样换动态范围,用数字滤波换带宽;所以当调低输出速率时,实际上是提高 OSR、增加平均、缩窄带宽,噪声就会下降。

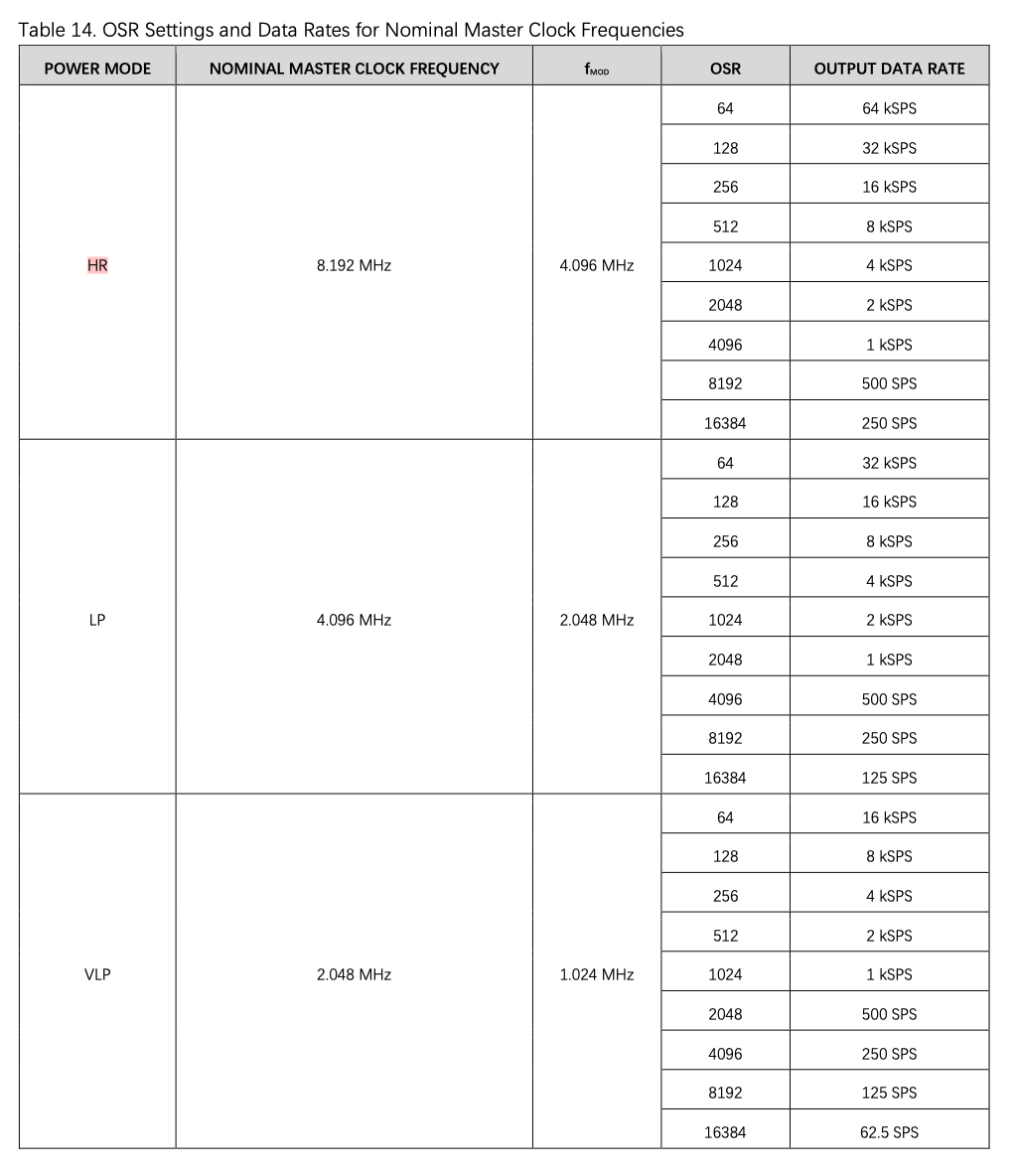

这颗器件有三种功耗模式:高分辨率 HR、低功耗 LP、超低功耗 VLP,对应的典型时钟分别是 8.192 MHz、4.096 MHz、2.048 MHz。在这三种模式下,仍然可以选不同 OSR,于是输出速率分别覆盖:HR 下 250 SPS 到 64 kSPS,LP 下 125 SPS 到 32 kSPS,VLP 下 62.5 SPS 到 16 kSPS。它的关键点不是“模式变了,转换原理变了”,而是模式改变了时钟和偏置,因而在功耗与速度之间折中。

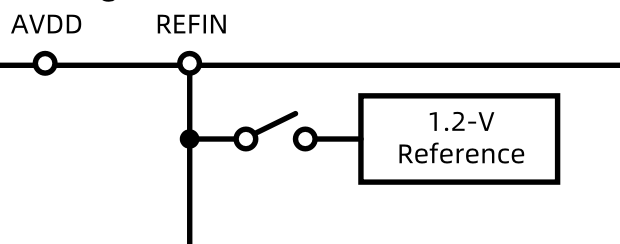

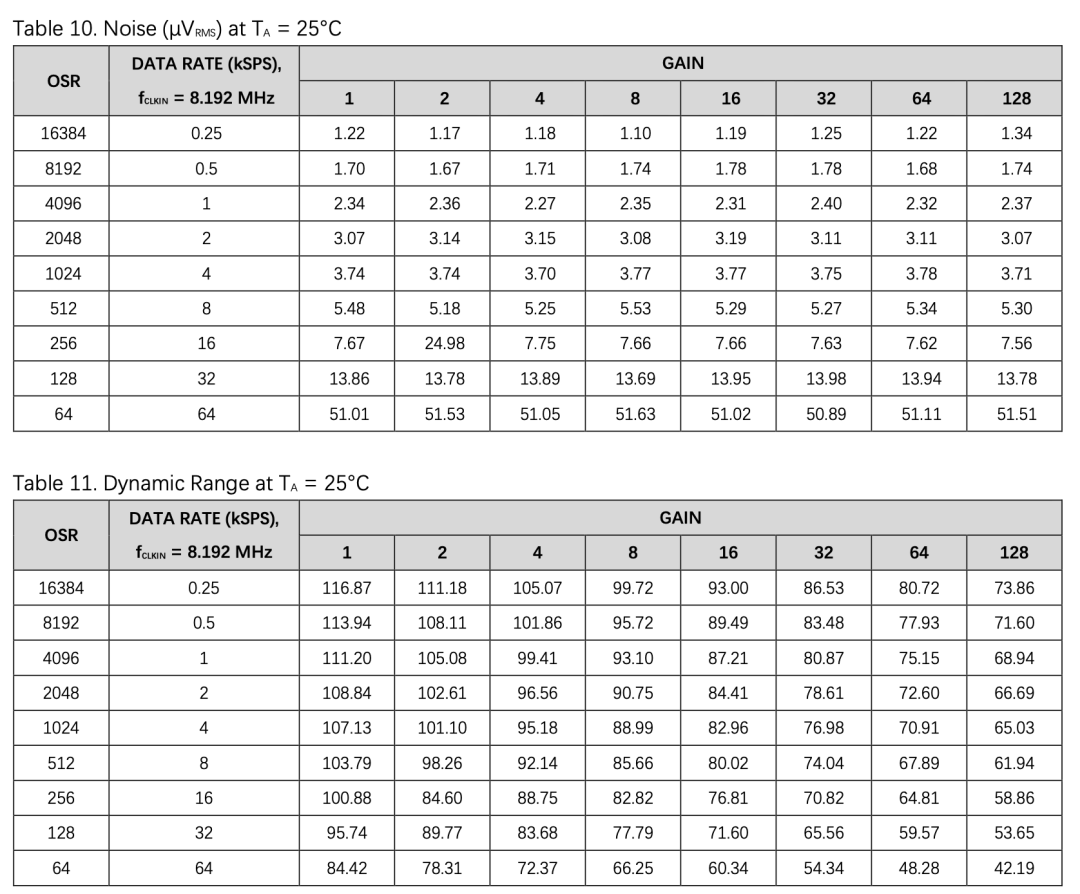

手册说:噪声随 OSR 和 Gain 变化,但与所选功耗模式本身无关;也就是说,只要 OSR 和增益一样,不同功耗模式本质上能达到相同噪声表现,只是对应的数据率会随着时钟不同而缩放。

从噪声表看,最典型的数据是:在 8.192 MHz 时钟、内部 1.2 V 参考下,OSR=1024、也就是 4 kSPS、Gain=1 时输入等效噪声约 3.74 μV RMS,动态范围约 107.13 dB,有效分辨率约 19.3 bit;如果把 OSR 提高到 16384,也就是 250 SPS,那么 Gain=1 时噪声降到约 1.22 μV RMS,动态范围能到 116.87 dB,有效分辨率约 20.9 bit。这非常符合 Δ-Σ ADC 的典型规律:速度降下来,噪声变小,动态范围上去。

滤波器

它的数字滤波器实现也很值得讲;上电或复位后,器件先走一个fast-settling filter,它近似 sinc1,这样前两次转换更快出结果;两次转换之后切到主路径,也就是 sinc3 滤波器。对于 OSR 64 到 1024,直接用 sinc3;对于 OSR ≥ 2048,则变成 sinc3 + sinc1 串联,其中 sinc3 固定在 OSR=1024,额外的更大 OSR 由后面的 sinc1 实现。这个设计的目的很明显:既要在大 OSR 下得到高分辨率,又要控制滤波器实现复杂度和启动行为。

另外:器件不会屏蔽未稳定的数据;也就是说,当切换通道配置、切换增益、使能通道、或者做重同步之后,滤波器需要重新稳定,在稳定时间到来之前读出来的数据可能是不可靠的,而芯片不会自动丢弃这些数据,必须由主控自己处理。这个是很多人用 Δ-Σ ADC 最容易踩的坑之一。(一般数据变化的时候都有这个事情)

滤波器还有一个非常适合电能场景的特性:它在输出数据率的整数倍频率处有陷波;手册还建议,若系统里存在其他周期性干扰过程,尽量把那些干扰频率规划到数据率整数倍附近,这样会被数字滤波器的陷波消掉;反过来,要避免靠近 fMOD 整数倍附近,因为那里可能混叠回带内;比如在做电能采样、PWM 驱动、周期性通信、继电器扫描时,就可以利用这个思路做频率规划。

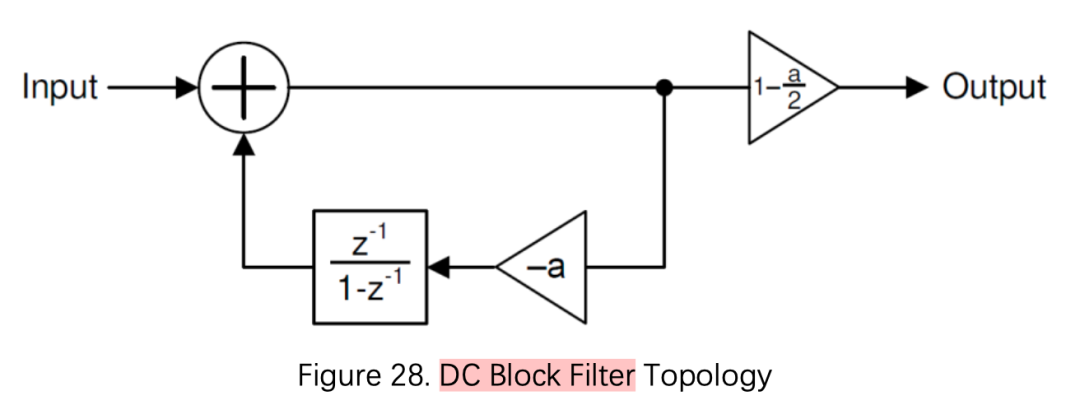

此外它还带 DC block filter,本质是一个可配置高通,用来去除系统失调和低频漂移;这个功能在电流检测、交流计量、去直流偏置场景下很有用,但去直流滤波一定会损伤低频甚至工频附近的幅度。

手册给出的表中,某些配置在 50/60 Hz 下是有通带衰减的,所以如果你的目标就是精确测 50 Hz/60 Hz 幅值与相位,就不能随便把 DC block 打开。

精度指标

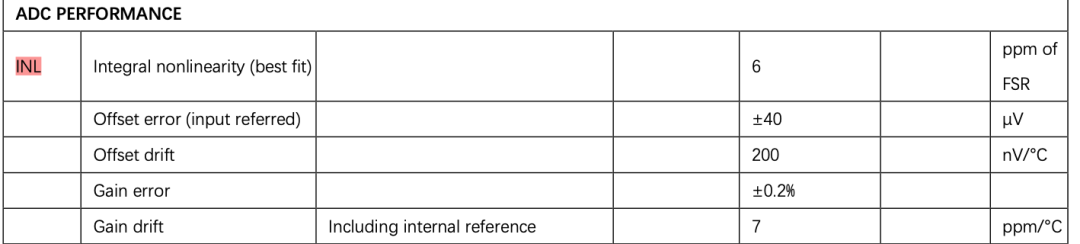

电气特性表给出:INL 6 ppm FSR、输入失调 ±40 μV、失调漂移 200 nV/°C、增益误差 ±0.2%、包含内部参考时增益漂移 7 ppm/°C、CMRR 100 dB、PSRR 对 AVDD 为 60 dB、对 DVDD 为 90 dB。

说明它在工业级集成 ADC 里属于相当能打的水平,尤其是同步双通道、低功耗前提下,已经很适合做计量级采样。

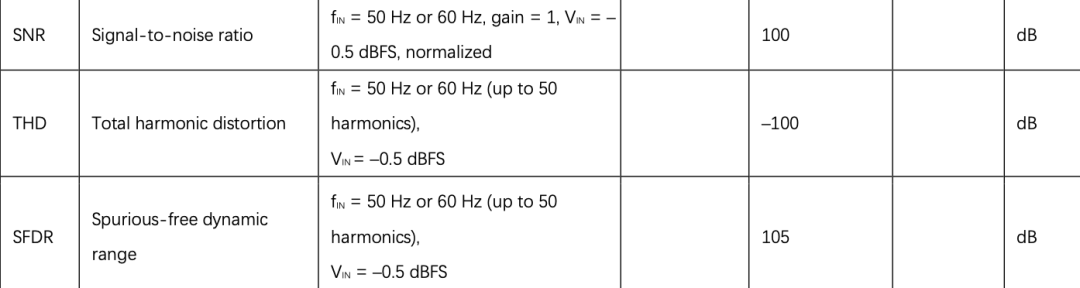

动态交流指标方面,在增益 1、输入 -0.5 dBFS、50/60 Hz 条件下,它的 SNR 100 dB、THD -100 dB、SFDR 105 dB;说明它不只是“直流精密”,在工频和低频交流信号链上也有不错的频谱纯净度,所以用来做功率测量、谐波分析前端、保护测量都比较顺手。

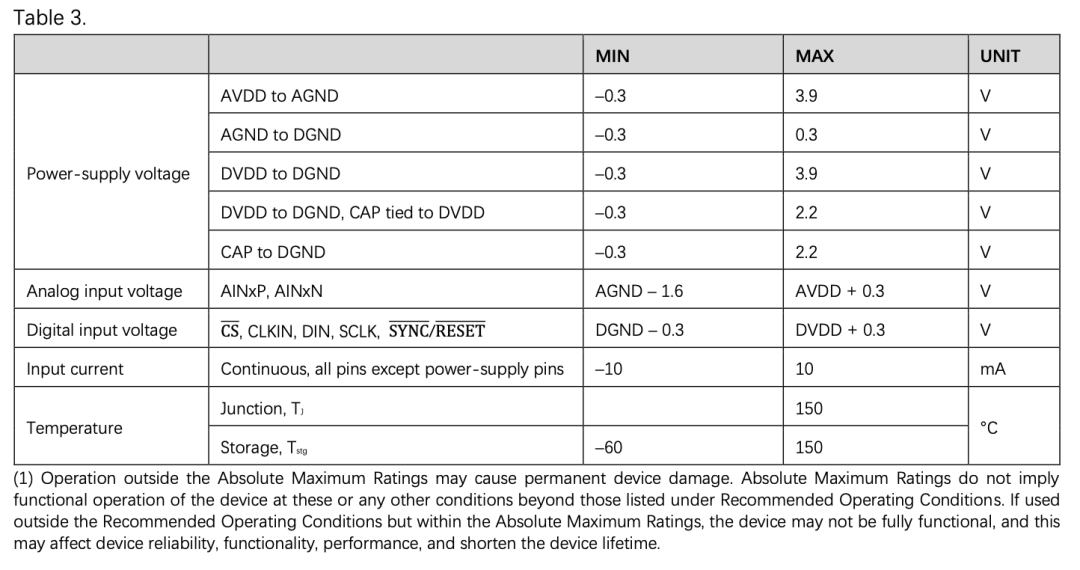

供电方面,它要求模拟和数字供电都在 2.7~3.6 V,如果 DVDD 与内部数字 LDO 的 CAP 脚短接旁路,则数字电源还能用 1.65~2.0 V;其中 AVDD 典型 3 V 时,HR 模式模拟电流约 1.2 mA,数字电流约 0.37 mA;VLP 模式下降到模拟 0.6 mA、数字 0.1 mA,总功耗约 2.1 mW;待机模式更低,只有几微瓦级。这对电池供电或在线监测系统挺友好。

小结

如果要测的是电压 + 电流同步量,比如电表、功率分析、逆变器前端、BMS 支路检测,它很合适。 如果要测的是微弱差分信号,希望片内直接开 PGA,也很合适,但要控制源阻抗,并认真处理过载余量。 如果要做的是超高阻源、超高精度直流计量、纳伏级低漂测量,那它未必是最优,因为它输入阻抗不是无限大,而且本质上还是面向同步工业采样的集成 Δ-Σ AFE。

LHA7879-2 的设计哲学不是“把 ADC 核做到极致”,而是“把双通道同步测量系统中最容易出问题的部分——增益切换、工频性能、滤波、相位、校准、同步、通信可靠性——一并集成好”;所以它特别适合做一个完整测量系统的核心采样芯片,而不是只把它当成一个普通两路 ADC 来看。

信号链-电能采集相关

电能测量本质上不是测“电压”或“电流”,而是测:

如果用非同步采样:电压是 时刻采样,电流是 时刻采样,那算出来的是:

这在有相位差(感性/容性负载)时,会产生系统性误差;那这颗 ADC核心能力是:双通道同步采样+通道间相位校准(Phase Calibration)+增益 / 失调校准。

本质目标:

把“电压通道”和“电流通道”变成一个严格对齐的数学系统

电压通道(Voltage Channel):电网:220V / 110V,通过电阻分压(高压 → mV~V级),然后RC 抗混叠滤波;进入 ADC,AIN0P / AIN0N。

电流通道(Current Channel):分流电阻(Shunt)的线性好,但是有发热、共模问题;电流互感器(CT)的隔离好,但低频差、相位误差;Rogowski 线圈是大电流、无饱和,但是需要积分。

现在系统变成:

传感器 → 简单前端 → LHA7879-2 → MCU → 功率计算

在使用的时候AINxP / AINxN 必须成对使用,即使单端信号,也建议“伪差分”,可以提高 CMRR(100 dB)+抗干扰

输入范围由 PGA 决定:

如:

Gain | 满量程 |

|---|---|

1 | ±1.2 V |

8 | ±150 mV |

128 | ±9.375 mV |

要求传感器输出 × 增益 ≈ 满量程,太小会分辨率浪费

Δ-Σ ADC 内部已经有数字低通,但仍需要模拟前端滤波,简单 RC 就行;因为ΔΣ 会“过采样”,高频噪声会折叠(alias),截止频率:

如:4 kSPS → fc ≈ 500 Hz ~ 2 kHz。

后记

主要亮点还是相位延迟这块,确实是专门为同步设计的,如果对相位要求高也可以考虑;不过现在这些 ADC+一些场景专有的特性也是蛮有新意的设计,至少工作变成了围绕这颗 ADC 做设计了。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-04-20,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录