台积电CoWoS供不应求, 苹果及高通开始评估英特尔先进封装技术

台积电CoWoS供不应求, 苹果及高通开始评估英特尔先进封装技术

芯智讯

发布于 2026-03-20 17:15:19

发布于 2026-03-20 17:15:19

11月17日消息,随着全球对于高性能计算(HPC)及人工智能(AI)芯片需求的持续增长,也推动了对于台积电CoWoS(Chip on Wafer on Substrate)先进封装产能的需求暴涨,虽然台积电持续扩大产能,但依然是难以满足市场需求,成为了限制HPC及AI芯片产能的另一关键瓶颈。这也使得部分客户考虑寻求台积电CoWoS以外的替代方案,其中就包括英特尔的先进封装技术。

据外媒wccftech报道,苹果公司与高通公司在新的职位招聘要求中,都明确列出了需要英特尔的EMIB 与Foveros 等先进封装技术经验,显示多家大厂正寻求CoWoS 以外的替代方案,以应对HPC与AI芯片需求快速增长下的产能瓶颈。

报道显示,苹果公司正在招聘的DRAM 封装工程师,职位要求熟悉CoWoS、EMIB、SoIC 与PoP 等先进封装技术。而高通招聘的数据中心事业部的产品管理主管职位要求,也将Intel EMIB技术列为重要技能之一。

分析认为,由于台积电CoWoS产能目前主要被英伟达、AMD 与大型云端客户包揽,新客户的排单弹性有限,使得其他芯片大厂开始积极评估其他先进封装技术,而在先进封装技术领域,英特尔的技术实力与台积电相当。英特尔高管过此前也多次强调,其Foveros 与EMIB 已取得多家客户的兴趣,并具备量产能力。

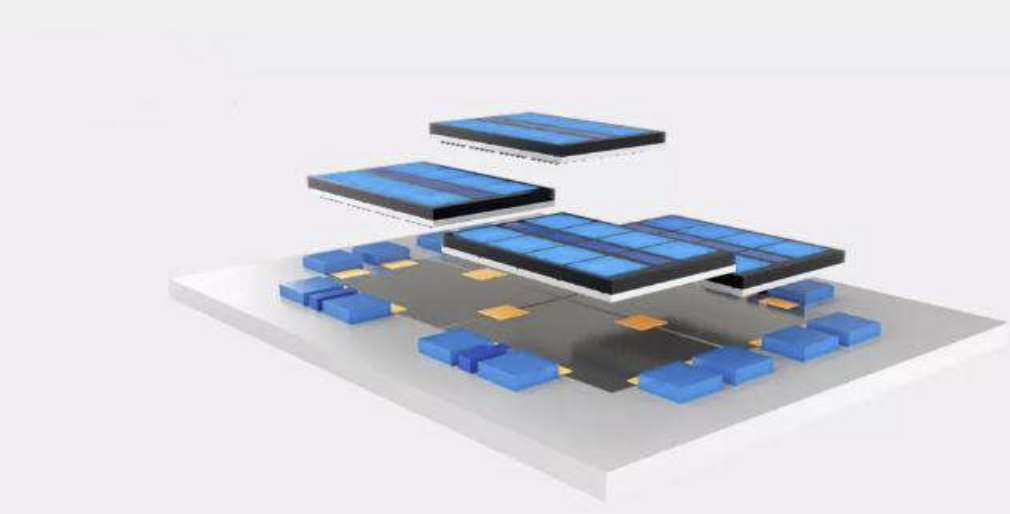

根据英特尔公布的资料显示,其先进封装技术主要分:2.5D 的EMIB(Embedded Multi-Die Interconnect Bridge)以及3D 的Foveros。

其中,EMIB前者采用嵌入式硅桥,能让多颗芯片水平整合,不需大型硅中介层,是英特尔Xeon Max与数据中心GPU Max 系列采用的关键技术。Foveros 则是通过 TSV(硅通孔) 与铜柱进行异质垂直堆叠,使顶层芯片不受基底芯片尺寸限制,适合移动处理器与定制化AI 加速器,包括Meteor Lake、Arrow Lake 与Lunar Lake 均将采用此技术。

业界普遍关注的台积电CoWoS则属于2.5D 大型硅中介层封装,是目前支持最多颗HBM 堆叠、也是AI GPU 最主要采用的技术。与英特尔的两项方案相比,CoWoS 成熟度高、产能规模最大,并拥有广泛的HPC/GPU 客户,因此仍是市场主流。

简单来看,三大技术在设计与定位上各有不同:

EMIB(Intel):2.5D 小型硅桥,适合逻辑芯片与HBM 的横向整合,成本较低、散热佳。

Foveros(Intel):3D 垂直堆叠,可混合不同制程工艺,具有高密度与省电特性。

CoWoS(台积电):2.5D 大型硅中介层平台,是AI GPU 采用最多的主流方案,支持高端HBM 配置。

市场人士指出,虽然CoWoS 仍占据先进封装主导地位,但随着AI、数据中心与定制化芯片需求加速攀升,各大芯片公司都在寻找新的供应链组合。苹果与高通此次在招聘要求上明确点名英特尔技术,被视为产业开始多元布局的信号,也意味着未来先进封装供应链将从单一依赖CoWoS,逐渐走向“双供应模式”的可能。

编辑:芯智讯-林子

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2025-11-18,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读