先进工艺嵌入式存储革命:MRAM崛起

阅读收获

- 洞悉先进工艺下NOR Flash与SRAM微缩瓶颈,避开芯片设计中的面积与功耗陷阱。

- 评估MRAM/ReRAM在嵌入式SoC的商业就绪度,识别边缘AI应用的即时机遇。

- 理解芯粒封装与新型缓存架构的权衡,优化AI处理器成本结构。

- 预判全非易失存储趋势,对存储介质投资与研究方向提供前瞻指导。

全文概览

在先进制程如3nm/5nm时代,芯片设计者面临嵌入式存储的双重危机:传统NOR Flash无法微缩,SRAM缓存面积占比飙升至50%以上,导致成本暴增、漏电严重。这不仅仅是技术瓶颈,更是市场转折点。

Objective Analysis总监Jim Handy和Coughlin Associates总裁Tom Coughlin等专家指出,MRAM/ReRAM已完全就绪,能以1/3~1/4面积取代NOR,提供XIP即时执行和瞬间启动,完美契合边缘AI与IoT低功耗需求。你是否好奇,为什么SRAM的“互连线物理极限”和“信噪比”要求让摩尔定律失效?MRAM如何从末级缓存起步,逐步颠覆“存储三明治”架构,实现全非易失计算?本文拆解这些变革驱动力,揭示独立存储为何暂难触及,而嵌入式市场即将爆发。

👉 划线高亮 观点批注

作者介绍:Jim Handy & Tom Coughlin

1. Jim Handy (Objective Analysis)

- 身份: Objective Analysis 总监及首席分析师。

- 专业领域: 半导体行业,尤其专注于固态存储 (SSD)、闪存 (Flash Memory)、DRAM 及新兴存储技术。

- 行业地位: 以深厚的工程背景和精准的市场预测闻名,能从技术可行性分析市场趋势。他是“新兴存储器”领域权威声音之一,观点常被主流媒体引用。

2. Tom Coughlin (Coughlin Associates)

- 身份: Coughlin Associates 总裁,IEEE Fellow,曾任 IEEE-USA 主席。

- 专业领域: 专注于数字存储技术及其在媒体娱乐、消费电子和企业级数据中心的应用,研究涵盖 HDD、SSD 及存储系统架构。

- 行业地位: 著名的 Flash Memory Summit 会议主席,也是 Storage Visions Conference 的组织者。他擅长分析存储需求端的变化,如 AI、大数据对存储的驱动。

为什么当下新兴存储器会成为关注的重点?

为什么当下新兴存储器会成为关注的重点?

- 主论点:嵌入式存储器已经发生变革

- 这里指的是集成在 SoC(片上系统)或 MCU(微控制器)内部的存储器(SRAM-片上缓存),而不是独立的存储芯片。

- 这意味着变革首先发生在芯片内部,而非外部的独立存储条或 SSD。

- 关键驱动力一:嵌入式 NOR 在先进工艺节点下不可用

- 背景解读: 传统的嵌入式 NOR Flash 在 28nm 工艺节点之后遇到了巨大的制造瓶颈。当逻辑芯片(CPU/MCU)向 22nm、14nm 甚至更先进的 7nm 工艺演进时,NOR Flash 无法随之微缩(Scaling)(后文介绍了原因)。

- 后果: 制造极其昂贵且复杂,导致芯片设计者在先进工艺下无法继续使用传统的 eFlash,被迫寻找替代品(如 eMRAM 或 eReRAM)。

- 关键驱动力二:嵌入式 SRAM 停止微缩

- 背景解读: SRAM(静态随机存取存储器)通常用于 CPU 的缓存(Cache)。它是基于 6 个晶体管(6T)的结构,占据面积很大。

- 后果: 随着芯片工艺越来越先进(如 5nm, 3nm),逻辑电路虽然变小了,但 SRAM 单元的大小几乎缩不下去。这导致 SRAM 在芯片上占据的面积比例越来越大,成本急剧上升,且漏电(Leakage)问题严重。

拆解 SRAM 难以微缩(Scaling Slowdown)的核心原因

1. “拥挤”的 6T 架构(结构瓶颈)

SRAM 单元需要 6 个晶体管 (6T),而逻辑门仅需 2 个晶体管。在极小的空间内塞入 6 个晶体管并保证复杂连线,结构上已极其拥挤,难以同比例缩小。

2. 互连线物理极限(主要原因)

晶体管可缩小,但连接它们的金属导线(互连线)难以同步。SRAM 需要大量接触孔连接电源和信号线。在 3nm 等先进工艺下,金属线间距接近物理极限。线再细电阻飙升导致延迟,线距再近则电容效应引起串扰。为保证连线可靠,SRAM 单元无法跟随晶体管同比例缩小。

3. 稳定性与“信噪比”要求(电气瓶颈)

SRAM 具有强模拟性质,靠内部正反馈环路保存数据。在 5nm/3nm 级别,晶体管尺寸极小,制造偏差(如原子数量差异)会显著影响性能。逻辑电路能容忍一定误差,但 SRAM 晶体管过小易导致读写失败。为确保稳定性,设计者不敢将 SRAM 晶体管做到最小尺寸,必须故意做大,限制了其缩小空间。

嵌入式 NOR Flash 的替代方案(MRAM/ReRAM)在商业生态上已经完全就绪(Ready)。

它传达了以下关键市场信号:

- 技术路径已定: 行业不再纠结于用什么来替代先进工艺下的 NOR Flash,答案就是 MRAM 和 ReRAM。

- 制造障碍已除: 所有的顶级代工厂都能生产,解决了芯片设计公司的后顾之忧。

- 驱动力明确:低功耗需求和边缘 AI 计算需求正在推动这一技术升级,虽然速度相对平稳,但趋势不可逆转。

MRAM/ReRAM 有可能取代SRAM在SOC上被集成吗?

在技术规划路线中,MRAM/ReRAM 将有可能优先取代 Last Level Cache (末级缓存,如 L3/L4) 和 Scratchpad Memory,而非一夜之间替换所有 SRAM。

1. MRAM/ReRAM 替换 SRAM 的驱动力

SRAM 面临“微缩墙”和“漏电墙”。

- 面积优势:

- SRAM 需 6 个晶体管 (6T),难以缩小。

- MRAM (STT-MRAM) 仅需 1 个晶体管 + 1 个磁性隧道结 (1T1R)。

- 结论: MRAM 单元面积仅 SRAM 的 1/3 到 1/4,同等面积可容纳 3-4 倍缓存,对 AI 芯片至关重要。

- 功耗优势:

- SRAM 是易失性,需持续供电,先进工艺下静态漏电惊人。

- MRAM 是非易失性,断电数据不丢失。

- 结论: MRAM 可实现“零待机功耗”,适合待机长的设备。

2. 为何不能“全面替换”?

MRAM 的物理弱点使其暂时无法取代紧贴 CPU 核心的 L1/L2 缓存:

- 速度:

- SRAM 读写极快(皮秒级),能跟上 CPU 高频。

- MRAM 写入速度较慢(10ns-30ns),SOT-MRAM 正在改进但仍不够快。

- 寿命:

- SRAM 读写寿命近乎无限。

- MRAM 有磨损寿命(10^10 - 10^12 次),频繁读写可能导致“折寿”。

为什么 MRAM/ReRAM 会率先在嵌入式设备中广泛使用?

嵌入式设备(尤其是 IoT 和边缘 AI)有两个痛点,MRAM 刚好解决:

- XIP (Execute in Place,片上执行):

- 传统 NAND Flash 必须先把代码读到 DRAM 里才能运行(太慢、太费电)。

- MRAM 速度够快,CPU 可以直接在 MRAM 上运行代码,省去了把数据搬来搬去的过程,既快又省电。

- Instant-on (瞬间启动):

- 由于是非易失的,断电数据还在。设备唤醒时不需要重新加载系统,毫秒级启动,这对于智能手表、工业传感器至关重要。

===

- 价格鸿沟: 独立存储市场(Standalone)是价格敏感型市场。DRAM 和 NAND 经过几十年优化,成本极低(每 GB 几美元)。目前 MRAM 的单位比特成本(Cost per bit)远高于 DRAM/NAND,无法在海量存储市场竞争。

- 嵌入式市场的特殊性: 嵌入式芯片卖的是系统价值。只要 MRAM 能让这颗 MCU 功耗降低 50%,或者能让它用上 22nm 工艺,客户就愿意买单。

一句话总结:在嵌入式领域,MRAM 是“雪中送炭”(解决了造不出来的问题);在独立存储领域,目前它只是“锦上添花”(太贵了)。所以它必然率先在嵌入式爆发。

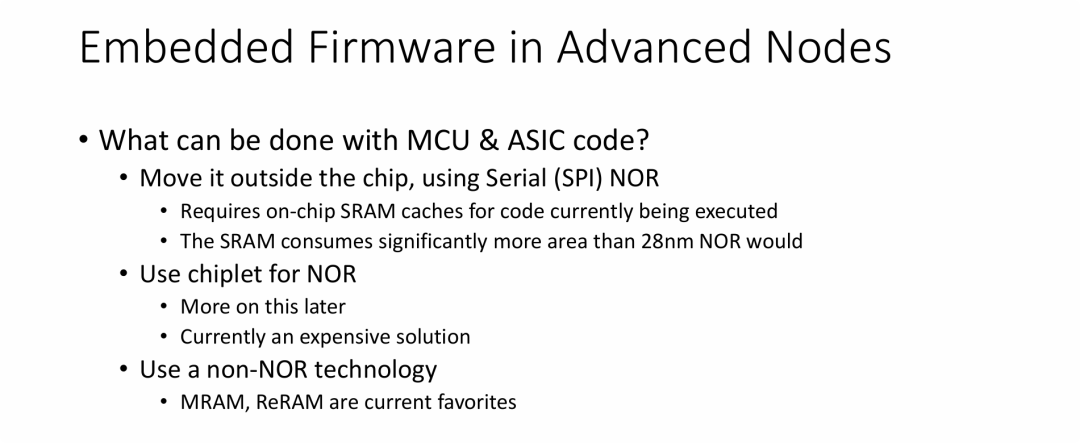

先进节点下的嵌入式固件

先进节点下的嵌入式固件

当芯片工艺先进到无法集成传统 NOR-Flash(SRAM) 时,设计者面临三个选择:

- 方案一:把代码移到芯片外面 (Move it outside the chip, using Serial (SPI) NOR)

- 做法: 逻辑芯片里不放 Flash,在电路板上旁边单独贴一颗便宜的 SPI NOR Flash 芯片。

- 代价 (Requires on-chip SRAM caches): 因为外部 SPI 接口速度慢,为了能跑得快,必须把代码从外面读进来,放到芯片内部的高速 SRAM 缓存里执行(这叫 Shadowing)。

- 致命伤 (The SRAM consumes significantly more area): 这是一个巨大的痛点。前面提到过 SRAM 缩不小。为了存代码而浪费宝贵的先进制程 SRAM 面积,比直接用 28nm 的 NOR 还要占地方,成本极其划不来。

- 方案二:使用芯粒技术 (Use chiplet for NOR)

- 做法: 把一颗先进的逻辑裸片(Die)和一颗老工艺的 NOR Flash 裸片封装在一起(SiP/Heterogeneous Integration)。

- 现状 (Currently an expensive solution): 虽然技术很火,但先进封装(Advanced Packaging)成本高昂,且设计复杂。

- 注: 报告提示 "More on this later",说明后面会有专门章节讲 Chiplet。

- 方案三:使用非 NOR 新技术 (Use a non-NOR technology)

- 做法: 直接在先进逻辑芯片内部集成新型非易失性存储器。

- 赢家 (Current favorites):MRAM 和 ReRAM 是目前的最佳选择。

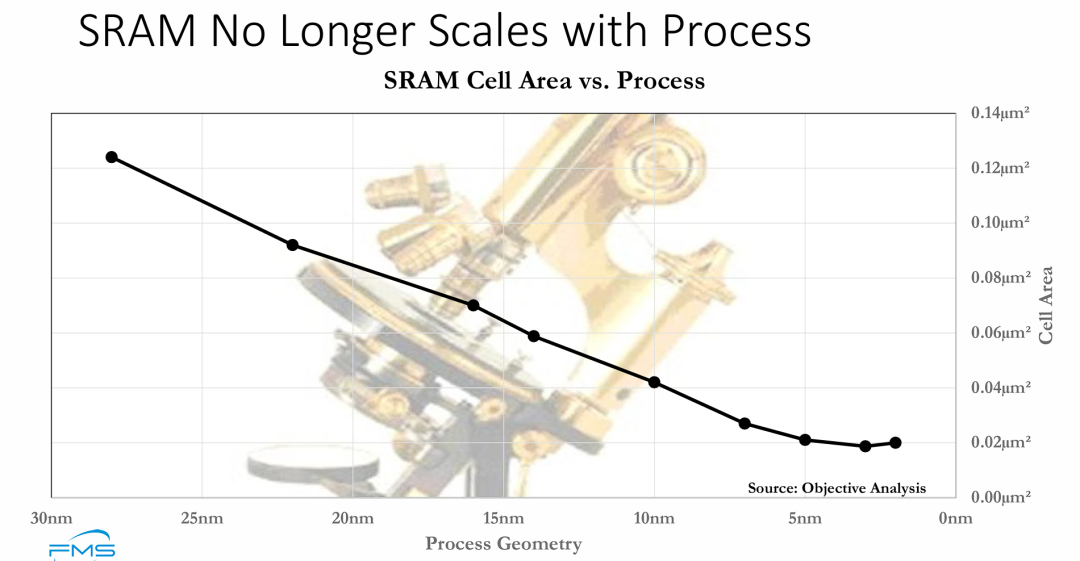

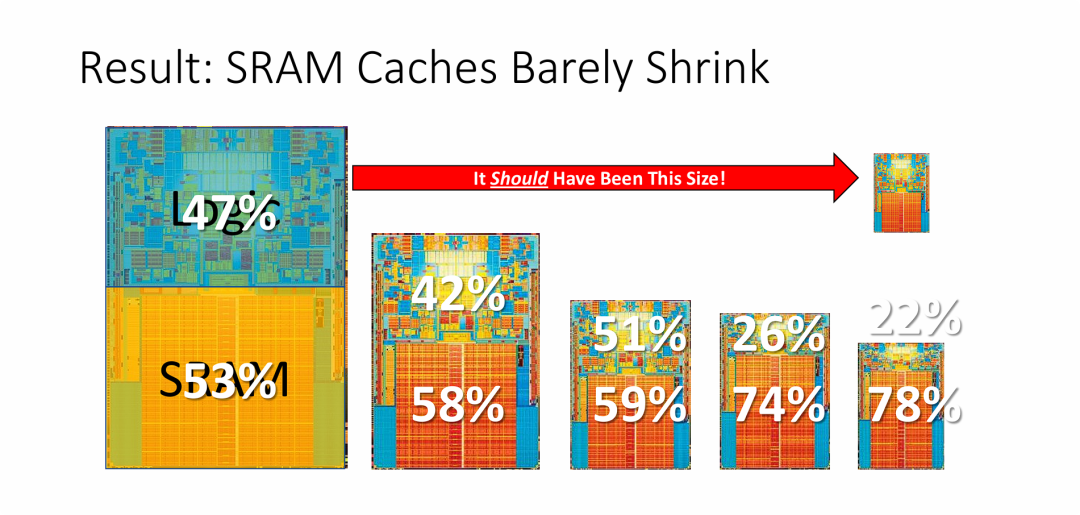

SRAM 单元面积随工艺节点演进的变化曲线

SRAM 单元面积随工艺节点演进的变化曲线

SRAM 的物理微缩(Scaling)已经触底。

它用数据证明了一个残酷的现实:

- 摩尔定律在 SRAM 上失效了: 过去我们通过升级工艺来获得更小的芯片面积,但现在,即使你花巨资升级到 3nm,SRAM 单元的大小和 5nm 相比几乎没有变化。

- “昂贵的死重”: 由于逻辑电路(Logic)还在变小(先进工艺也面临挑战,但可以通过核心数/并行计算来扩展计算能力),而 SRAM 不变,SRAM 在芯片上占据的面积比例会被动地越来越大。对于缓存密集型芯片(如 AI 处理器、CPU),这意味着芯片成本不仅没降,反而因为工艺复杂度的提升而剧增。

- 过去: 每一代新工艺(如 N 到 N+1),逻辑电路密度提升 1.8-2 倍,SRAM 密度也能提升 1.6-1.8 倍。

- 现在(3nm/5nm): 逻辑电路密度依然提升 1.6 倍以上,但 SRAM 密度提升可能只有 1.1-1.2 倍,甚至几乎停滞。

后果: 以前一颗 CPU 芯片中,SRAM(缓存)可能只占 30% 面积;而在最新制程下,SRAM 可能会占据 50% 甚至更多 的面积。这使得芯片成本极其昂贵(因为你花大价钱买 3nm 工艺,却有一半面积是缩不小的旧技术)。

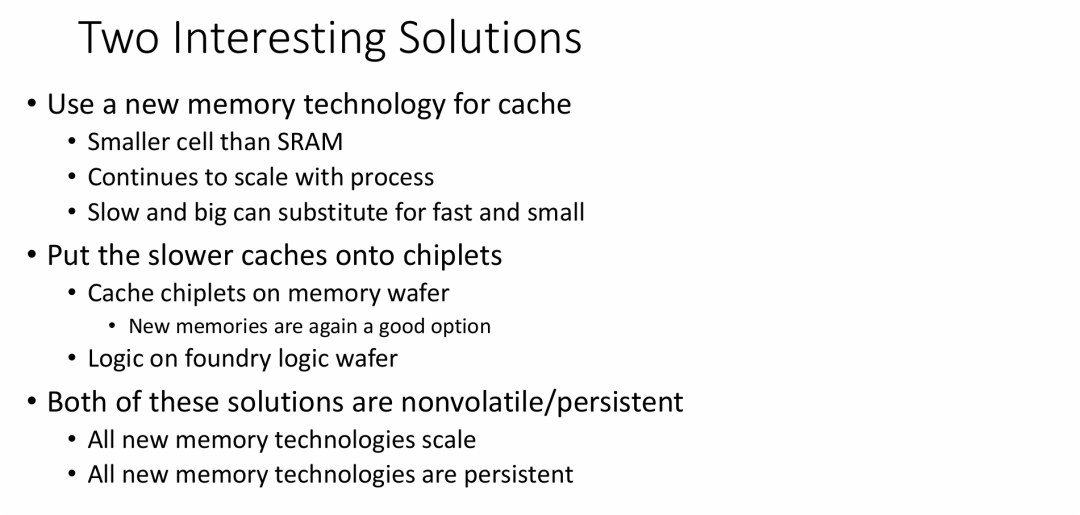

应对危机的两个架构级解决方案

应对危机的两个架构级解决方案

方案一:使用新型存储技术直接做缓存

- 更小的单元: MRAM/ReRAM 单元面积远小于 6T SRAM(仅为 1/3 ~ 1/4)。

- 持续微缩: 该技术在先进工艺下仍能缩小,无 SRAM 物理瓶颈。

- 架构权衡: “慢而大”可替代“快而小”。MRAM 虽慢但密度高,同面积容量更大。一个更大但稍慢的缓存(提高命中率)常比极快但很小的缓存(命中率低)带来更好系统性能。

方案二:将较慢缓存移至芯粒

- 分离制造:

- 缓存芯粒: 使用专门优化的存储器工艺(成本更低)制造缓存芯粒,新型存储器是理想选择。

- 逻辑芯粒: 昂贵先进逻辑工艺仅用于 CPU/GPU 核心,不用于占地缓存。

- 此法利用先进封装技术,实现“好钢用在刀刃上”。

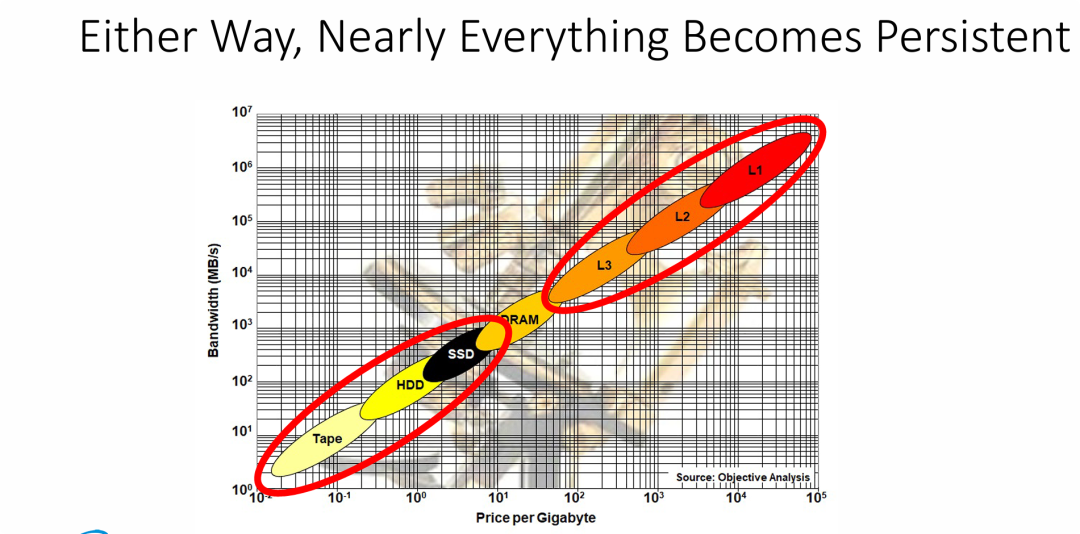

未来趋势:大部分存储器都将演进为持久化

未来趋势:大部分存储器都将演进为持久化

图非常耐人寻味,它揭示了一个潜在的 “存储三明治” 危机与机遇:

- DRAM 成了唯一的“易失孤岛”:

- CPU (L1/L2/L3) 是非易失的(因为换成了 MRAM)。

- 硬盘 (SSD/HDD) 是非易失的。

- 夹在中间的 DRAM 依然是易失的。这在系统架构上显得非常突兀。

- 系统设计的颠覆性影响:

- Instant On (瞬间唤醒): 如果你的 L1/L2/L3 缓存掉电不丢数据,CPU 几乎可以在通电瞬间恢复“思考”,无需从硬盘重新加载数据到内存,再预取到缓存。

- Check-pointing (断点续算): 对于 AI 计算或高性能计算,如果系统崩溃,无需重头算起,因为计算现场(Context)就保存在 L1/L3 的 MRAM 里。

- 未来的暗示: 虽然这张图没明说,但它暗示了下一步的终极目标——取代 DRAM。如果有一天 MRAM/ReRAM 足够便宜且够快,能把中间那个黄色的 DRAM 也吃掉,那么计算机将实现全非易失性 (All-Persistent) 计算。那是存储技术的圣杯。

延伸思考

这次分享的内容就到这里了,或许以下几个问题,能够启发你更多的思考,欢迎留言,说说你的想法~

- MRAM/ReRAM在取代L1/L2高速SRAM前,能否通过架构优化(如增大缓存提升命中率)实现系统级性能跃升?

- 嵌入式市场MRAM爆发后,独立DRAM/NAND的价格敏感性将如何制约其向大容量存储扩展?

- 全非易失计算时代,系统“瞬间唤醒”和断点续算将如何重塑AI与高性能计算的架构设计?

原文标题:Is the World Ready for New Memories?[1]

Notice:Human's prompt, Datasets by Gemini-3-Pro

#FMS25#新兴存储技术趋势

---【本文完】---

👇阅读原文,搜索🔍更多历史文章。

丰子恺-护生画集-生离死别

- https://files.futurememorystorage.com/proceedings/2025/20250806_OMEM-201-1_Handy-2025-08-03-23.50.48.pdf ↩

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-03-03,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录