来自瑞萨的 FGA 基准源(ISL21009)

今天发一个有趣的东西,还是基准源,但是是和我们见到的原理不一样的东西。最早是闲鱼一个 DIY 的六位表里面的基准源,瞎几把做:

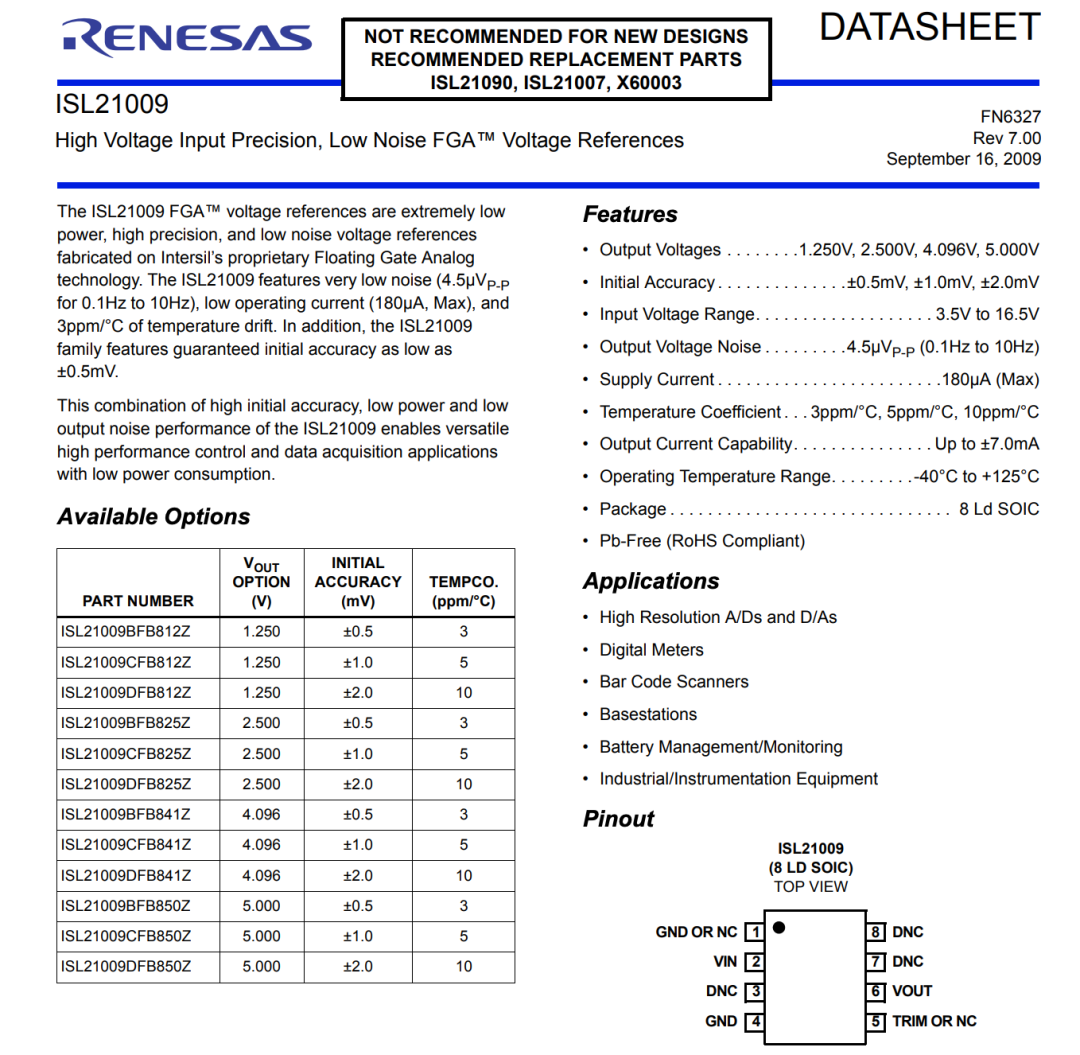

就是这个型号了

就是这个型号了

价格大概要几十块!!!

image-20260225182151394

ISL21009 = 浮栅模拟(FGA)高精度电压基准

先看点参数

初始精度:±0.5 mV

温漂:3 ppm/°C(最高等级)

0.1–10 Hz 噪声:4.5 µVpp

供电电流:典型 95 µA

输出能力:±7 mA

输入电压:3.5 V – 16.5 V

总之:

这是一个低功耗 + 低漂移 + 低 1/f 噪声 的精密基准

FGA 技术到底是什么?

在第15页 Applications Information 里有说明(FGA Technology)

传统的有带隙基准,以及齐纳基准,它们的问题:温漂来自 PN 结,电流较大,低频噪声较高。

FGA(Floating Gate Analog)做法

它是:

在制造时向浮栅注入精确电荷,直接“编程”参考电压。

等效理解:

Vref ≈ 存储电荷 / 栅电容

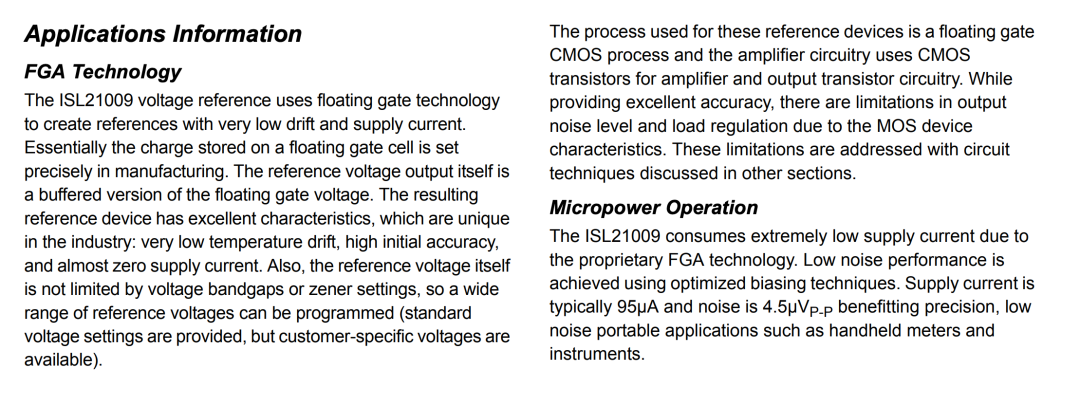

优点是极低漂移(几乎不依赖温度),拥有超低静态电流,可任意电压定制,缺点是MOS 输出级 → 驱动能力有限,以及对 X-ray 敏感(会改变浮栅电荷)。

这样的场景就有可能坏掉

这样的场景就有可能坏掉

初始精度±0.5 mV @ 2.5 V,相对误差:

0.5mV / 2.5V = 0.02%

≈ 200 ppm,这对于 16bit ADC 是够的,对于 20bit 需要校准。

温漂 3 ppm/°C,这个温度跨度 -40 → 125°C = 165°C

漂移总量:

3 ppm × 165 = 495 ppm

对 2.5V:

2.5V × 495 ppm ≈ 1.24 mV

如果做 20bit 系统(1 LSB ≈ 2.4 µV):

1.24mV ≈ 516 LSB

所以:

高精度系统必须做温度补偿

低频噪声是0.1–10 Hz = 4.5 µVpp,这是 flicker noise 区域。

等效 RMS≈ 0.75 µV RMS,如果接 24-bit ADC,LSB (2.5V, 24bit):2.5V / 2^24 ≈ 0.15 µV;所以:噪声 ≈ 5 LSB(对 24bit 会限制 ENOB)

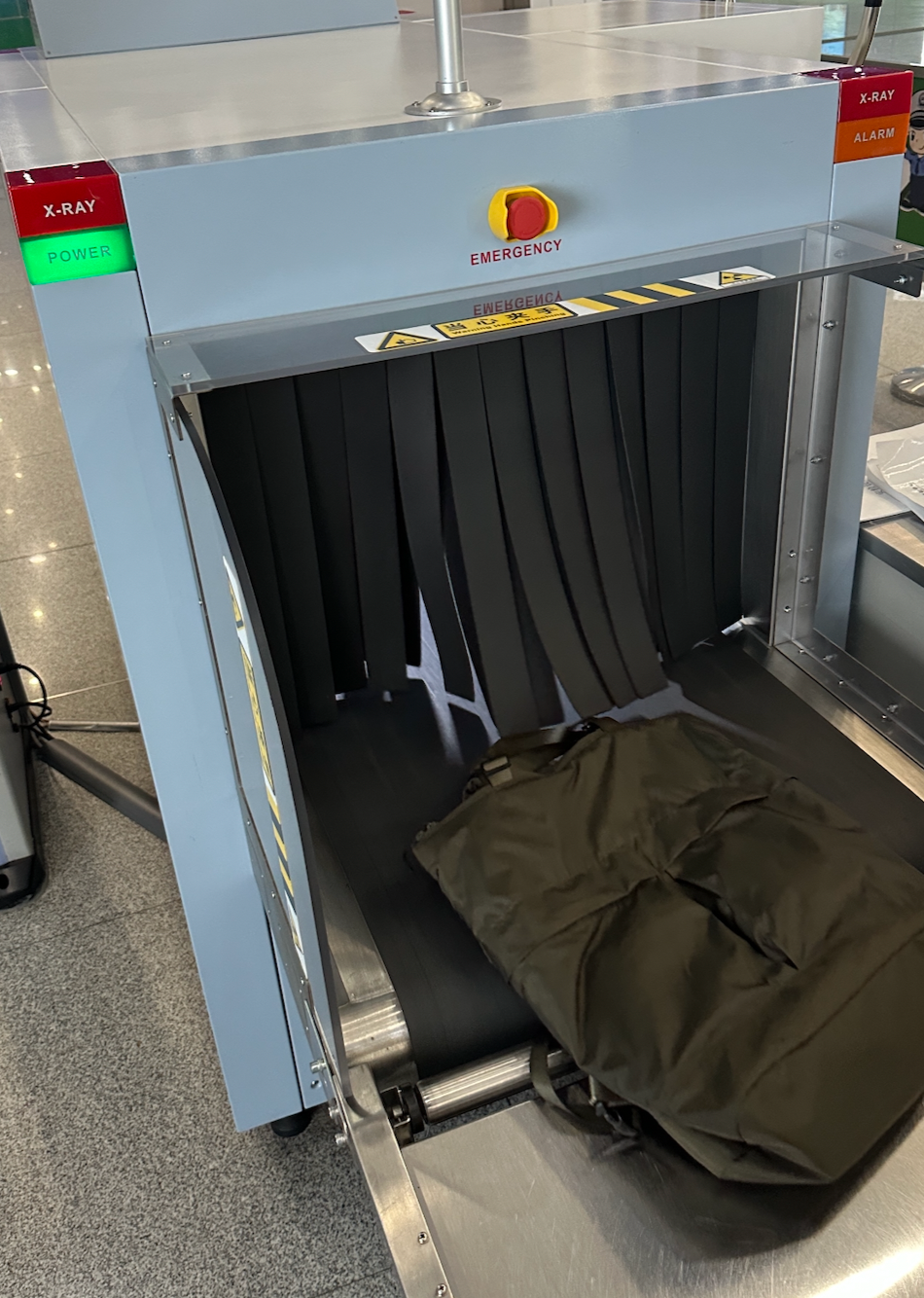

噪声与输出电容问题

在第16页提到:

输出级不擅长驱动大电容

如果 Cout > 0.001µF,推荐 RC 网络

网络:

Vout -- 2kΩ -- 10µF

|

0.01µF

这是一个输出隔离电阻 + 降噪电容网络,作用是降低高频噪声,改善瞬态响应,防止振荡这和我们设计 ADC 参考端 RC 滤波非常类似。

PSRR(供电抑制)

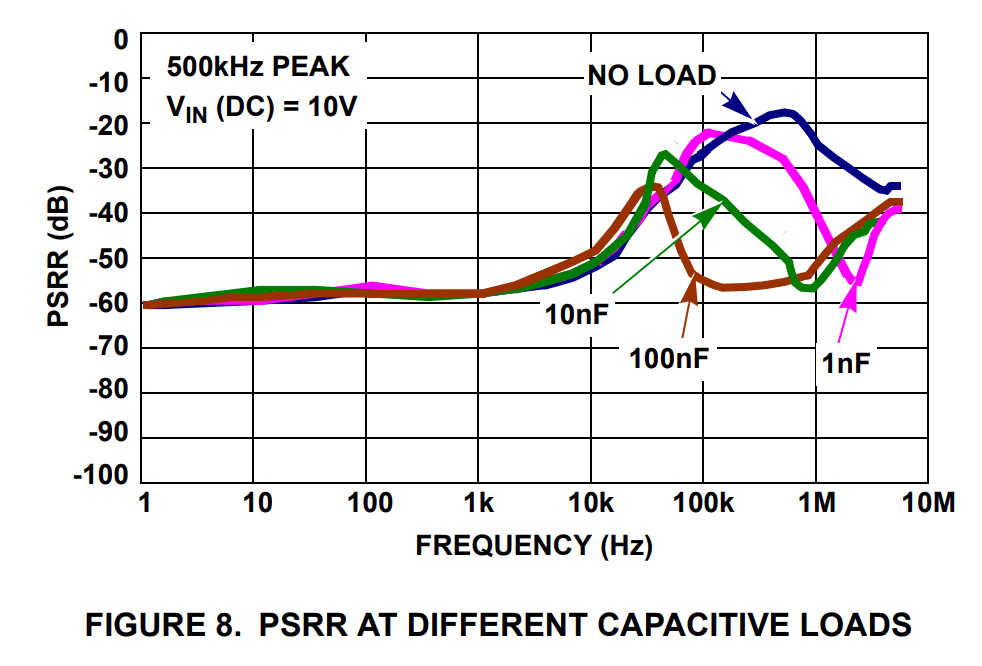

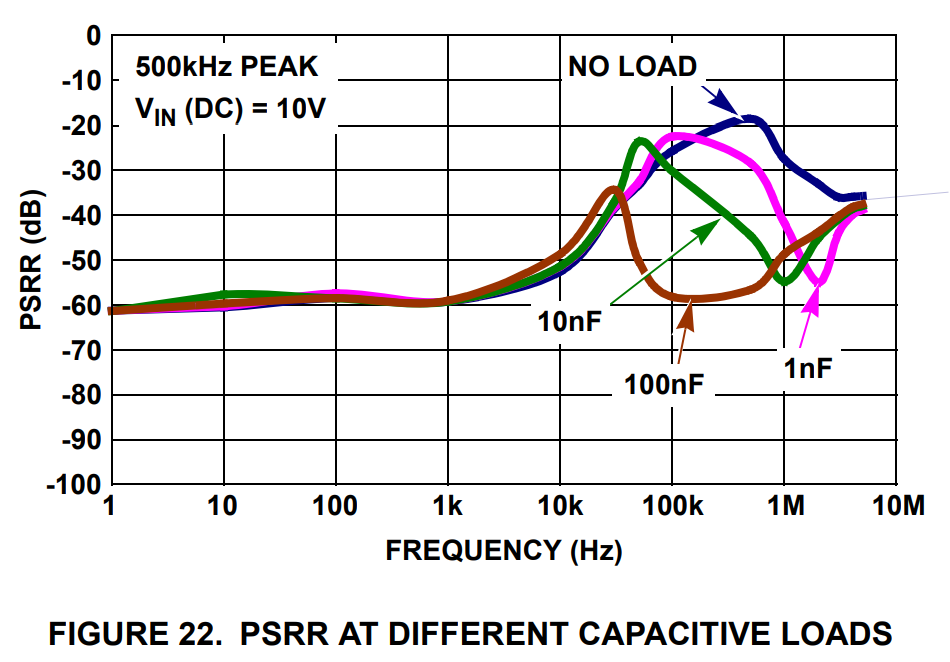

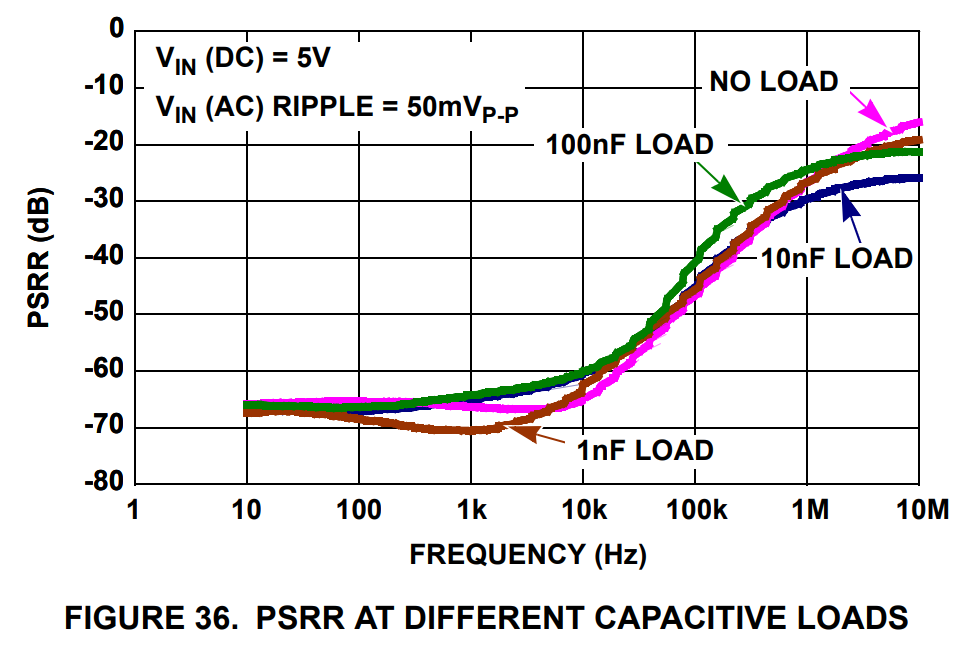

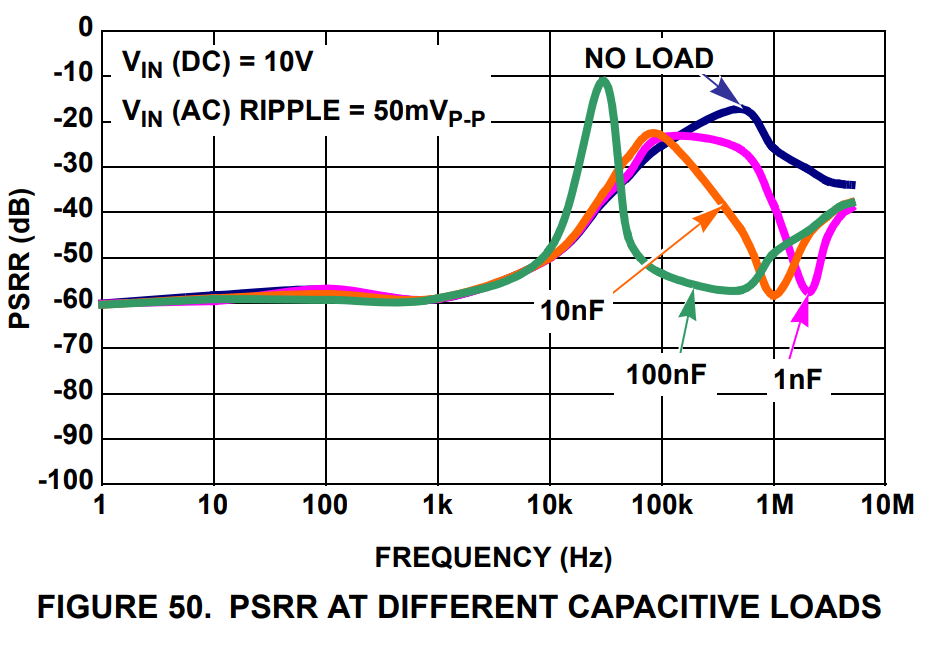

从典型曲线(图8、图22、图36、图50)可见:

低频 PSRR 很好,高频衰减明显,所以必须在 VIN 端加 0.1µF + 10µF 去耦,否则前级的电源噪声会直接调制 Vref。

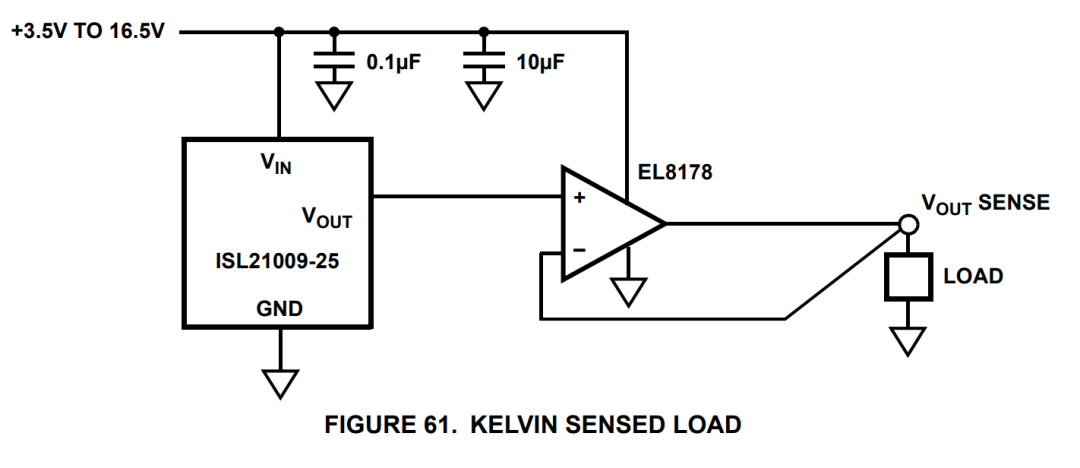

负载能力分析

输出电流:±7 mA

负载调节:10–100 µV/mA

比如有输出 3 mA 变化≈ 30–300 µV,如果接 ADC 参考引脚(通常 <100 µA)影响极小;但如果外接运放 buffer建议 Kelvin sense(图61)

这个芯片有一个非常少见的警告:Pb-free 回流后会漂移 100µV–1mV,X-ray 会永久改变输出;原因是:

浮栅电荷会被 X-ray 改变

如果设备会过机场安检:要屏蔽。

它甚至建议:

两层 1/2oz 铜平面可降低 90% X-ray 剂量

这个在精密设备设计里是非常罕见的注意点。

和常用的 LTC6655 对比

指标 | ISL21009 | LTC6655 |

|---|---|---|

架构 | FGA | 带隙 |

低频噪声 | 4.5 µVpp | 0.25 µVpp |

电流 | 95 µA | 1.5 mA |

精度 | 0.5 mV | 0.025% |

驱动能力 | 一般 | 强 |

一整个崩溃。

登堂入室

什么是浮栅(Floating Gate)?

先回忆一个东西,EEPROM / Flash 存储器;里面有一个结构:

控制栅

│

┌───────┐

│ 绝缘氧化层 │

└───────┘

│

浮栅(Floating Gate)

│

MOS沟道

浮栅被绝缘层完全包围。一旦向浮栅注入电荷:电荷被困住,几乎不会泄漏,可以保存几十年。

FGA 模拟基准的核心思想

普通基准的思路是:

用物理常数(带隙电压 ≈ 1.2V)产生基准

FGA 的思路完全不同:

直接“存储”一个精确电荷,用它定义参考电压

换句话说:

Vref ≈ Qfloating / Ceff

它不是靠 PN 结温度特性平衡,而是靠制造时“写入电荷”;这种精确注入电荷(电子隧穿),直到 Vref = 目标值,这就像“模拟版校准烧录”。

所以它可以做到:±0.5 mV 初始精度,而不需要外部修调。传统基准必须持续维持带隙电流来维持偏置;但是对于FGA浮栅电荷已经存好,只需要一个缓冲放大器,所以静态电流可以做到95 µA 级别。

那为什么低频噪声还存在?

注意一个重要事实:浮栅本身几乎无噪声;但是噪声来自:CMOS 输出缓冲器,MOS 1/f 噪声,偏置电流源,因此:0.1–10Hz ≈ 4.5 µVpp,它比普通带隙低,但比超低噪声参考(如 LTC6655)高。

因为X-ray 会:激发氧化层中的电子,改变浮栅电荷;那电荷改变 → Vref 改变这在数据手册第16页有专门说明这是 FGA 独有的问题。

说说为什么24bit的ADC不适合这个基准

假设:

Vref = 2.5V

ADC = 24bit

LSB 大小:

也就是说:

1 LSB ≈ 0.15 µV

FGA 基准的低频噪声是多少?

ISL21009:

0.1–10Hz = 4.5 µVpp

典型换算 RMS:

(pp ≈ 6 × RMS 近似)

换算成 LSB 看看

这意味着什么?

光是基准噪声,就已经有 5 LSB 的随机抖动

注意哦~这是低频噪声,不是宽带。

真正问题在这里:低频噪声不能被平均掉

如果是白噪声可以通过过采样 + 数字滤波降低,但 0.1–10Hz 噪声是 1/f 噪声,会直接变成慢漂移,在 DC 测量中无法滤除;对高分辨率直流系统来说:

低频噪声才是致命的

比如 LTC6655:

0.1–10Hz ≈ 0.25 µVpp

≈ 0.04 µV RMS

换算:

差距:

器件 | LSB RMS |

|---|---|

ISL21009 | ~5 LSB |

LTC6655 | <0.3 LSB |

差了一个数量级以上。

再看长期漂移

ISL21009:

长期漂移 ≈ 50 ppm

50 ppm 对 2.5V:

µ

换算 LSB:

µµ

当然这是长期漂移,但说明:它的设计目标不是亚微伏级稳定系统。

再看输出阻抗问题

FGA 用 CMOS 输出级输出阻抗较高,驱动电容能力有限,所以瞬态响应较慢;我们知道24bit ADC(尤其 SAR)在采样瞬间会产生参考电流尖峰,如果参考源输出阻抗高 → 参考电压瞬态下沉;这直接转化为:

动态 INL / DNL 误差

那为什么很多 24bit ADC 也用普通基准?

因为24bit 标称 ≠ 24bit ENOB,而实际有效位数通常 18–20bit,很多系统可以靠校准补偿。

所以:

ISL21009 可以驱动 24bit ADC但不会发挥 24bit 的全部潜力

至于一个基准是否适合 24bit:

关键看:

ISL21009≈ 5,这明显超标;它不适合“真 24bit”系统的原因不是精度问题,而是:

低频噪声和输出动态性能达不到亚微伏级要求。

后记

FGA 高精度电压基准不是“产生”一个物理参考电压而是“存储”一个经过精确校准的电荷,并把它缓冲输出,更像:一个“模拟 EEPROM 电压源”。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-02-25,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录