从 AD620 的宏模型分析 LTSpice 器件建模

那我前几天写的这个 LTSpice,还有不少后续,令人讽刺的是这个东西好的教程不多(放大器笔记算,官方有一些,还有日本人写了不少),是的。

就落下了一个牛逼的很,又不能让很多人用起来的尴尬境地。

所以我还想用我建模这一套写这个东西,毕竟要留不一样的东西在世间;先写一些,最后把顺序排一下。和设计 PCB 一样,第一步也是原理图设计,在这之前是元器件,除了理想的以外就是这些现成的了,ADI 收了 LT,所以自带的器件库分外的丰富,所以这篇我想写写这个器件模型。

我这里一开始就想到了这个 AD620,非常经典,直接开刀

我这里一开始就想到了这个 AD620,非常经典,直接开刀

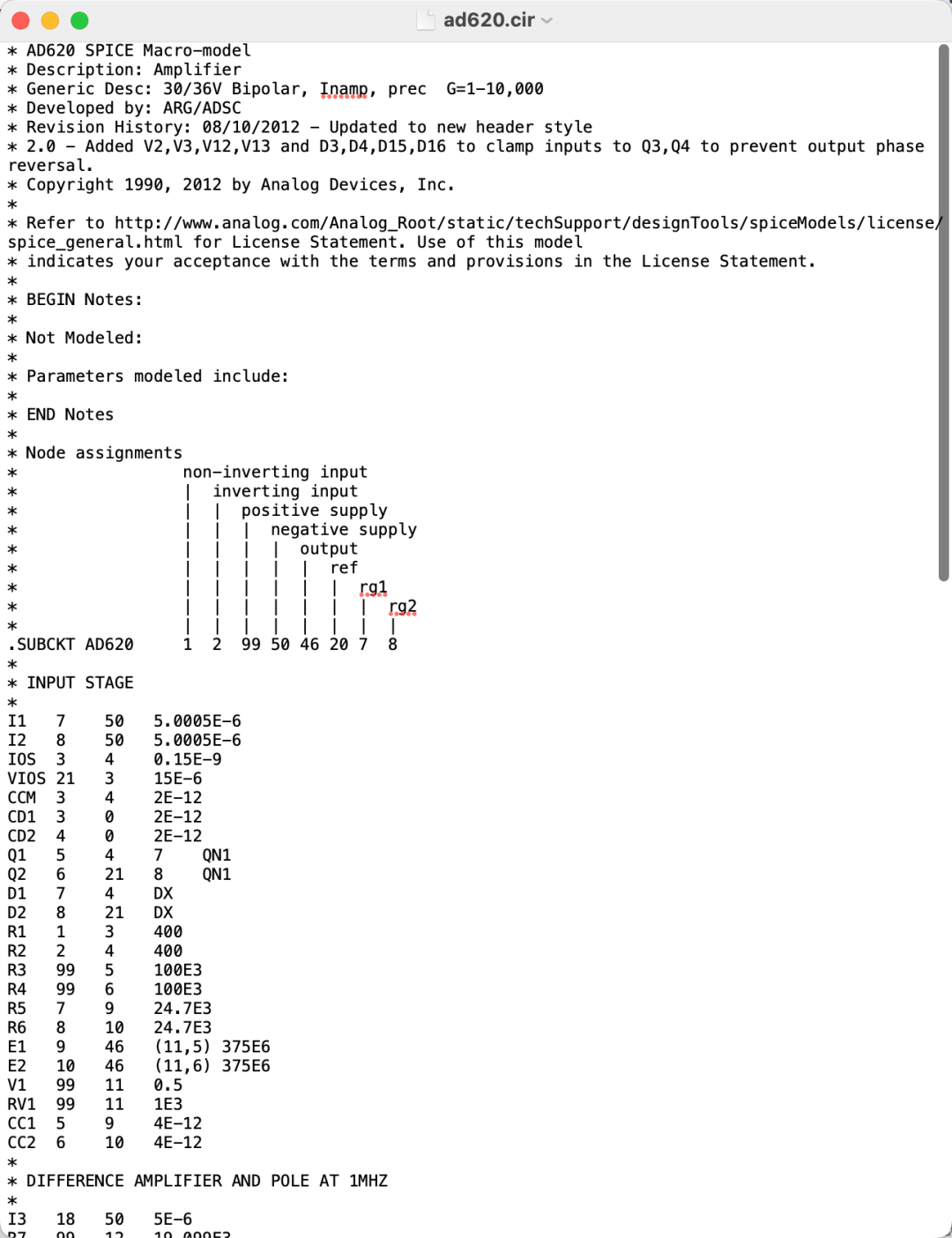

这个 ad620.cir 本质上是 AD620(仪表放大器)的 SPICE 宏模型(macro-model):用一堆受控源、晶体管、二极管、RC 等“等效电路”去近似 AD620 的直流/交流/稳定性/部分非线性行为,供 LTspice 做仿真用。

文件头在说什么?

开头几行是说明:

* AD620 SPICE Macro-model:这是宏模型

Generic Desc: 30/36V Bipolar, Inamp, prec G=1-10,000:双极型仪放,增益范围 1~10000

2.0 - Added ... to clamp inputs ... prevent output phase reversal:模型 v2.0 加了一些钳位(clamp)器件,防止输出相位反转等不良仿真现象(也更贴近真实器件的保护行为)

.SUBCKT 引脚定义

在 .SUBCKT 之前,它给了一段非常清晰的节点/引脚注释:

* Node assignments

* non-inverting input

* | inverting input

* | | positive supply

* | | | negative supply

* | | | | output

* | | | | | ref

* | | | | | | rg1

* | | | | | | | rg2

.SUBCKT AD620 1 2 99 50 46 20 7 8

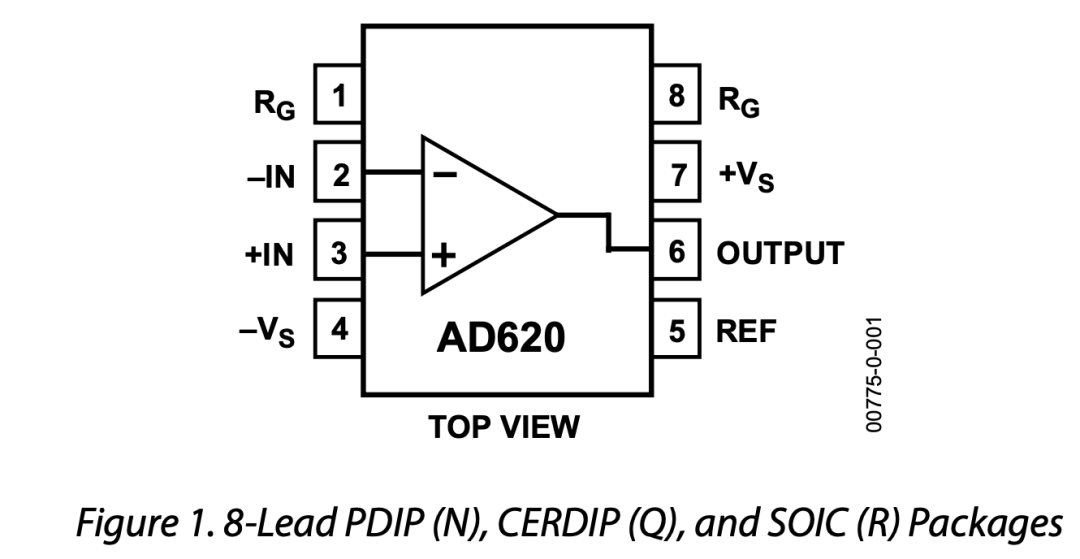

所以这个子电路 AD620 的 8 个引脚顺序是:

1:+IN(同相输入,non-inverting input)

2:−IN(反相输入,inverting input)

99:+VS(正电源)

50:−VS(负电源)

46:OUT(输出)

20:REF(参考端,输出参考/偏置点)

7:RG1(增益电阻端 1)

8:RG2(增益电阻端 2)

这一步非常重要:很多人接不对就是因为不知道

.SUBCKT的 pin order。

网表的分块结构(每一块在模拟芯片哪部分)

这个文件后面用大写注释分了 7 块,按“芯片内部功能”解释:

* INPUT STAGE 输入级(决定输入偏置/失调/输入噪声雏形)

这一段会看到:

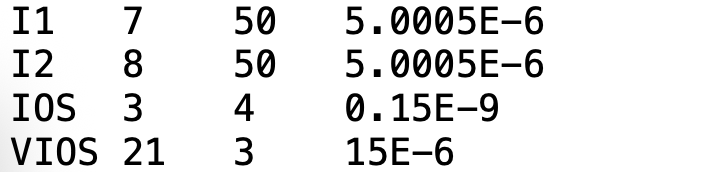

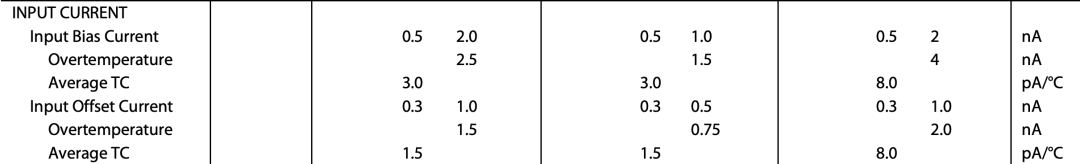

I1 I2:两个微安级电流源,等效 输入偏置电流/输入级偏置

IOS:输入失配电流(input offset current)建模

VIOS:输入失调电压(典型几十 µV 级)建模

模型

模型

数据手册数据

数据手册数据

CCM, CD1, CD2:输入电容/共模相关电容(影响高频、稳定性、CMRR)

Q1 Q2 + D1 D2:输入晶体管和二极管等效,用来表现输入级的非线性、钳位等行为

R1 R2:输入串联电阻(某种等效输入电阻/保护/噪声贡献)

可以把这一块理解为:“让仿真里能出现输入失调、偏置、输入电容、输入保护的基本行为”。

* DIFFERENCE AMPLIFIER AND POLE AT 1MHZ 差分放大 + 1 MHz 极点

这里一般会用受控源(E 元件)+ RC 做一个 固定的中频增益,并加一个 1 MHz 的极点来近似开环特性/内部补偿的一部分。

* GAIN STAGE AND DOMINANT POLE AT 0.667HZ 增益级 + 主极点(超低频)

会看到“dominant pole”这种字眼:这就是宏模型在塑造 低频开环增益非常高、并在很低频处滚降的典型运放/仪放开环形状。

主极点放得很低,是为了让 AC/稳定性仿真表现得像真实器件(高 DC 增益 + 单极点滚降)。

* POLE AT 10MHZ 高频极点

再加一个高频极点,让幅相曲线更接近真实芯片在高频的掉相/带宽限制。

* COMMON MODE STAGE WITH ZERO AT 100HZ 共模通道 + 100 Hz 零点

仪表放大器核心指标是 CMRR,所以模型通常会额外做一条“共模路径”,再塞零点/极点去拟合 CMRR 随频率变化的形状。

* OUTPUT STAGE 输出级(摆幅/限流/驱动能力的近似)

这里会出现:输出缓冲,输出电阻(等效输出阻抗),可能的钳位/限幅(二极管到电源轨/到内部节点);也对应文件头提到的“clamp inputs…prevent phase reversal”那类保护建模。

* MODELS USED 器件模型表

最末尾会定义类似:

.MODEL QN1 ...(晶体管模型)

.MODEL DX ...(二极管模型)

以及可能的开关、受控源参数。是宏模型赖以成立的“底层器件参数”。

怎么在 LTspice 里用它?

直接在原理图里 include + 用“子电路符号”

把 ad620.cir 放到 .asc 同目录(最省心),然后在原理图加指令:

.include ad620.cir

放一个 8 引脚符号(你可以自己画,或用 LTspice 的“从 .subckt 自动生成符号”功能),符号的 Value 填 AD620,Prefix 用 X;连接关系按上面 pin 顺序接:+IN、−IN、±VS、OUT、REF、RG1、RG2。

直接写网表调用

在 netlist 里这样实例化:

XU1 VINP VINN VPOS VNEG VOUT VREF RG1 RG2 AD620

.include ad620.cir

RG1 和 RG2 之间接一个外部电阻 RG(设定增益)

VREF 接地=输出参考为 0V;或者接 2.5V=输出偏置到 2.5V(单电源系统常用)

这个模型适合仿真什么?不适合什么?

适合

DC 工作点:输出偏置、输入失调带来的输出偏移

AC 小信号:增益带宽、相位特性、CMRR 随频率变化趋势

环路稳定性相关的幅相形状(到一定频段),部分限幅/钳位行为(模型做了 clamping)

不适合

超精细的失真(THD)预测(宏模型通常不为低失真精确拟合);输出驱动极限下的瞬态细节(比如重负载、复杂负载的动态);过于极端工况(输入超范围、ESD/保护的真实瞬态能量)。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-02-08,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录