拿着3PEAK 的新品TPA1782,并且对着评估板指指点点

今天这个主角是 3PEAK,很少写它家的东西,最近找大哥要了几个样片:

同城就是快!

同城就是快!

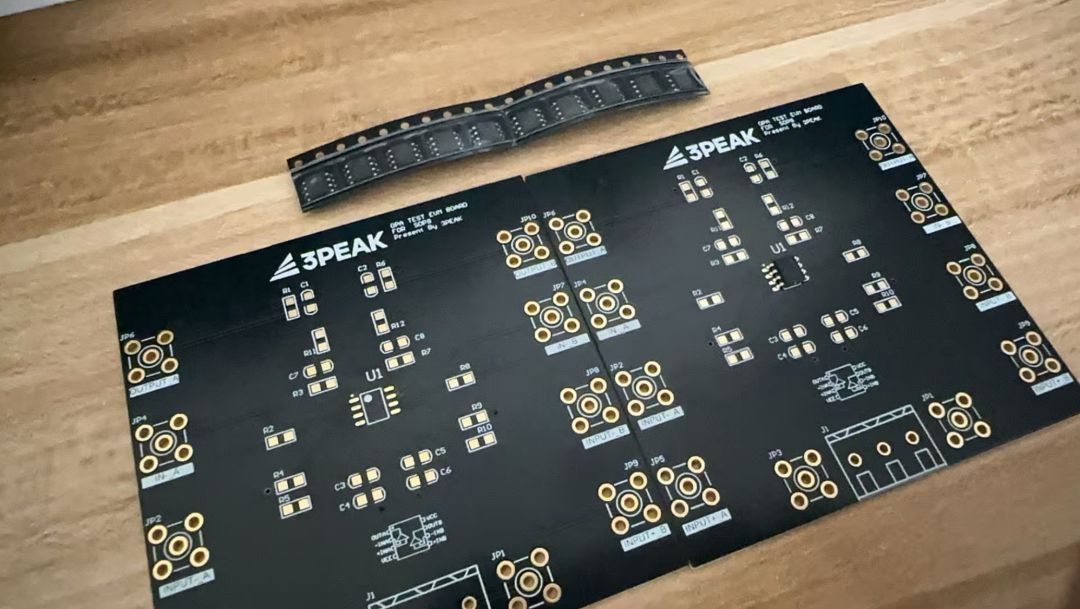

今天就收到了,不过还是有点懵逼:

真散料。我以为 bom 表全的

真散料。我以为 bom 表全的

一般商单就不能这样搞了,这个反正就是裸体的样子也能放~~~

开始今天的分享:

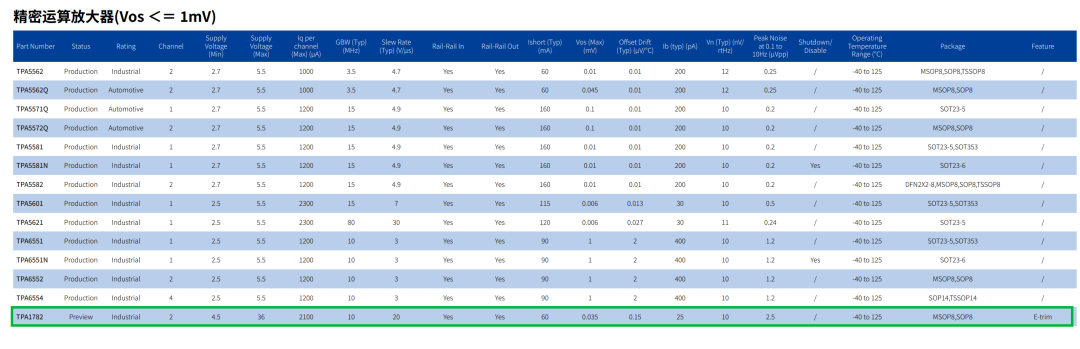

今天这个和我平时写的精密运放不一样,他是属于高压类型

今天这个和我平时写的精密运放不一样,他是属于高压类型

然后呢,官网这个手册是同步更新的:

可以看到是预览状态

可以看到是预览状态

先总结一下:

36 V 高供电、极高 PSRR/CMRR、低失调/低温漂、较强容负载驱动、很低 THD+N → 适合:

桥式/电阻分压传感器放大(压力、应变、温度等),尤其单电源高电压系统;精密缓冲 + 有源滤波 + 采样保持/ΣΔ ADC 前级;工业控制/电机控制里需要较大摆幅、较强驱动且不牺牲精度的环节;音频/低失真缓冲(失真指标漂亮)。

就是说,这个片子还挺能打~

器件定位与家族

家族成员:单路 TPA1781、双路 TPA1782、四路 TPA1784;目标是“高供电电压 + 低失调 + 稳定高频响应 + 低功耗”的通用精密放大。适合工业/仪表/电机控制/有源滤波/传感器接口。

供电范围 4.5–36 V,轨到轨输入/输出(RRIO),GBW≈10 MHz,SR≈20 V/μs,静态电流约 2.0 mA/放大器。

低失调:标称 ±35 µV(Max),并给出 0.15 µV/°C 的失调温漂指标。

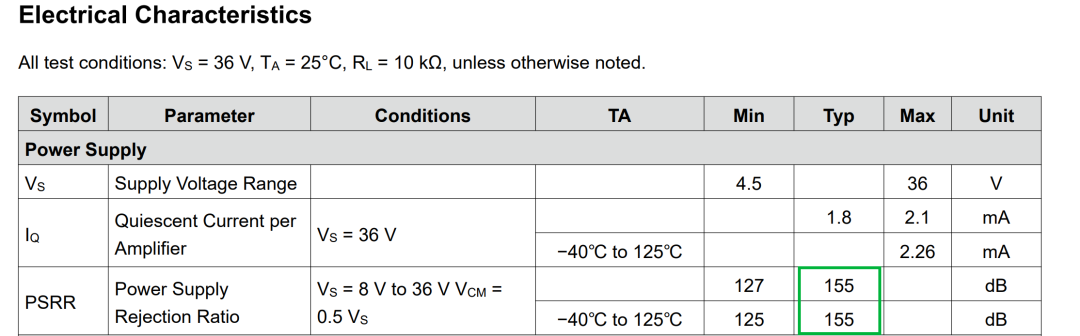

关键直流与电源指标(与可用动态范围密切相关)

供电电压:工作 4.5–36 V,绝对最大 40 V。可单电源或双电源(例如 ±15 V)。

静态电流 IQ:VS=8–36 V 时典型 1.8–2.1 mA/amp。

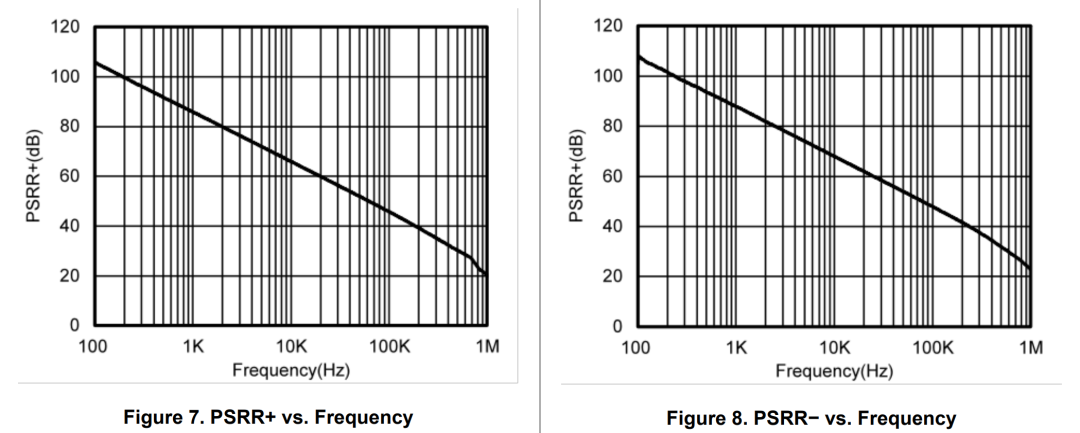

PSRR:在 VS=8→36 V、VCM=0.5VS 条件下典型 155 dB(极高),利于电源纹波抑制。

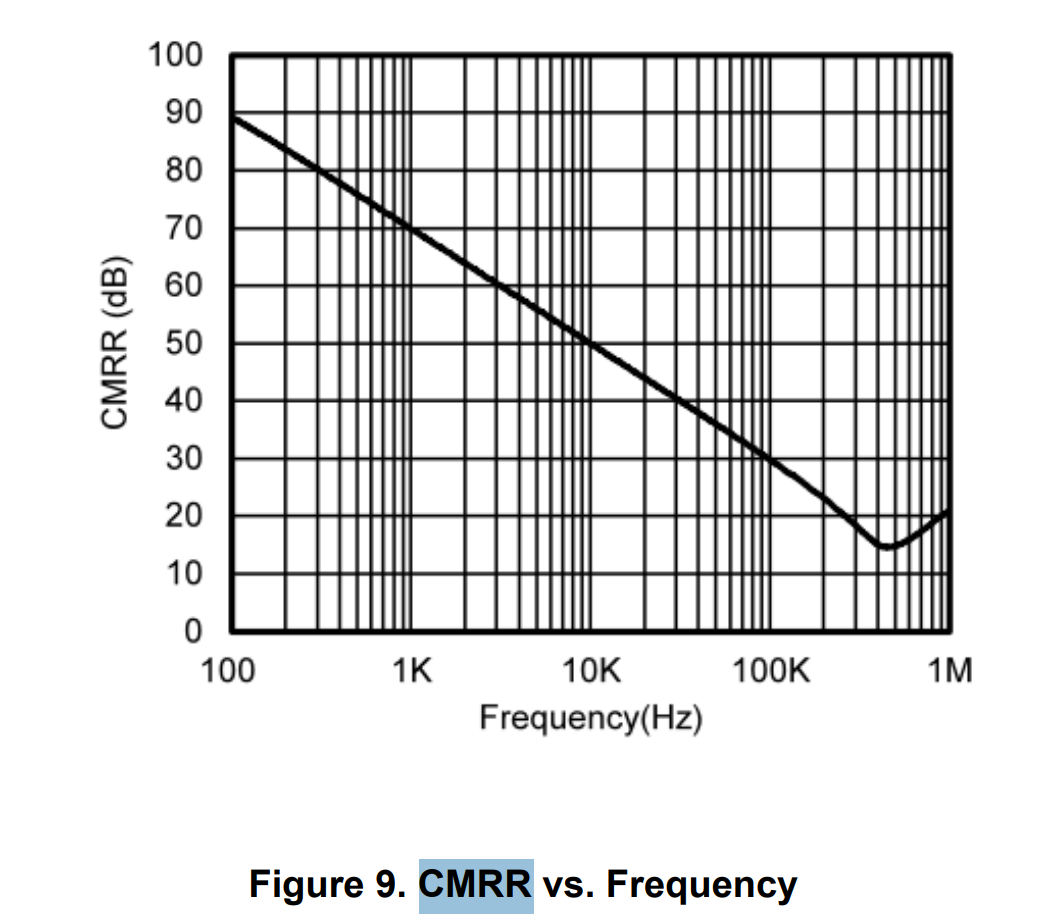

CMRR:共模在中段时典型 130 dB;但靠近上电源轨(V+−1.5 V 至 V+−0.1 V)时典型 125 dB,这提示靠近上轨时直流性能略有下降。

输入共模范围 VCMR:覆盖 −0.1 V 到 V+ + 0.1 V(不同供电示例下给出数值),这支撑 RR 输入覆盖到两轨外侧一点点的“超范围”余量。

设计含义:

这颗器件对电源与共模波动非常“淡定”(高 PSRR/CMRR),适合低频高精度测量与工业现场的电源环境。

PSRR 很高

PSRR 很高

两个轨

两个轨

但当输入共模逼近上轨时,噪声/CMRR 指标会变差一点(手册给了不同 VCM 区间的噪声与 CMRR),布局/偏置尽量让 VCM 处于“中段”更理想。

这里

这里

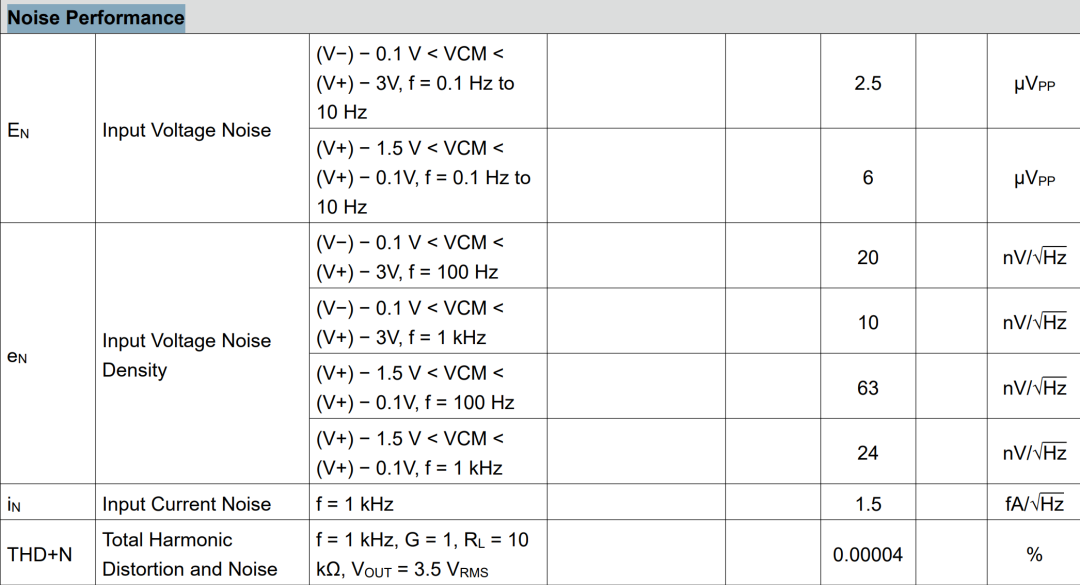

“Electrical Characteristics / Noise Performance & CMRR”表格里,用不同的 VCM 区间分别给了噪声与 CMRR 数值:

0.1–10 Hz 低频噪声(输入等效)

VCM 处在中段: → 2.5 µVpp。Datasheet_TPA1781_TPA1782_TPA17…

VCM 逼近上轨: → 6 µVpp(另一处规格页给 7 µVpp 的版本)。

宽频电压噪声密度(输入等效)

中段 VCM:20 nV/√Hz @100 Hz、10 nV/√Hz @1 kHz。

逼近上轨:63 nV/√Hz @100 Hz、24 nV/√Hz @1 kHz(同样在多处表格出现)。

CMRR(共模抑制比)

中段 VCM: → 约 115–130 dB(随供电页而不同)。

逼近上轨: → 约 102–125 dB。

归纳:当 VCM 贴近上电源轨时,0.1–10 Hz 噪声与宽频噪声密度显著变大,CMRR 也略降;把工作点放在中段 VCM能获得更好的噪声与抑制指标。上述位置就是手册里“噪声/CMRR随VCM区间”的明确出处。

我只能说加上频率以后就有点每况愈下了

我只能说加上频率以后就有点每况愈下了

输出能力与摆幅(驱动负载的可用范围)

输出摆幅(到电源轨的余量):

RL=10 kΩ 时,离正/负轨约 8–20 mV(VS=4.5/8 V 情况),VS=36 V 情况下为 45–100 mV。载流越大余量越大(RL=2 kΩ 时约 30–300 mV)。无负载时可逼近 2–10 mV。

短路输出电流:源/灌约 50–70 mA(视供电不同),可见输出级较硬,对中等电容/电阻负载友好。

电容性负载:宣称可驱动 10 nF,对需要长线/容性采样保持的系统很有帮助。

在放大缓冲 ADC 前级、驱动长线/电容负载会更省心。但大电容直挂仍建议串个 5–20 Ω 小电阻或做“R-C 雪崩环/隔离电阻”来提升相位裕度(通用做法)。

交流与瞬态性能(带宽、阶跃、过载恢复)

GBW≈10 MHz;SR≈20 V/µs;0.01% 建立时间 ~0.7 µs(10 V 步进,G=1);过载恢复 ~250 ns。

开环增益 AVOL:在较轻载(10 kΩ)下可到 155 dB,为高闭环精度与低失真打下基础。

THD+N:1 kHz、G=1、10 kΩ 负载、Vout=3.5 VRMS 情况下 **0.00004%**,可视作“音频友好”的精密型器件。

在 kHz~低十 kHz 的工业/传感应用,能做到高环路增益 + 快速阶跃 + 很低失真,既适合精密直流测量,也能胜任有一定动态要求的驱动与有源滤波。

噪声(宽频与 0.1–10 Hz)与 VCM 效应

电压噪声密度:10 nV/√Hz @1 kHz(当 VCM 不逼近上轨),100 Hz 约 20 nV/√Hz。

0.1–10 Hz 低频噪声:典型 2.5 µVpp(VCM 在中段);当 VCM 逼近上轨(V+−1.5 V…V+−0.1 V)时 6–7 µVpp,噪声明显变差。

电流噪声:约 1.5 fA/√Hz,适合高阻源。

若做超低频/直流高精度(例如毫伏级/微伏级传感器),尽量把输入共模偏在中段,能显著改善 0.1–10 Hz 漂移与宽频噪声。

输入端特性与保护

输入失调/温漂:±35 µV(Max)级别、0.15 µV/°C;适合 16–20 bit 量级的直流测量前端。

IB/IOS:室温典型 ±25 pA,高温规格到 ±20 nA 量级(−40~125 °C),高阻源下要计算偏置引起的误差。

ESD:HBM 3 kV、CDM 1 kV;输入/输出都有到电源轨的 ESD 二极管。若信号可能超过电源轨 500 mV,需限流 <10 mA(串电阻/前级钳位)以保护。

热与封装

常见封装:SOT23-5(单路)、MSOP8/SOP8(双路)、TSSOP14/SOP14(四路)。热阻 θJA:SOT23-5 约 250 °C/W、SOP8 约 158 °C/W、TSSOP14 约 180 °C/W(与铜箔面积强相关)。

短路可以持续,但功耗受供电与短路路数影响,需注意结温 150 °C Max。

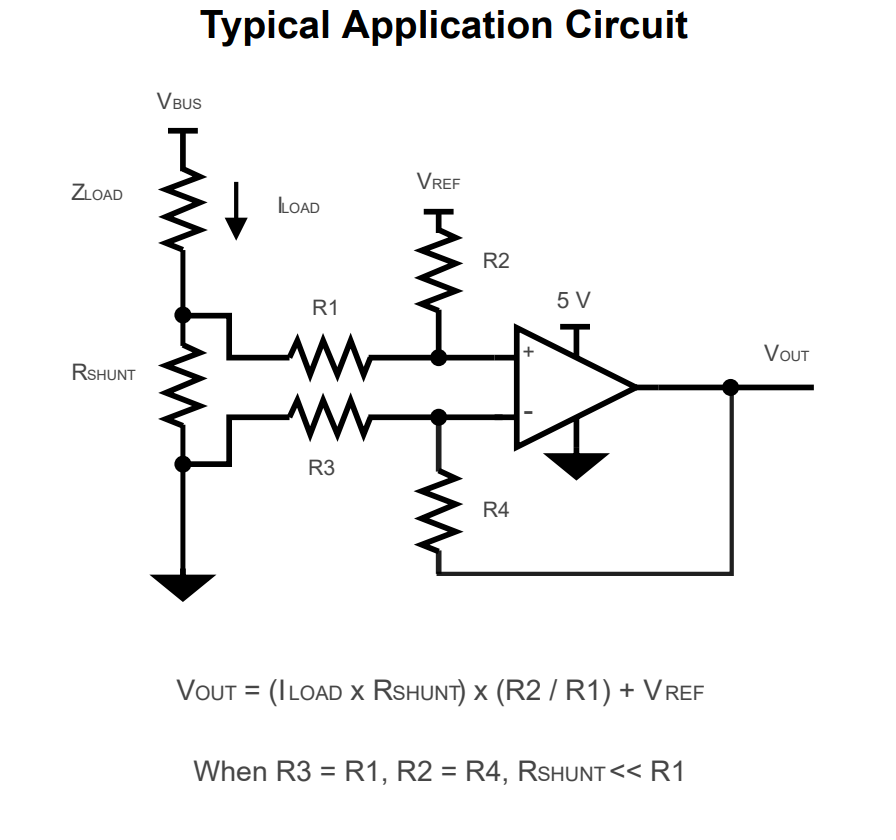

低边电流检测(手册给的范例)

典型电路:Rshunt 取样,运放做差分 + 提供增益,输出 Vout = (I_load × Rshunt) × (R2/R1) + Vref(当 R3=R1、R4=R2、且 Rshunt≪R1 时)。

当头一棒

当头一棒

选择 R1/R2 值时顾及噪声与输入偏置误差(大阻值会把 pA 级 IB 放大成可见误差)。

Vref 确定输出零点;如果 ADC 单极性输入,Vref 设在中点可测双向电流;高边测量时输入共模靠近上轨,若想要最佳噪声/CMRR,考虑抬高负轨或改变分压/隔离方式,让 VCM 不要贴轨运行。

精密缓冲/低通有源滤波(这个是我想的)

GBW=10 MHz、SR=20 V/µs,适中带宽足够做kHz 量级有源滤波;高 AVOL 有利于低失真。容负载驱动能力对后跟采样保持 ADC 的系统也更稳。但是没有写单位增益到底稳定不稳定。

算一下噪音:

设单位增益缓冲、有效平坦带宽 BW(由你的前端/滤波/ADC 决定),中段 VCM:

宽频均方根(RMS)噪声(输入等效)

例:若 BW = 100 kHz,取 →

若闭环增益 G=10,输出等效 ≈31.6 µV_rms。

0.1–10 Hz 区间(低频飘移)手册给的是 峰—峰值:中段 VCM ≈2.5 µVpp;靠近 V+ 会升到 6–7 µVpp。这部分常作为直流/极低频漂移预算单独看待。

源阻/电阻热噪声是否“盖过”运放?电阻热噪声(输入等效):。

想让电阻热噪声低于器件 10 nV/√Hz,室温下R ≲ 6 kΩ;常见 10 kΩ 级环路电阻本身就 ≈12.9 nV/√Hz,会比运放底噪还大,因此选小阻值是降噪关键。

电流噪声折算:。有 i_n≈1.5 fA/√Hz,R_s≤100 kΩ 时几乎可忽略;兆欧级源才需要关心。这些都很简单,随便搞。

等以后有时间了,设计一些实验来实测,现在不行;至于 OP 本身,有愿意体验的小伙伴吗?不包邮出几颗,有需要的可以拿着测测

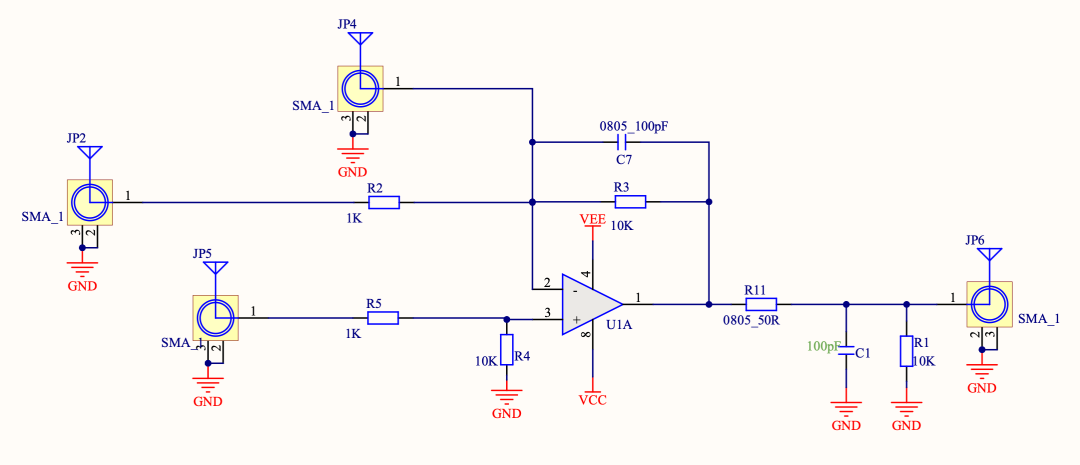

这是 EVAL 板子的原理图

这是 EVAL 板子的原理图

看图是运放差分放大+带有简单滤波的前端电路:

信号接口

JP2 / JP5:输入 SMA 接口,分别接到电阻 R2(1 kΩ)、R5(1 kΩ)。 → 说明这是双端输入,目标是放大差分信号。

JP4:与 R2 输入端并联的 SMA,可能用作测试点或并行输入/旁路。

JP6:运放输出 SMA,用于把放大后的信号引出。

运放 U1A

单个通道。电源脚 VCC/VEE 说明可以单电源或双电源供电。

输入:

反相端(引脚 2)接 R2(1 kΩ)、反馈网络 R3(10 kΩ)和电容 C7(100 pF)。

同相端(引脚 3)接 R5(1 kΩ)和偏置电阻 R4(10 kΩ 下拉到 GND)。

输出:引脚 1 → 通过串联 R11(50 Ω 匹配电阻)→ SMA 输出,同时有 RC 滤波(R1=10 kΩ、C1=100 pF)。

功能解读

差分放大

R2=1 kΩ,R3=10 kΩ → 增益约 −10 倍(反相通道)。

R5=1 kΩ、R4=10 kΩ:构成一个“伪差分输入”,在同相端加地参考,避免漂移。

因此,这电路是一个单端输入 + 增益 10 倍反相放大,或者通过 JP2/JP5 接成差分输入放大(具体看布线)。

高频补偿

C7(100 pF)并联在 R3 上,和 10 kΩ 形成一个零点:

→ 在高频自动降低增益,防止运放振荡、提升稳定性。

输出端

R11(50 Ω):用于驱动同轴电缆(匹配 50 Ω 负载)。

R1=10 kΩ、C1=100 pF:这是一个低通滤波器,截止频率

→ 进一步衰减高频噪声;用了 TPA1781/1782/1784 这类低噪声 RRIO 运放,整个电路就是一个宽带、低噪声、稳定的前置放大器模块。

眼看四下无人,再算算噪音呢?

增益:典型反相放大

同相端经 R5=1 k 与信号相连、R4=10 k 下拉,主要做伪差分/偏置稳定

高频补偿:C7 与 R3 并联,闭环在高频处滚降,角频率

输出端口:串联 R11=50 Ω 做同轴回传的源端匹配;节点处 C1=100 pF 对地(与源等效阻抗 ≈50 Ω 构成一阶低通),而 R1=10 kΩ 只是泄放/偏置,不决定高频角频率。 因为运放 Rout 很小,C1 看到的等效源阻≈50 Ω → (远高于 159 kHz), 所以真正的带宽瓶颈是 C7,不是 C1/R1。

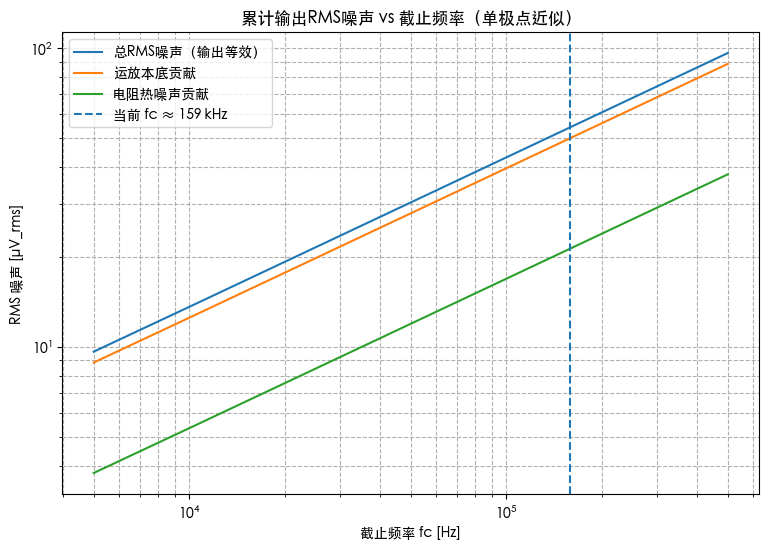

综上:闭环理想带宽 。 单极点近似下的等效噪声带宽(ENBW)≈ 。

噪声(输入等效 → 输出等效)

以下按中段 VCM(TPA178x 的最佳噪声区)估算:

运放电压噪声(主项)

ENBW ≈ 250 kHz

输入等效 RMS:

输出等效 RMS:

(若远端50 Ω 终端使电压二分,则到负载端的噪声与信号一样会衰减 1/2,相当于对负载的有效增益=5。)

运放电流噪声(可忽略)

;以千欧级源阻估算: 仅 皮伏级,远小于 10 nV/√Hz → 忽略。

电阻热噪声

室温下 。

R2=1 kΩ(反相输入电阻):其等效“加到输入端”的系数≈1(典型反相结构)。

R3=10 kΩ(反馈电阻):自身约 ,折算到输入端大致 ÷增益比(≈R3/R2=10),得到 ≈1.29 nV/√Hz 的输入等效。

R5=1 kΩ、R4=10 kΩ(同相端分压):贡献很小;在反相拓扑里主要通过共模/偏置路径耦合,通常远小于主通道两电阻。

因此,电阻噪声输入等效可近似合成:。 与运放本底 10 nV/√Hz 合成 → 。

最终(更保守)的输出噪声:(到 50 Ω 终端处约 27 µV rms)。

2.4 0.1–10 Hz 低频噪声(漂移项)

中段 VCM:输入等效 ≈2.5 µVpp → 输出 ≈25 µVpp(远端终端处 ≈12.5 µVpp);如果共模“贴上轨”,这个项会升到 ~6–7 µVpp(输出 60–70 µVpp),且宽频密度也劣化——应避免。

鄙人对这个电路的优化建议(按“噪声/带宽/传输”排序)

保持 VCM 在中段(供电或前级偏置上做保证),否则 0.1–10 Hz 与宽频噪声都变差。

电阻再降一档(保持增益 10 不变):如 R2=499 Ω、R3=4.99 kΩ。

R2 热噪声降到 ~2.9 nV/√Hz,R3 折返到输入 ~0.9 nV/√Hz,合成输入等效降到 ≈10.4 nV/√Hz,总输出噪声可降**~10%,同时提高相位裕度**。维持相同 只需把 C7 改为 220 pF(因 R3 降为一半)。

前端限带:若 ADC/后端只需几十 kHz,把 C7 再加大(或在输入端加小电容与 R2 构成零极点配对),让 ENBW 再小一些,噪声 会继续下降。

匹配与端接:

若示波器/后端选择 50 Ω端接:R11=50 Ω 是典型“源端回终”配置,信号与噪声都会二分,但反射小(但是这个频率也没有什么好说的)、链路干净。

如果后端是 1 MΩ 高阻:R11 形成源阻抗 50 Ω,C1=100 pF 的角频率在 31.8 MHz,几乎不动这个 160 kHz 的通带;R1=10 kΩ 仅作泄放。

输入保护(若可能越轨/外接传感器):在 JP2/JP5 与 R2/R5 之间串 51–100 Ω + 钳位(肖特基到供电轨或 TVS),限流 < 10 mA。

结论

通带:≈ 160 kHz(由 C7 决定)

输出噪声:≈ 54 µV rms(到 50 Ω 终端≈ 27 µV rms)

低频漂移(0.1–10 Hz,输出):≈ 25 µVpp(中段 VCM),贴上轨会到 60–70 µVpp

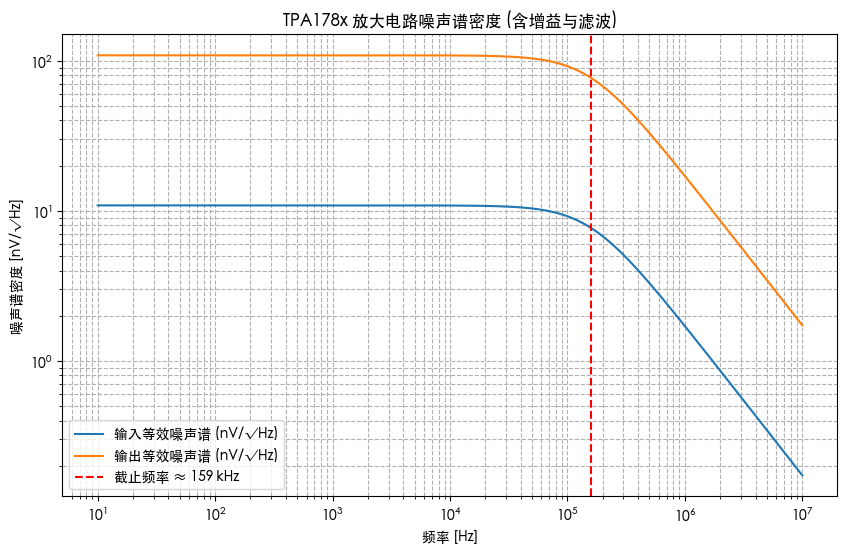

可视化一下

可视化一下

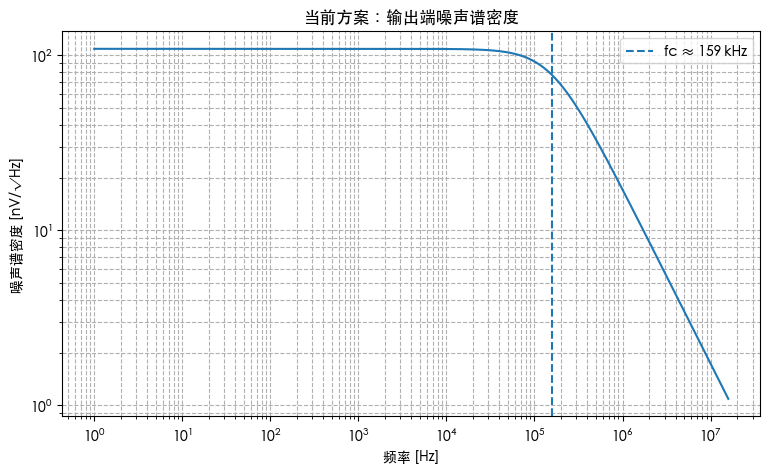

给出了电路的噪声谱可视化结果:

橙色曲线:输入等效噪声谱,低频区约 11 nV/√Hz,在截止频率 (~159 kHz) 后随滤波器衰减。

蓝色曲线:输出等效噪声谱,低频区约 110 nV/√Hz(因为增益 10 倍),同样在截止频率处开始下降。

红虚线:闭环 −3 dB 截止频率 ≈ 159 kHz(由 R3=10k 与 C7=100pF 决定)。

积分结果(RMS 噪声)

输入等效 RMS 噪声 ≈ 5.4 µV

输出等效 RMS 噪声 ≈ 54 µV

image-20250917112824094

(若负载端 50 Ω 终端,电压会二分,对负载的实际噪声约 27 µV rms。)

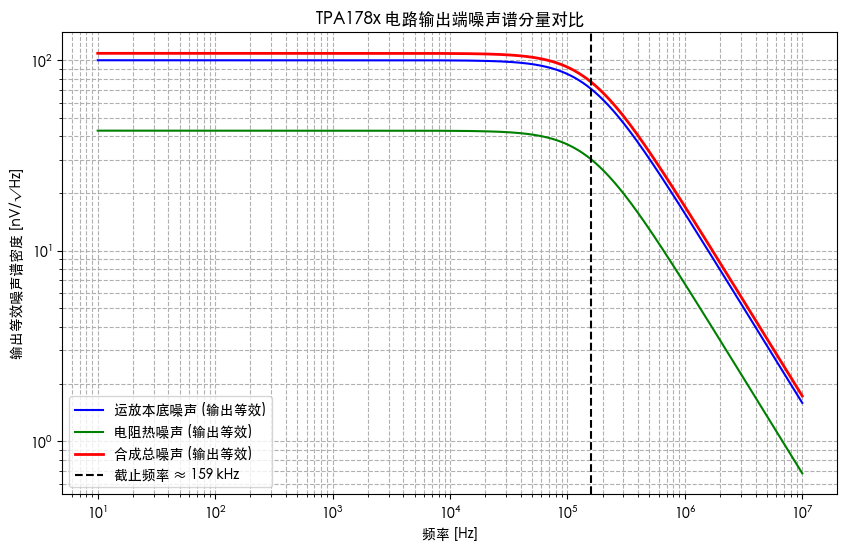

噪声贡献

噪声贡献

这张图把噪声贡献分解出来了:

蓝色曲线:运放本底噪声(输出等效,增益 10)。

绿色曲线:电阻热噪声(输出等效)。

红色曲线:合成总噪声。

黑色虚线:闭环截止频率 ~159 kHz。

可以看出:

在低频和通带内,运放本底噪声(蓝色)主导,电阻噪声只是次要贡献;合成总噪声(红色)几乎与运放曲线重合,说明这电路里 噪声瓶颈是运放本身;截止频率之后三条曲线同步下降,因为滤波器衰减了所有噪声源。

噪声 vs 带宽

噪声 vs 带宽

“累计输出RMS噪声 vs 截止频率”图:直观看出带宽越窄,积分噪声按 √BW 缩减;黑虚线是当前 fc≈159 kHz。

image-20250917113245337

“当前方案的输出端噪声谱密度”图:核对谱形状与 −3 dB 点

当前方案(R2=1k, R3=10k, C7=100p)

累计 RMS 噪声:≈ 54.2 µV_rms

其中运放贡献:≈ 49.9 µV_rms

其中电阻贡献:≈ 21.3 µV_rms

0.1–10 Hz(中段 VCM):≈ 25 µV_pp

降阻等带宽(R2=499Ω, R3=4.99k, C7=220p)

累计 RMS 噪声:≈ 52.1 µV_rms(下降约 4% )

运放贡献基本不变(≈ 49.9 µV_rms),

电阻贡献降到 ≈ 15.0 µV_rms(约−30%)。

说明:在这个配置下,运放本底噪声主导;把环路电阻减半虽能降一部分电阻噪声,但总体只能小降几微伏。若要明显更干净,收窄带宽最有效(比如把 fc 降到 40 kHz,理论上 RMS 噪声会再降一半左右)。

原厂如果看见我写错了,也别锤,毕竟我只是个爱好者~

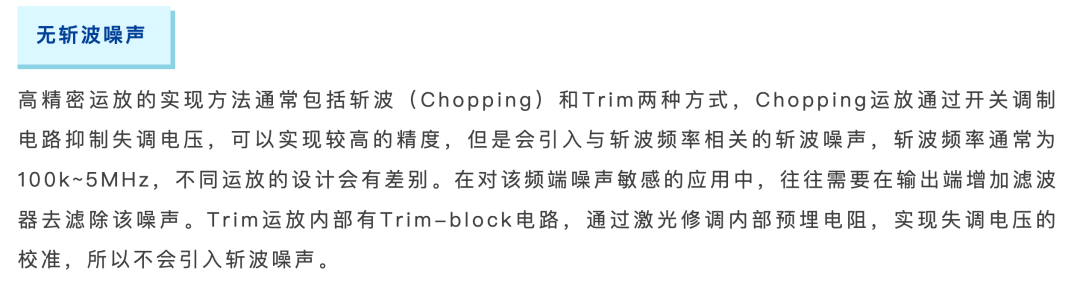

官方的推荐

官方的推荐

我那知道里面咋设计的,不过看纸面参数确实不错的!

https://static.3peak.com/res/doc/ds/Datasheet_TPA1781_TPA1782_TPA1784.pdf

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2025-09-17,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录