什么? 精密ADC停产了?没事,领慧立芯会出手(LHA7530 接力CS5530)

什么? 精密ADC停产了?没事,领慧立芯会出手(LHA7530 接力CS5530)

云深无际

发布于 2026-01-07 11:18:42

发布于 2026-01-07 11:18:42

又又又是领慧,又是一个新品,和以外咬 ADI 和 TI 的屁股不一样,这次咬了另外一家:

这个有熟悉的吗?

这个有熟悉的吗?

没事,这家也是信号链厂,但是做的比较集中:

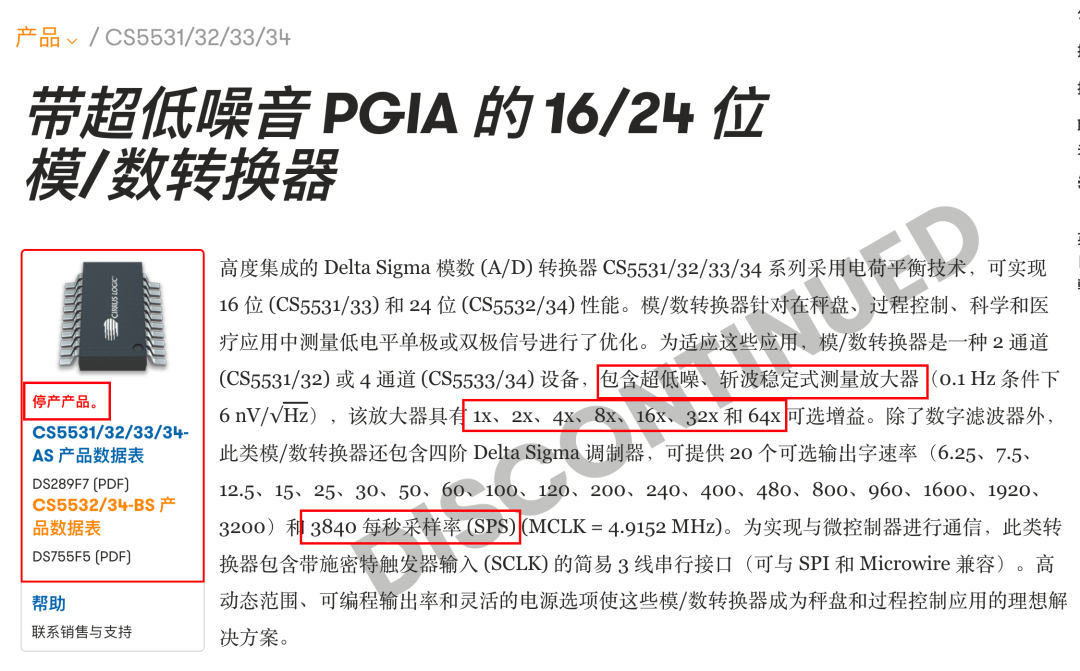

这是他们的产品页

这是他们的产品页

因为现在这个地区战事不断(可能吧),这些没有自己晶圆厂的厂家是对稳定供货很敏感的,所有这家公司有的型号就停产了

型号是比较多的

型号是比较多的

而且也没有推荐的同类产品,那这种情况下,LHA 就有机会了;先看下停产了什么。

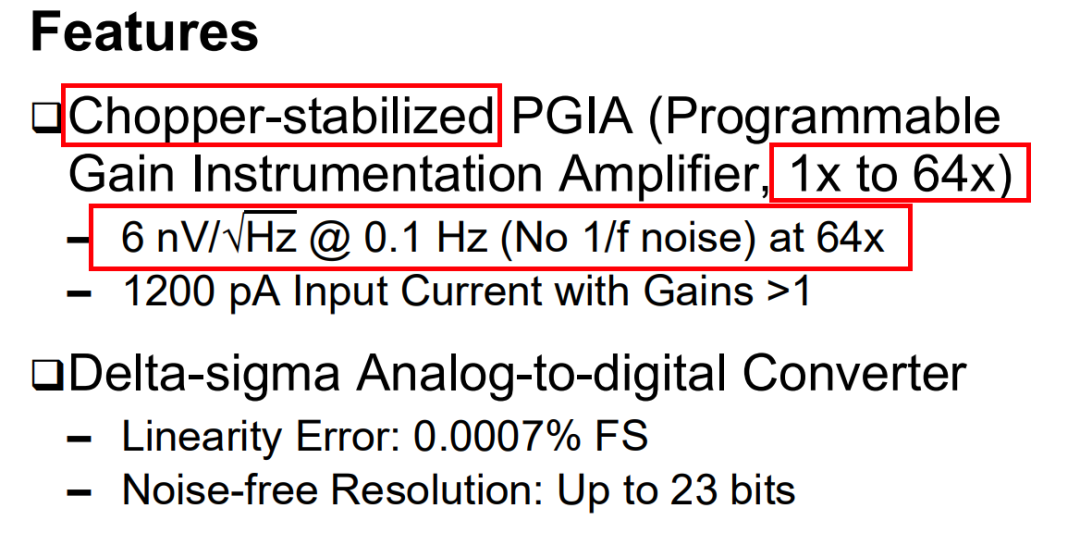

就是一个性能很强的 ADC

就是一个性能很强的 ADC

其中主要还是这个没有 1/f,关于这里的门道我后面会大写特写的

其中主要还是这个没有 1/f,关于这里的门道我后面会大写特写的

CS5530 是什么?

CS5530 = 24bit ΔΣ ADC + 内置 64× 超低噪声斩波仪表放大器(12 nV/√Hz),满量程仅 ±39mV,专为称重/低频/高精度而生。它是最经典的一代“桥式传感器专用 ADC”,在功能上与 ADS1232/ADS1246/AD7730 同档。

可以把它看作:

前端:64× INA(斩波,无 1/f 噪声)

后端:4 阶 ΔΣ 调制器 + Sinc5/Sinc3 滤波器

接口:3 线 SPI

输出分辨率:Noise-free up to 19 bits(在 OWR=7.5 SPS 时)

Feature

模块 | 参数 |

|---|---|

INA | 64×,12 nV/√Hz@0.1Hz,无 1/f 噪声,输入电流 1200 pA |

ADC | 4阶 ΔΣ,线性误差 ±0.0015% FS,24bit 无失码 |

参考 | VREF 可到模拟供电(VA+−VA−) |

噪声 | Noise-free 19bit(低速时) |

数据率 | 6.25–3840 SPS(共 20 档) |

供电 | ±2.5V / ±3V / 单 5V 都能跑 |

接口 | SPI、Schmitt 触发 SCLK、支持光耦直接驱动 |

它本质上是一颗带“完美前置运放”的单通道高精度 ADC,用来接微伏级信号。

前端结构:输入、模型、噪声

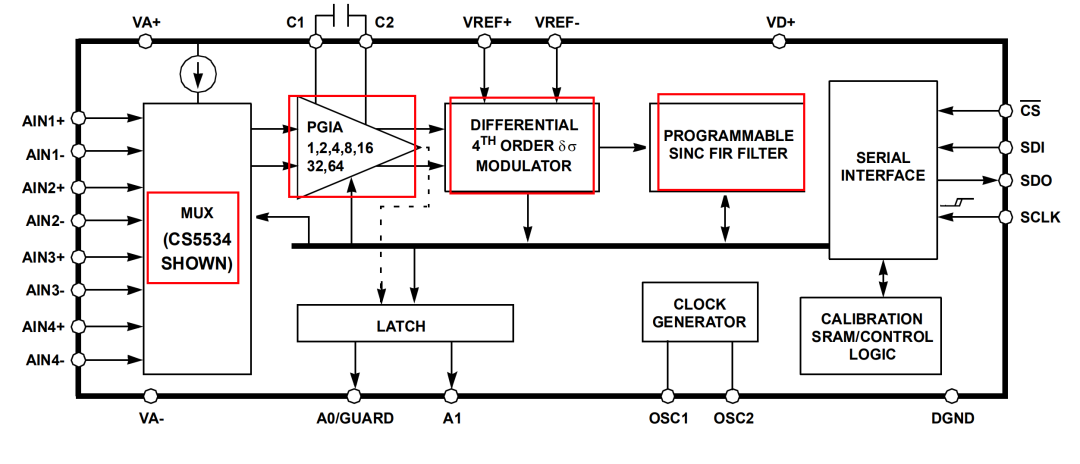

框图也简单,就是流式的信号走向

框图也简单,就是流式的信号走向

图中结构清晰分为:

差分输入 AIN+ / AIN-→ 斩波 64× INA(抑制 1/f 噪声)→ 1000 Ω / 22 nF 内部滤波网络(抗混叠)→ ΔΣ Modulator(4 阶)→ Sinc5 / Sinc3 滤波器;相当于你买到的是:前端模拟 + ADC 全套已匹配的系统,几乎不需要外部驱动运放。

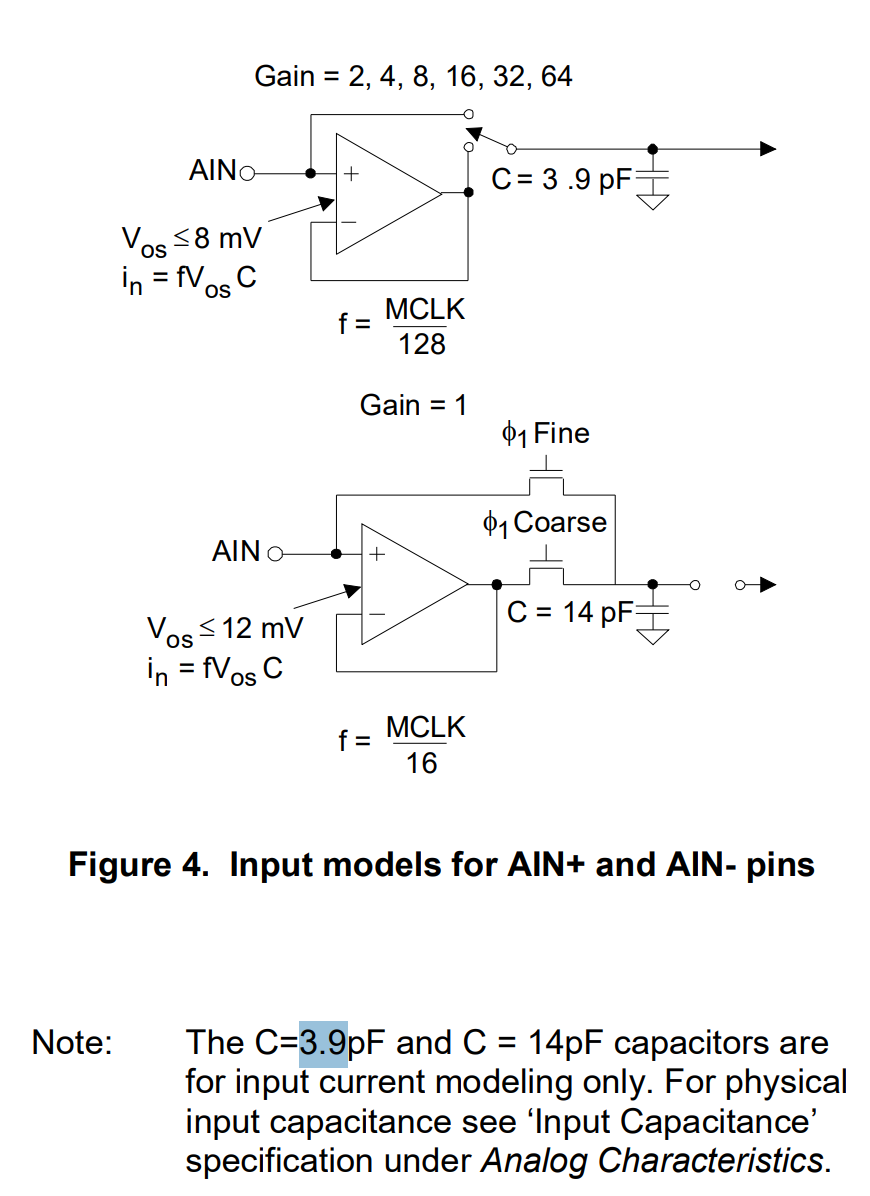

输入模型

输入模型

INA 斩波频率:MCLK/128

输入模型中包含一个 3.9 pF 的“采样电容”

产生的 CVF(采样)电流:

数据表典型值:1200 pA; 前端非常容易驱动,不像 SAR 那样需要高速缓冲器。

输入共模范围

AIN+/AIN- 可做差分测量,但各自必须在:

若用单电源 5V,那共模大约只能放 1.6–3.4V,因此使用桥传感器时通常会把桥激励设在中点(2.5V)。

3.4 输入满量程

若 VRS=1 → Y=1 → 满量程 = ±VREF/64

若 VRS=0 → Y=2 → 满量程 = ±VREF/128

例如 VREF=2.5V:

Gain=64 → ±39mV

Gain=128 → ±19.5mV,这就是为什么它天生适合称重传感器(2mV/V → 10mV)。

噪声性能

表格列出的噪声:

OWR | Noise-free bits | 噪声 (nV_rms) |

|---|---|---|

7.5 Sps | 19 bit | 17 nV |

60 Sps | 18 bit | 48 nV |

120 Sps | 17 bit | 68 nV |

240 Sps | 16 bit | 115 nV |

在 10mV 满量程时:17 nV → 可分辨 10mV / 17nV ≈ 588k 档(约等效 19-bit noise-free resolution)这就是为什么这一代 ΔΣ ADC 在称重行业横扫几十年。

CS5530 的意义 = 你不需要构建前级放大器,它已经自带了完美的超低噪声前端。

用它建的系统一般如下:传感器 → 简单 RC → CS5530(无需前置运放,无需复杂驱动,校准只需要 Offset + Gain)

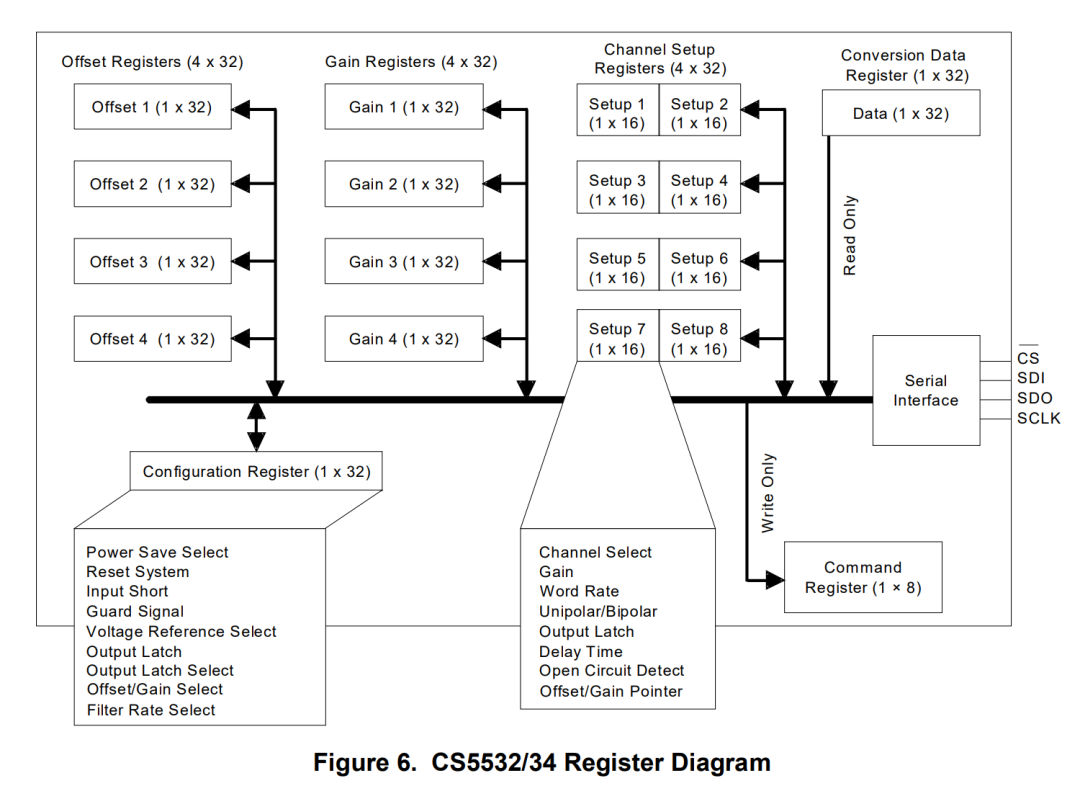

然后这个寄存器配置的图我是很喜欢的,其实使用的时候就是这样

然后这个寄存器配置的图我是很喜欢的,其实使用的时候就是这样

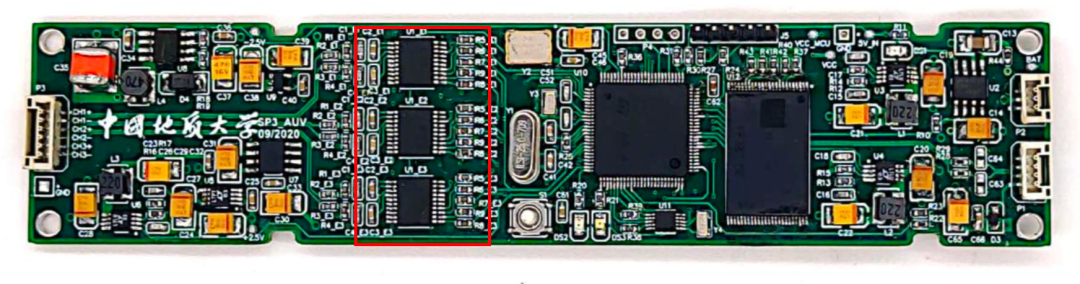

然后最早我接触到这个 ADC 是因为一个海洋工具的事情:

在论文里面出现了这个 ADC,三颗三个轴,就是没有想到停产了

在论文里面出现了这个 ADC,三颗三个轴,就是没有想到停产了

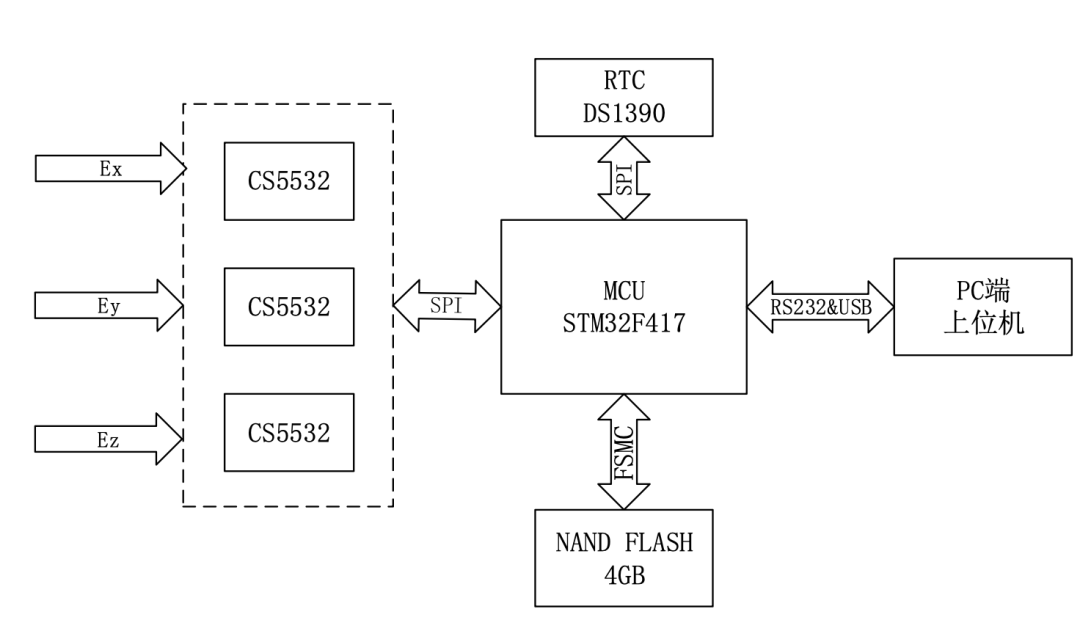

架构是这样的

架构是这样的

那这么好的 ADC,肯定是用了在不同的领域,但是突然的嘎调,你就得囤货以及换,囤货的话,未来还是要换片子;那这样的背景下不如找个替代的:

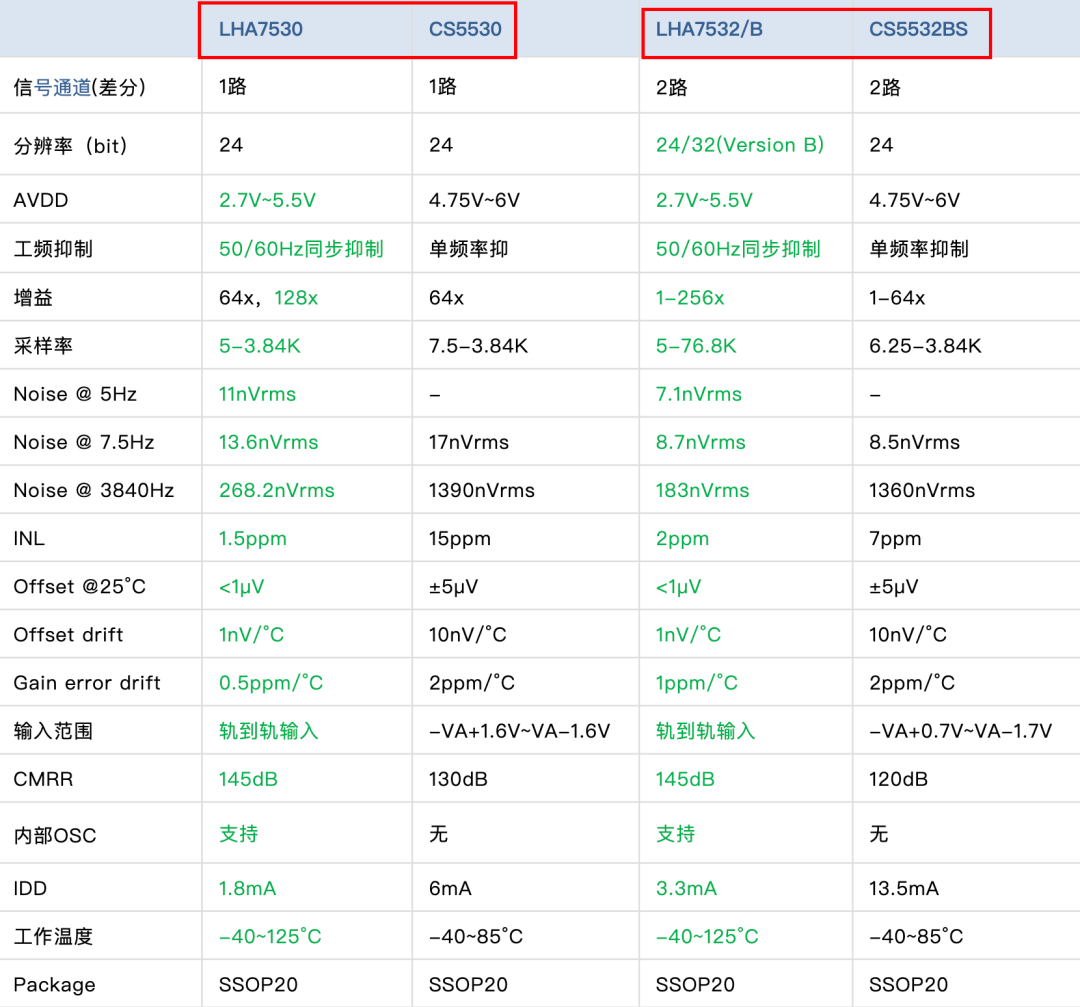

没错,就是这样,对应单通道和多通道,直接 P2P 的俩颗就做出来

没错,就是这样,对应单通道和多通道,直接 P2P 的俩颗就做出来

之前的对标,LHA 还是有点和友军对不上的,这次也不装了,直接就是换个前缀。

好啦,好啦,赶紧看新品。

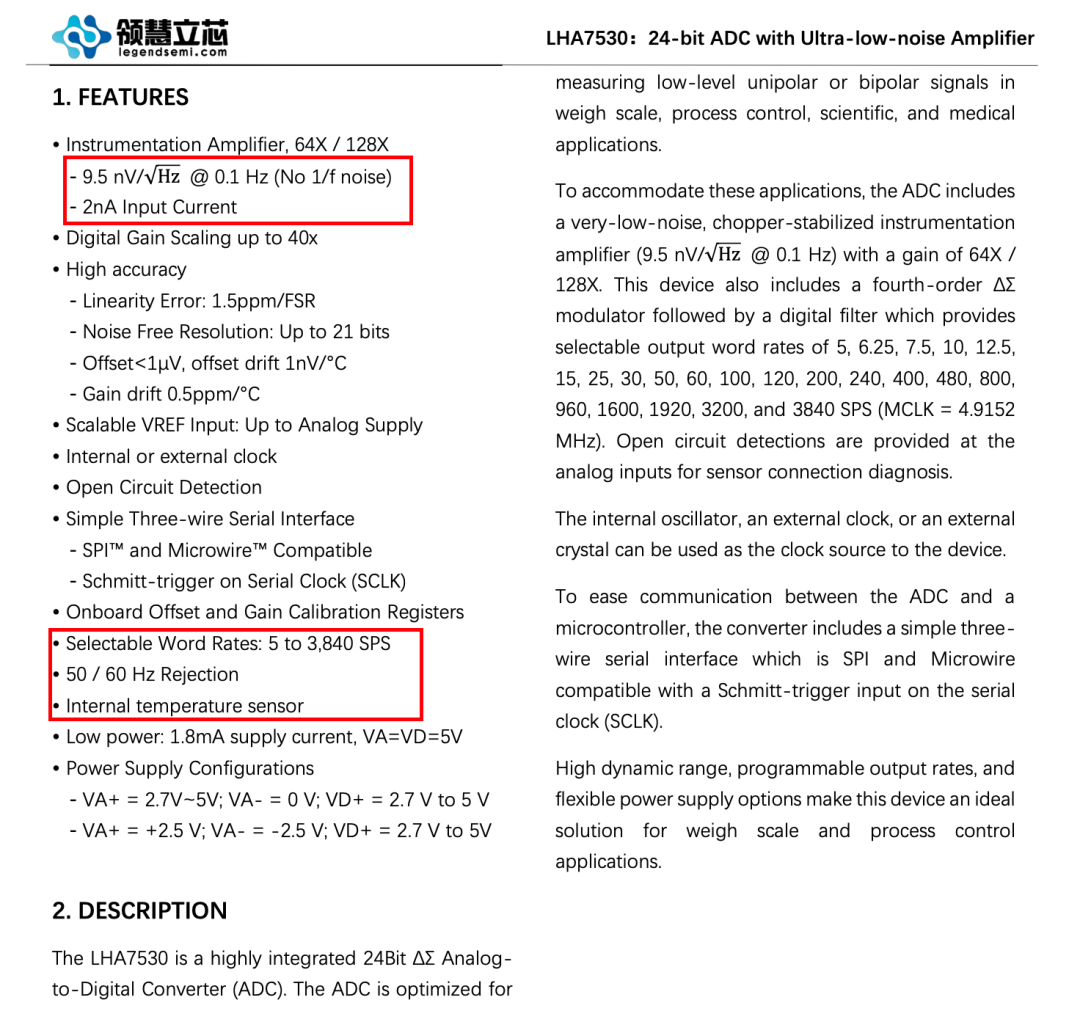

LHA7530 怎么说?

其实看构架大差不差的,就是按照对标设计的。

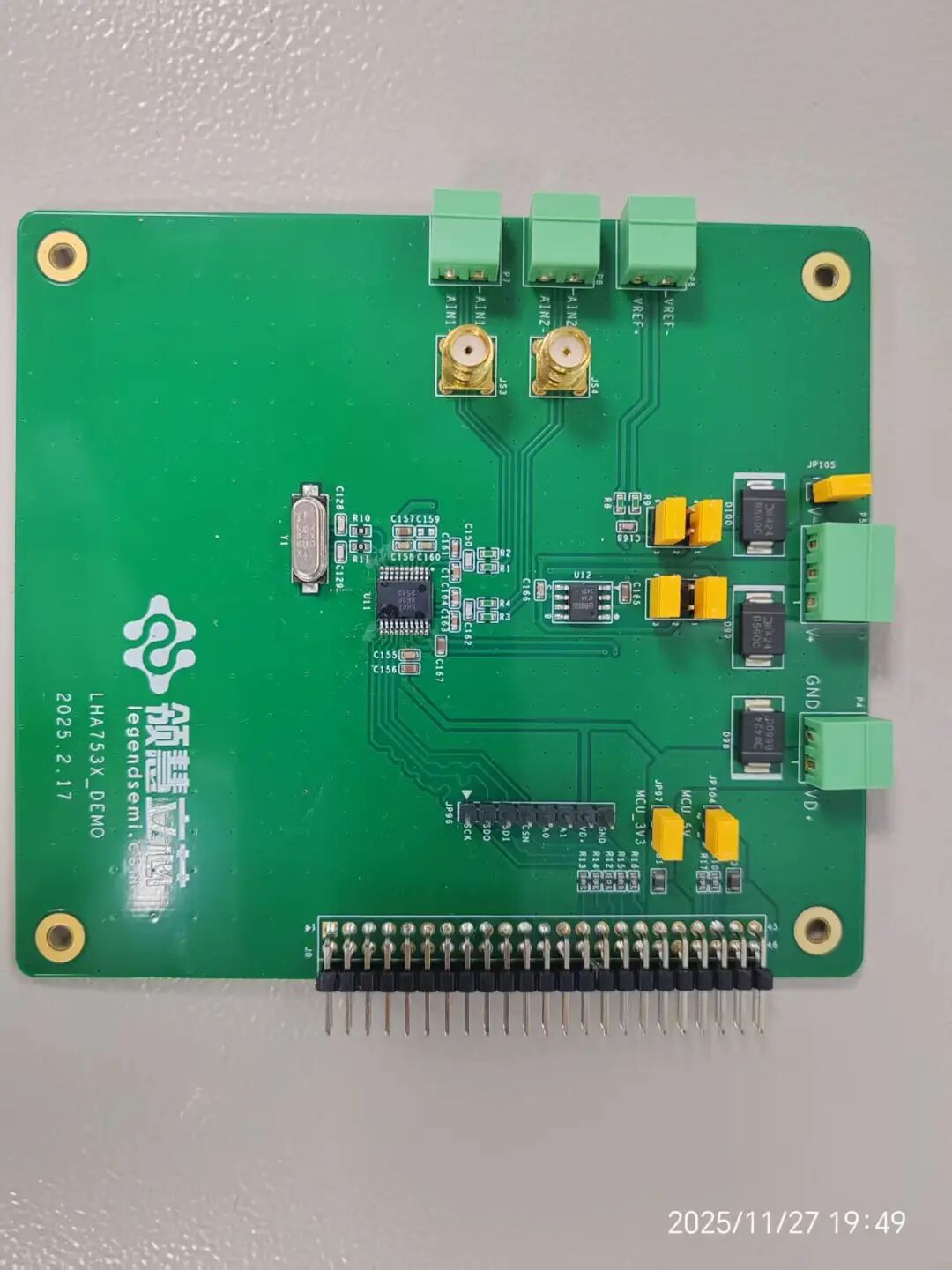

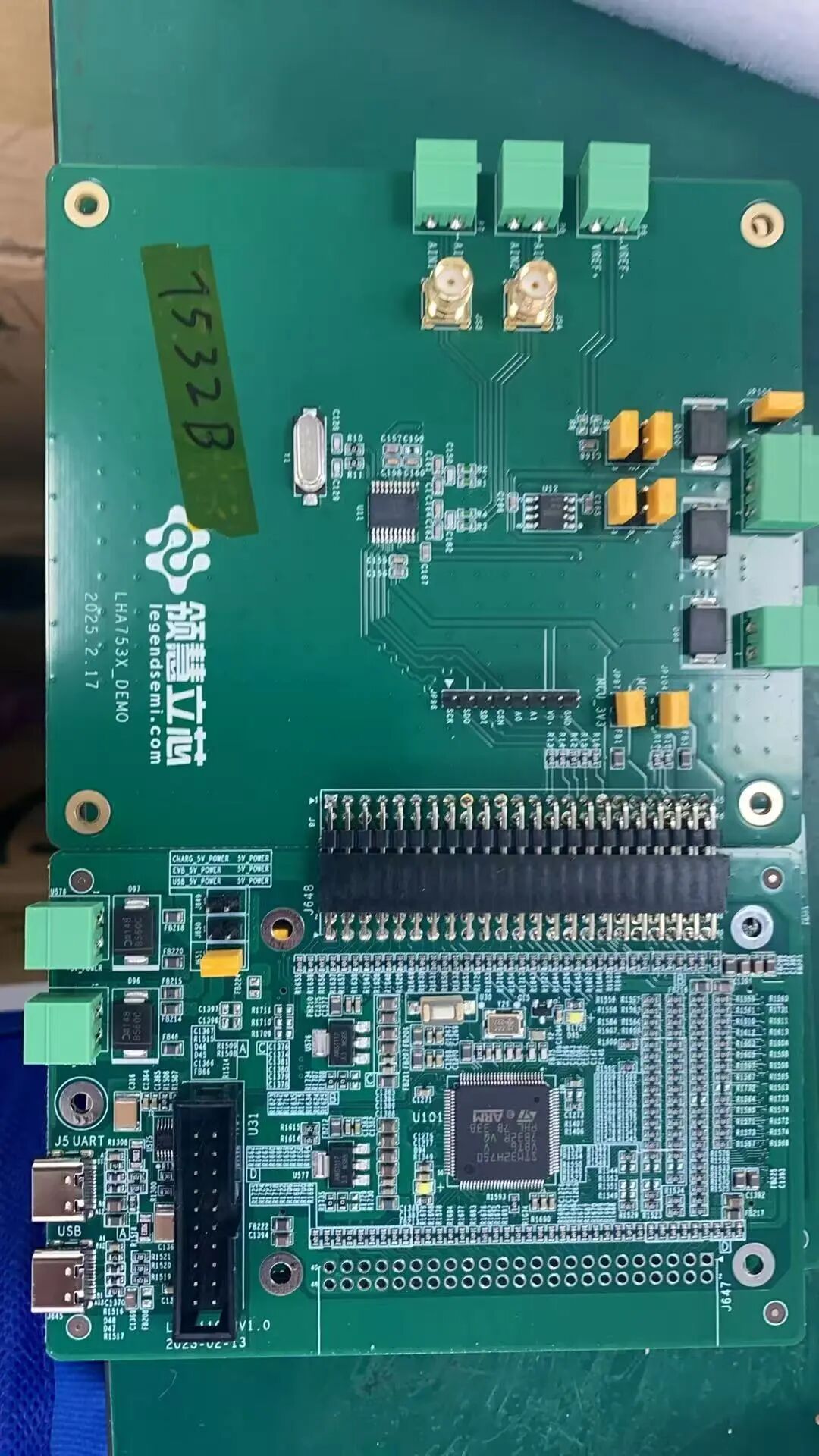

LHA 的板子很有辨识度

下面配的是 H7 的核心,挺大气,每次 demo 板都会给

模拟前端:INA + ΔΣ 的细节

前端仪表放大器

斩波稳定,等于自带“零 1/f 噪声”:在 0.1 Hz 处噪声密度 9.5 nV/√Hz,而且数据手册直接写 “No 1/f noise”,适合超低频 / DC 应用(如称重、压力)。

增益档位:64× 或 128×,由配置寄存器里的 VRS 位选择:

VRS=1:Gain=64 → 输入满量程 ±VREF/64

VRS=0:Gain=128 → 输入满量程 ±VREF/128

输入偏置电流 2 nA(CVF current),输入电流噪声 1 pA/√Hz;输入电容约 18 pF。

CVF current 2 nA 其实就是 sampling current:内部有采样电容和预充电结构,所以前端永远会有一个“小吸电流”,但量级很小。

输入范围和 VREF 的关系

满量程差分输入:,其中 Y=2(VRS=0)、Y=1(VRS=1)。

举例:VREF=2.5 V

Gain=64:±2.5/64 ≈ ±39 mV

Gain=128:±2.5/128 ≈ ±19.5 mV

通过数字增益寄存器还能再缩小到 1 mV 满量程级别(数字等效放大)。

共模范围:AIN+、AIN- 各自可在 VA-~VA+ 之间摆动,只要差分量落在上述满量程内即可,这对桥式传感器 + 中点偏置特别友好。

精度指标:线性、噪声和“有效 bit 数”

静态精度

线性误差:1.5 ppm/FSR(典型),24 bit 无失码。

偏置:±0.2 μV,温漂 1 nV/°C;增益误差 0.005%,漂移 0.5 ppm/°C —— 典型 ΣΔ 高精度 ADC + 校准后的水平。

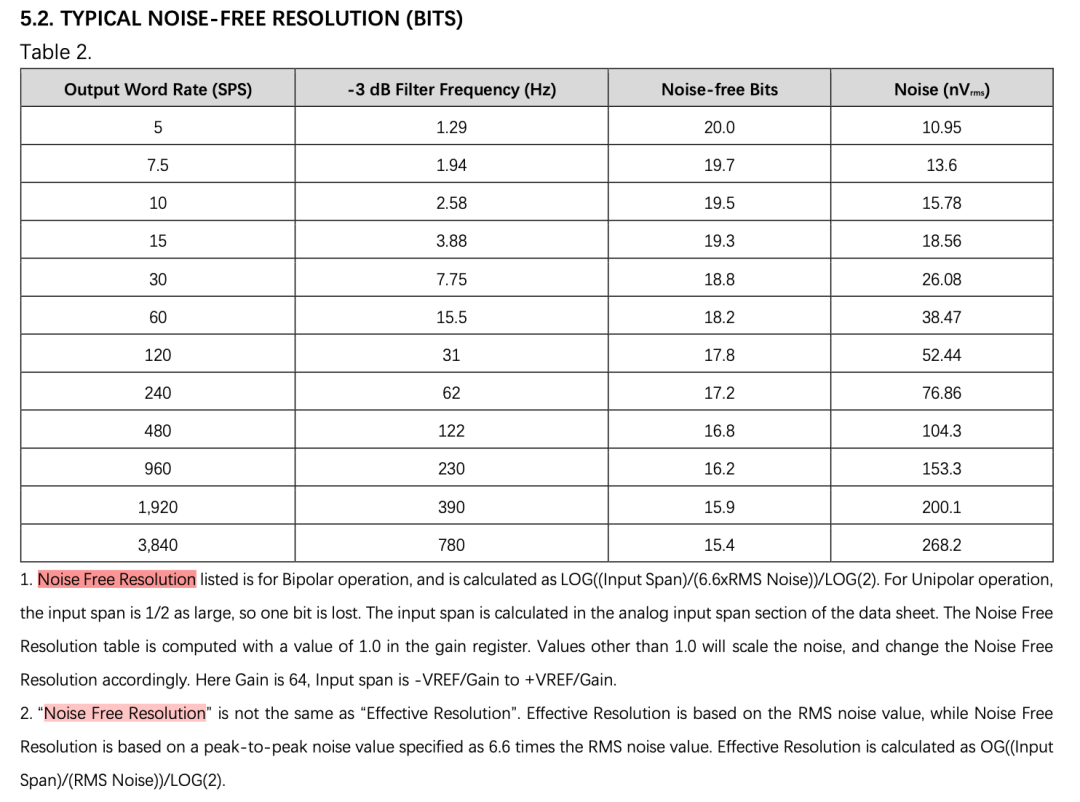

噪声-free 分辨率(表 2)

噪声-free 分辨率(表 2)

以双极性、Gain=64 为例(OWR=60 SPS,MCLK=4.9152 MHz):

60 SPS:噪声-free 18.2 bit,对应输入 RMS 噪声 ~38 nVrms

5 SPS:可到 20 bit,噪声 ~11 nVrms

注意这里是 放大后的等效输入噪声。对于称重场景,几十 nV 级的噪声,配 ±39 mV 满量程,理论可做到5~6 位有效计数头(10^5 级别的分辨率)是合理的。

表里还明确区分:

Noise Free Resolution:按 6.6×RMS(峰-峰)算,噪声更保守;

Effective Resolution:按 RMS 噪声算,数值会比 noise-free 高约 2.7 bit。

数字滤波 & 采样率

滤波结构

调制器采样率 。

3200 / 3840 SPS:只用一个 Sinc5 滤波器。

其它 SPS:Sinc5 + Sinc3 级联,Sinc3 有可编程抽取比 D=3840/OWR 或 3200/OWR。

120 SPS 时的幅频特性:−3 dB 点约 31 Hz(对应表 2);相位是线性的,保证线性相位(整形滤波不会产生相位畸变)。

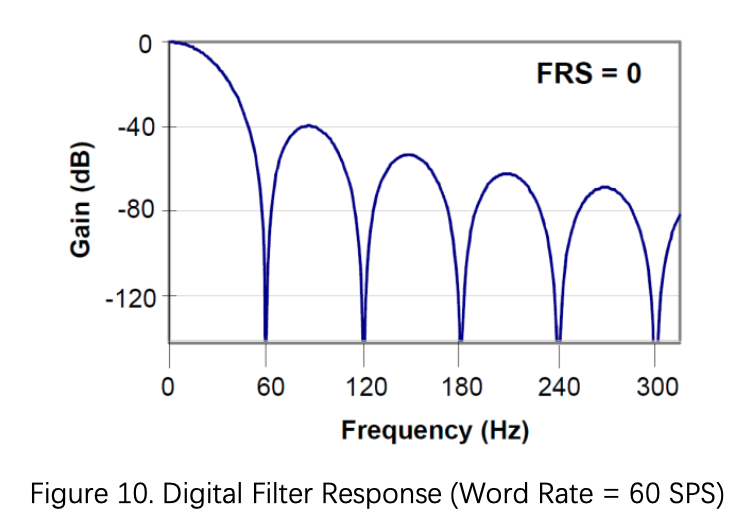

60 SPS 的响应图(图 10)

60 SPS 的响应图(图 10)

可以看到典型 sinc^5 型主瓣 + 很深的 50/60 Hz 零点:特别适合工频环境下的称重。

450/60 Hz 抑制

靠两种手段:

Sinc 滤波器的零点安排在 50/60 Hz 多个整数倍;FRS 位(Filter Rate Select)可以整体乘 5/6,把整套 OWR + 零点位置从 60 Hz 系统挪到 50 Hz 系统。

我们来进一步的对比

方向 | CS5530 | LHA7530 |

|---|---|---|

前端结构 | 经典斩波 INA 64×(不可改) | 斩波 INA + 64/128× |

噪声 | 更低(业内曾经标杆) | 略高 |

采样结构 | 老式 ΔΣ + 预充 | 新一代 ΔΣ + 更优化的 pre-charge |

输入范围 | ±19mV / ±39mV | ±19mV / ±39mV(完全相同) |

数字特性 | 早期设计,功能少 | 控制更多、寄存器更现代化 |

抗工频 | 强(典型 Sinc5+Sinc3) | 强(但滤波更可调) |

应用风格 | 精密秤、仪表、超低速测量 | 需要速度 + 精度的现代系统 |

LHA 在 2025 看来设计的确实现代了不少。

滤波器,LHA的滤波器是兼顾50和60的

仿真设定

模拟一颗 4.9152 MHz 时钟的 ΔΣ ADC:

调制器采样率:

目标输出数据率:ODR = 60 SPS→ 总抽取比:

CS5530 风格:只有 sinc5

直接用一个抽取比 R=10240 的 sinc 滤波器。

幅频公式(CIC):

LHA7530 风格:sinc5 + sinc3 级联

为了直观,假设(和很多 ADC 类似):

先用 sinc、抽取到 240 SPS:

再用 sinc、再抽 4 倍到 60 SPS:

总响应:

LHA7530 的 50 Hz 模式(FRS=5/6)

把 ODR 改成 50 SPS(总抽取比 12288),并重新拆成 R1/R2(这里演示设成 200SPS→50SPS);这样零点从 60、120…Hz 这一族“搬”到 50、100…Hz。

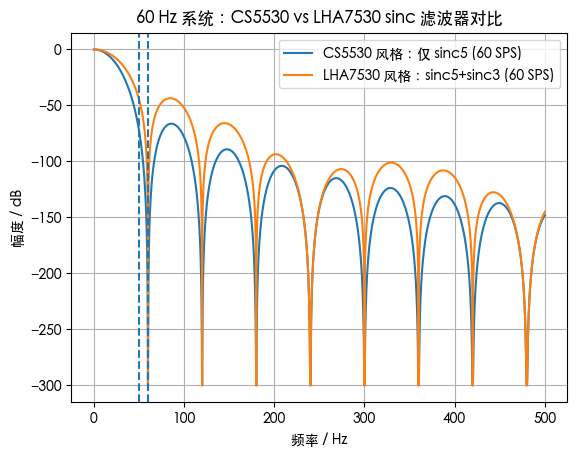

60 Hz 系统下 sinc5 vs sinc5+sinc3

60 Hz 系统下 sinc5 vs sinc5+sinc3

看第一张图(60 SPS,两条曲线):

CS5530:单 sinc

在 60 Hz、120 Hz、180 Hz… 等点上出现明显深零点(约 −150 dB);主瓣较宽,从 DC 到几十 Hz 的滚降比较平缓;对于接近 30–40 Hz 的信号,幅度已经开始衰减。

LHA7530:sinc+sinc

也在 60 Hz 整数倍处有深零点,同样对 60 Hz 工频有极强抑制;由于多了一个 sinc,主瓣更窄、过渡带更陡:在 20–40 Hz 之间就已经明显开始下落,带外更快滚降;对于高于几十 Hz 的干扰(比如 100–300 Hz 机械振动 / EMC),抑制更强;这也对应数据手册里:在相同 ODR 下,LHA7530 的有效噪声带宽一般比 CS5530 小一些 → 噪声 slightly 更优,同时带外抑制更强。

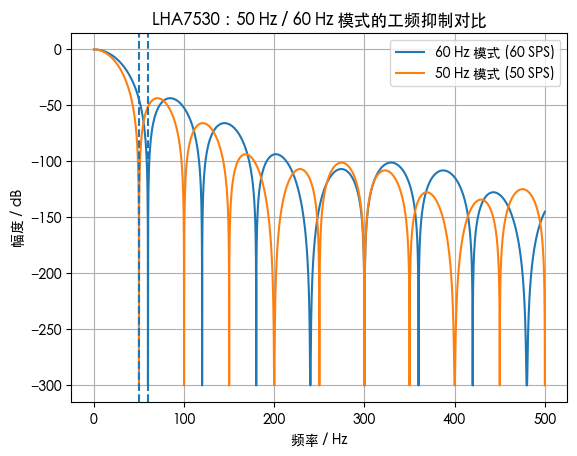

LHA7530 50 Hz / 60 Hz 模式对工频的影响

LHA7530 50 Hz / 60 Hz 模式对工频的影响

橙色:60 Hz 模式(ODR=60 SPS),零点在 60、120、180…Hz,对 60 Hz 电网环境的抑制极深(那根纵虚线就是 60Hz)

蓝色:50 Hz 模式(ODR=50 SPS),零点整体“左移”到 50、100、150…Hz,对 50 Hz 工频抑制极深,对 60 Hz 变差

这就是数据手册里 FRS 位(5/6)干的事:

60 Hz 电网国家(美国、日本 60Hz 区)→ 设为 60 系统

50 Hz 电网国家(欧洲、中国大部分地区)→ 设为 50 系统

核心不是 ODR 是多少,而是:把 Sinc 零点精准对准工频。

两颗芯片在滤波器上的“性格差异”

结合仿真 + 数据手册,可以归纳成:

CS5530

典型 sinc 结构,零点就落在 k·ODR。

由于没有第二级 sinc,主瓣更宽 → 对“有点动态”的信号更宽容;在低速档,通过提高 OSR 获得极低噪声。

LHA7530

sinc + sinc 级联,整体过渡带更陡、带外抑制更强;同样可以把零点对准 50/60Hz,但还能通过 WR/FRS 灵活调整带宽;对工频、谐波、电机噪声的抑制更强,适合工业现场恶劣环境。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2025-11-29,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录