使用Modelsim中的2到1 mux生成的4到1 mux的输出问题

使用Modelsim中的2到1 mux生成的4到1 mux的输出问题

提问于 2019-07-04 19:54:39

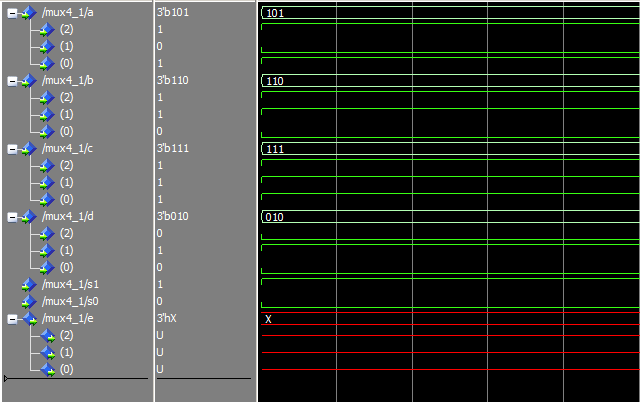

在成功地使用下面代码的Modelsim编译和仿真之后(这只是使用两个2到1个mux构建的一个简单的4到1个mux),我运行了一个波形测试,看看它会是什么样子,输出一直处于U状态,而不管输入的值如何,下面是代码和结果:

a. 2到1 mux的代码:

entity mux2_1 is

port( a,b:in std_logic_vector(2 downto 0);

s:in std_logic;

e:out std_logic_vector(2 downto 0));

end mux2_1;

architecture wx of mux2_1 is

begin

process

begin

if(s='0') then

e<=a;

else

e<=b;

end if;

wait;

end process;

end wx;b. 4到1 mux的代码:

entity mux4_1 is

port( a,b,c,d:in std_logic_vector(2 downto 0);

s1,s0:in std_logic;

e :out std_logic_vector (2 downto 0));

end mux4_1;

architecture nj of mux4_1 is

signal t1,t2:std_logic_vector (2 downto 0);

begin

k1: entity work.mux2_1 port map (a,b,s0,t1);

k2: entity work.mux2_1 port map (c,d,s0,t2);

k3: entity work.mux2_1 port map (t1,t2,s1,e);

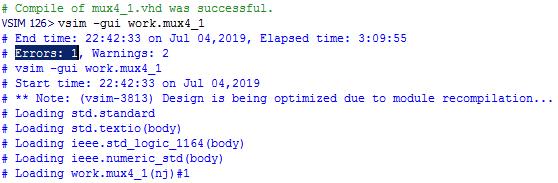

end nj;下面是模拟后的控制台报告:

最后,输出不一致的波形:

回答 2

Stack Overflow用户

回答已采纳

发布于 2019-07-07 18:54:21

我相信这个错误是由于你2:1的穆X中的“等待”语句造成的。请把它移开。

这里有一个附带说明:只在testbench中尽可能多地使用等待语句。由于等待是不可综合的,您会遇到一些错误。

谢谢

Stack Overflow用户

发布于 2019-07-05 15:00:13

首先,我建议您从其他人那里阅读一些VHDL代码,并尝试理解他们正在做什么。您所拥有的是代码,它将完成一些事情,但不一定是您希望它做的。当人们开始VHDL编码时,会犯一个很大的错误,那就是认为它是软件,它可以和软件一样编程,但实际上并非如此。要想更好地编写VHDL编码,就必须考虑硬件和代码声明的逻辑。

等待语句是一个问题。应该使用wait语句的唯一位置是在testbench中,因为它们不能映射到逻辑单元格。因此,您想要做的是删除等待语句并创建一个进程敏感性列表(在这里,您甚至不需要它,但这是一个很好的实践)。

p_MUX_2x1 : process (a, b, s)

begin

if (s = '0') then

e <= a;

else

e <= b;

end if;

end process p_MUX_2x1;页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/56893669

复制相关文章

相似问题