数组中求最小值的问题

数组中求最小值的问题

提问于 2018-12-26 10:29:18

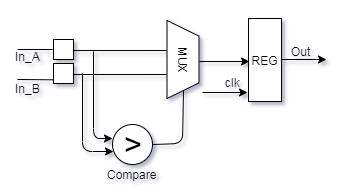

我试图找到一个包含19个VHDL值的“数组”的最小值。这19个值由J0表示为J18,并用作我的Find_min_v3模块的输入。下面的结构(在图中)用于比较两个输入,输出存储在REG中。大量结构的使用将导致通知。

“Netlist 29-101 Netlist‘模块’对于布局规划来说并不理想,因为单元视图‘模块’包含大量原语。如果你想做地板规划,请考虑在综合中启用层次结构。“

我有两个问题:

1.为什么它包含了许多原语,导致不太适合于城市规划。

2.如何优化连接的无数结构,以求数组的最小值?或者您有其他方法来找到最小值吗?

这是我的密码

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity Find_min_v3 is

Port ( i_clk : in STD_LOGIC;

reset : in STD_LOGIC;

EN_RUNNING : in STD_LOGIC;

J0 : in STD_LOGIC_VECTOR (11 downto 0);

J1 : in STD_LOGIC_VECTOR (11 downto 0);

J2 : in STD_LOGIC_VECTOR (11 downto 0);

J3 : in STD_LOGIC_VECTOR (11 downto 0);

J4 : in STD_LOGIC_VECTOR (11 downto 0);

J5 : in STD_LOGIC_VECTOR (11 downto 0);

J6 : in STD_LOGIC_VECTOR (11 downto 0);

J7 : in STD_LOGIC_VECTOR (11 downto 0);

J8 : in STD_LOGIC_VECTOR (11 downto 0);

J9 : in STD_LOGIC_VECTOR (11 downto 0);

J10 : in STD_LOGIC_VECTOR (11 downto 0);

J11 : in STD_LOGIC_VECTOR (11 downto 0);

J12 : in STD_LOGIC_VECTOR (11 downto 0);

J13 : in STD_LOGIC_VECTOR (11 downto 0);

J14 : in STD_LOGIC_VECTOR (11 downto 0);

J15 : in STD_LOGIC_VECTOR (11 downto 0);

J16 : in STD_LOGIC_VECTOR (11 downto 0);

J17 : in STD_LOGIC_VECTOR (11 downto 0);

J18 : in STD_LOGIC_VECTOR (11 downto 0);

J_Min_out : OUT STD_LOGIC_VECTOR (11 downto 0)

);

end Find_min_v3;

architecture Behavioral of Find_min_v3 is

TYPE J_type IS ARRAY (0 to 18) OF SIGNED(11 downto 0) ;

SIGNAl r_J : J_type;

SIGNAl out_min_stage1_0 : SIGNED (11 downto 0);

SIGNAl out_min_stage1_1 : SIGNED (11 downto 0);

SIGNAl out_min_stage1_2 : SIGNED (11 downto 0);

SIGNAl out_min_stage1_3 : SIGNED (11 downto 0);

SIGNAl out_min_stage1_4 : SIGNED (11 downto 0);

SIGNAl out_min_stage1_5 : SIGNED (11 downto 0);

SIGNAl out_min_stage1_6 : SIGNED (11 downto 0);

SIGNAl out_min_stage1_7 : SIGNED (11 downto 0);

SIGNAl out_min_stage1_8 : SIGNED (11 downto 0);

SIGNAl out_min_stage1_9 : SIGNED (11 downto 0);

SIGNAl out_min_stage2_0 : SIGNED (11 downto 0);

SIGNAl out_min_stage2_1 : SIGNED (11 downto 0);

SIGNAl out_min_stage2_2 : SIGNED (11 downto 0);

SIGNAl out_min_stage2_3 : SIGNED (11 downto 0);

SIGNAl out_min_stage2_4 : SIGNED (11 downto 0);

SIGNAl out_min_stage3_0 : SIGNED (11 downto 0);

SIGNAl out_min_stage3_1 : SIGNED (11 downto 0);

SIGNAl out_min_stage3_2 : SIGNED (11 downto 0);

SIGNAl out_min_stage4_0 : SIGNED (11 downto 0);

SIGNAl out_min_stage4_1 : SIGNED (11 downto 0);

SIGNAl out_min_stage5_0 : SIGNED (11 downto 0);

BEGIN

r_J(0) <= signed(J0) WHEN EN_RUNNING ='1';

r_J(1) <= signed(J1) WHEN EN_RUNNING ='1';

r_J(2) <=signed(J2) WHEN EN_RUNNING ='1';

r_J(3) <=signed(J3) WHEN EN_RUNNING ='1';

r_J(4) <=signed(J4) WHEN EN_RUNNING ='1';

r_J(5) <=signed(J5) WHEN EN_RUNNING ='1';

r_J(6) <=signed(J6) WHEN EN_RUNNING ='1';

r_J(7) <=signed(J7) WHEN EN_RUNNING ='1';

r_J(8) <=signed(J8) WHEN EN_RUNNING ='1';

r_J(9) <=signed(J9) WHEN EN_RUNNING ='1';

r_J(10) <=signed(J10) WHEN EN_RUNNING ='1';

r_J(11) <=signed(J11) WHEN EN_RUNNING ='1';

r_J(12) <=signed(J12) WHEN EN_RUNNING ='1';

r_J(13) <=signed(J13) WHEN EN_RUNNING ='1';

r_J(14) <=signed(J14) WHEN EN_RUNNING ='1';

r_J(15) <=signed(J15) WHEN EN_RUNNING ='1';

r_J(16) <=signed(J16) WHEN EN_RUNNING ='1';

r_J(17) <=signed(J17) WHEN EN_RUNNING ='1';

r_J(18) <=signed(J18) WHEN EN_RUNNING ='1';

-------stage1

STAGGE1_0: PROCESS (i_clk,reset)

BEGIN

IF (RISING_EDGE(i_clk)) THEN

IF (reset ='0') THEN

--out_ind_stage1_0 <= (others => '0');

out_min_stage1_0 <= (others => '0');

out_min_stage1_0 <= (others => '0');

out_min_stage1_1 <= (others => '0');

out_min_stage1_2 <= (others => '0');

out_min_stage1_3 <= (others => '0');

out_min_stage1_4 <= (others => '0');

out_min_stage1_5 <= (others => '0');

out_min_stage1_6 <= (others => '0');

out_min_stage1_7 <= (others => '0');

out_min_stage1_8 <= (others => '0');

out_min_stage1_9 <= (others => '0');

out_min_stage2_0 <= (others => '0');

out_min_stage2_1 <= (others => '0');

out_min_stage2_2 <= (others => '0');

out_min_stage2_3 <= (others => '0');

out_min_stage2_4 <= (others => '0');

out_min_stage3_0 <= (others => '0');

out_min_stage3_1 <= (others => '0');

out_min_stage3_2 <= (others => '0');

out_min_stage4_0 <= (others => '0');

out_min_stage4_1 <= (others => '0');

out_min_stage5_0 <= (others => '0');

ELSE

IF (r_J(1)>r_J(0)) THEN

out_min_stage1_0 <= r_J(0);

ELSE

out_min_stage1_0 <= r_J(1);

END IF;

IF (r_J(3)>r_J(2)) THEN

out_min_stage1_1 <= r_J(2);

ELSE

out_min_stage1_1 <= r_J(3);

END IF;

IF (r_J(5)>r_J(4)) THEN

out_min_stage1_2 <= r_J(4);

ELSE

out_min_stage1_2 <= r_J(5);

END IF;

IF (r_J(7)>r_J(6)) THEN

out_min_stage1_3 <= r_J(6);

ELSE

out_min_stage1_3 <= r_J(7);

END IF;

IF (r_J(9)>r_J(8)) THEN

out_min_stage1_4 <= r_J(8);

ELSE

out_min_stage1_4 <= r_J(9);

END IF;

IF (r_J(11)>r_J(10)) THEN

out_min_stage1_5 <= r_J(10);

ELSE

out_min_stage1_5 <= r_J(11);

END IF;

IF (r_J(13)>r_J(12)) THEN

out_min_stage1_6 <= r_J(12);

ELSE

out_min_stage1_6 <= r_J(13);

END IF;

IF (r_J(15)>r_J(14)) THEN

out_min_stage1_7 <= r_J(14);

ELSE

out_min_stage1_7 <= (r_J(15));

END IF;

IF (r_J(17)>r_J(16)) THEN

out_min_stage1_8 <= r_J(16);

ELSE

out_min_stage1_8 <= r_J(17);

END IF;

out_min_stage1_9 <= r_J(18);

---------

IF (out_min_stage1_0)> out_min_stage1_1 THEN

out_min_stage2_0 <= out_min_stage1_1;

ELSE

out_min_stage2_0 <= out_min_stage1_0;

END IF;

IF (out_min_stage1_2)>(out_min_stage1_3) THEN

out_min_stage2_1 <= (out_min_stage1_3);

ELSE

out_min_stage2_1 <= (out_min_stage1_2);

END IF;

IF (out_min_stage1_4)>out_min_stage1_5 THEN

out_min_stage2_2 <= (out_min_stage1_5);

ELSE

out_min_stage2_2 <= (out_min_stage1_4);

END IF;

IF (out_min_stage1_6)>(out_min_stage1_7) THEN

out_min_stage2_3 <= (out_min_stage1_7);

ELSE

out_min_stage2_3 <= (out_min_stage1_6);

END IF;

IF (out_min_stage1_8)>out_min_stage1_9 THEN

out_min_stage2_4 <= (out_min_stage1_9);

ELSE

out_min_stage2_4 <= (out_min_stage1_8);

END IF;

---------STAGE3

IF (out_min_stage2_0)>out_min_stage2_1 THEN

out_min_stage3_0 <= (out_min_stage2_1);

ELSE

out_min_stage3_0 <= (out_min_stage2_0);

END IF;

IF (out_min_stage2_2)>(out_min_stage2_3) THEN

out_min_stage3_1 <= (out_min_stage2_3);

ELSE

out_min_stage3_1 <= (out_min_stage2_2);

END IF;

out_min_stage3_2 <= (out_min_stage2_4);

-------------STAGE4

IF (out_min_stage3_1)>out_min_stage3_0 THEN

out_min_stage4_0 <= (out_min_stage3_0);

ELSE

out_min_stage4_0 <= (out_min_stage3_1);

END IF;

out_min_stage4_1 <= (out_min_stage3_2);

-------------STAGE5

IF (out_min_stage4_0)>(out_min_stage4_1)THEN

out_min_stage5_0 <= (out_min_stage4_1);

ELSE

out_min_stage5_0 <= (out_min_stage4_0);

END IF;

J_Min_out <= STD_LOGIC_VECTOR(out_min_stage5_0);

END IF;

END IF;

END PROCESS;

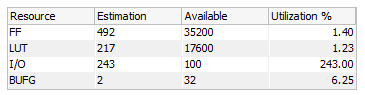

end Behavioral;这是使用报告

回答 1

Stack Overflow用户

发布于 2018-12-30 17:13:38

听起来你正在通过综合,但击中这个问题的位置和路线?这可能是因为您正在使用的设备中的IOs数量。(243人只需要100人)。

还有几件事情在看代码。

您不需要在进程敏感列表中重置。

我不知道你为什么需要有条件的类型转换。为什么不直接进行类型转换而不查看运行信号?

这个实现需要几个时钟周期来计算结果。希望延迟在应用程序中是可以接受的。

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/53930770

复制相关文章

相似问题