将多个FiFos连接到一个FiFo

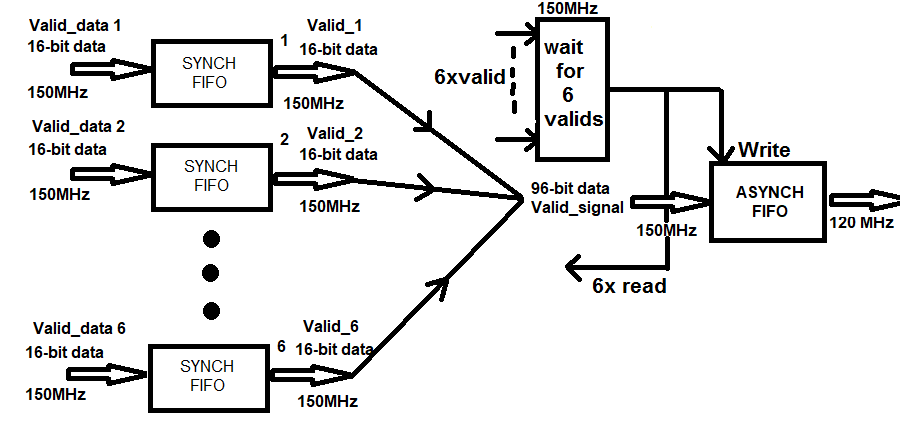

我的verilog固件的图表如下:

在我的图表中,我有6个16位数据和6个valid_data是由生成函数生成的6个相同模块的输出。valid_data的功能是在16位数据写入Xilinx提供的FiFo (本地和IP核)时发出通知。因为我的固件中有两个时钟域,所以我使用同步FiFo作为两个时钟域之间的握手,以确保在时钟域120 MHz中正确地获得6 16位数据。

在此之后,我将6个16位数据从6个同步FiFo输出到一个96位变量。我想使用来自6个同步FiFo的6个有效信号来生成新的有效信号,通知异步FiFo,96位数据已经准备好写入异步FiFo。但我有一个问题:

我认为6位16位数据同时进入FIFO,所以同步输出的Fifo需要同时出现。,但是当我使用chipscope检查有效信号时,我不明白为什么发出的有效信号在数字上不同时,这使我很难生成新的有效信号。有人可以告诉我发生这种事的原因。

6个Fifos的有效信号和Chipscope检查的新有效信号

_有效校验85:81是6来自6 FiFos的有效信号。

_ check_ir_valid是累积6个有效信号的变量

_ valid_to_fifo是新的有效信号。

由于6个有效信号不同时出现,所以我也想了另一个方法这样也用一个6位变量来累积6个有效信号。当这个变量从FiFo收集足够的6个有效信号时,这意味着6位变量等于6'h3F,我将获得异步FiFo的新有效信号。这种方法有什么潜在的风险吗?

回答 1

Stack Overflow用户

发布于 2018-01-31 12:46:35

我想我知道你想做什么,但图表和文本有些不完整,有些地方令人困惑。

第一:

在图中,您将显示输入时钟为150 and和输出时钟为120 and的同步FIFO。这不可能!同步FIFO读写端口上的时钟在频率和相位上必须相同。

但我认为你正在做的是等待每个FIFO有一个词,然后阅读,然后全部同时出来。关键是:所有六个FIFO都运行在同一个150 The时钟上吗?如果是这样的话,您可以使您刚才描述的逻辑,它应该运行在150 the的时钟。由此产生一个单一的读取脉冲,从同步FIFO中获取数据,并将它们写入异步FIFO。

我已经将您的图表更改为我认为您需要实现的内容:

请注意,只有在以下情况下才有效:

- 150个MHz时钟都是一样的。

- 输入端的数据速率不太高。(有效时间最长为120/150 )

发布编辑:

你还没有回答,如果150兆赫的时钟是相同的。如果没有,您应该使用6个异步FIFO。在这种情况下,终端FIFO可以从120 MHz时钟同步运行。

如果是同一个时钟,上面的方案就不那么逻辑了。

“等待六值”逻辑

无论您使用什么,“等待六种验证”逻辑必须能够接受任何或全部同时到达。我对这部分的逻辑有另一个问题。您的波形显示一个时钟周期的“有效”(可能,我不知道时钟在哪里)。我从来没见过这是来自FIFO的。

如果FIFO有一个“空”信号,那么只要至少有一个值可读取,它就会好得多,因为它仍然很低。当你能够阅读时,逻辑就变成了一个6输入的“NOR”门。

使用空信号

你的“有效”信号似乎只有一个周期是高的。这是很难工作的。大多数FIFO都有“满”和“空”之类的状态信号。在这种情况下,您需要检查所有FIFO是否都有数据(所有空信号都是0)。而不是你读到的。在Verilog中,它看起来是:

wire [5:0] empty;

wire can_read;

....

asyncfifo fifo1 (

....

.empty( empty[0] ),

asyncfifo fifo2 (

....

.empty( empty[1] ),

// The above for each FIFO

assign can_read = (empty==6'b000000);https://stackoverflow.com/questions/48537021

复制相似问题