VHDL设计中意想不到的结果

VHDL设计中意想不到的结果

提问于 2017-04-17 15:13:52

当所有的输入都是x和clk = 1时,它应该输出clk = 1的值,但是它没有。下面的代码有什么问题?

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

--This is a D Flip-Flop with Synchronous Reset,Set and Clock Enable(posedge clk).

--Note that the reset input has the highest priority,Set being the next highest

--priority and clock enable having the lowest priority.

ENTITY syn IS

PORT (

Q : OUT std_logic; -- Data output

CLK : IN std_logic; -- Clock input

Qpl : IN std_logic;

RESET : IN std_logic; -- Synchronous reset input

D : IN std_logic; -- Data input

SET : IN std_logic -- Synchronous set input

);

END syn;

ARCHITECTURE Behavioral OF syn IS --architecture of the circuit.

BEGIN

--"begin" statement for architecture.

PROCESS (CLK) --process with sensitivity list.

BEGIN

--"begin" statment for the process.

IF (CLK'EVENT AND CLK = '1') THEN --This makes the process synchronous(with clock)

IF (RESET = '1') THEN

Q <= '0';

ELSE

IF (SET = '1') THEN

Q <= D;

ELSE

Q <= Qpl;

END IF;

END IF;

END IF;

END PROCESS; --end of process statement.

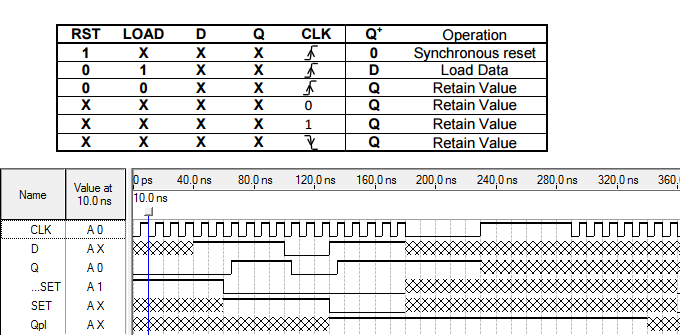

END Behavioral;下图显示了上述设计的波形,以及所需的操作要求;

回答 2

Stack Overflow用户

回答已采纳

发布于 2017-04-17 15:36:53

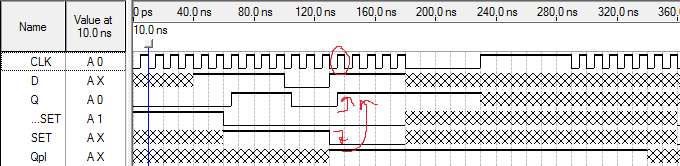

从波形图上看,似乎一切正常,当输入信号SET变为U时,if条件无法求值,因此输出Q也是如此,即U。您可以看到,当SET是0时,输出Q正确地得到了Qpl的值。

很抱歉绘制了粗图,但是当SET是0时,您可以看到圆圈时钟在上升,Q得到了预期的Qpl值。只有在SET信号变成U后,输出Q在下一个时钟上升事件中也失去了它的值,也变成了U。

Stack Overflow用户

发布于 2017-04-18 09:35:26

代码和注释不同。表/图也是如此。D触发器/寄存器是一个非常简单的组件。示例:

entity dff is

port (

clk : in std_logic;

rst : in std_logic;

set : in std_logic;

load : in std_logic;

d : in std_logic;

q : out std_logic

);

architecture rtl of dff is

begin

dff_proc : process(clk)

begin

if rising_edge(clk) then

if rst='1' then

q <= '0';

elsif set='1' then

q <= '1';

elsif load='1' then

q <= d;

end if;

end if;

end process;

end architecture;页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/43454211

复制相关文章

相似问题