在模拟过程中信号值不会被初始化

我们有一个大学项目,我们必须模拟一个用于DSP的MAC单元。对于模拟,我使用Aldec Riviera Pro 2014.06通过EDA操场。问题是,即使我初始化了一个名为add_res的32位签名信号,但在模拟时,它的值将始终显示为XXXX_XXXX。

这是design.vhd的代码

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

USE IEEE.numeric_std.all;

-----------------------------

ENTITY mac IS

PORT (B, C : IN SIGNED (15 DOWNTO 0);

clk : IN STD_LOGIC;

A : OUT SIGNED (31 DOWNTO 0));

END mac;

-----------------------------

ARCHITECTURE mac_rtl OF mac IS

SIGNAL mul_res: SIGNED (31 DOWNTO 0);

SIGNAL add_res: SIGNED (31 DOWNTO 0) := (others => '0');

BEGIN

mul_res <= B * C;

PROCESS (clk)

BEGIN

A <= mul_res + add_res;

add_res <= A;

END PROCESS;

END mac_rtl;这是testbench.vhd的代码

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

entity testbench is

end entity testbench;

architecture BENCH of testbench is

component mac is

port (B, C : in SIGNED (15 DOWNTO 0);

clk : in STD_LOGIC;

A : out SIGNED (31 DOWNTO 0));

end component;

signal StopClock : BOOLEAN;

signal clk : STD_LOGIC;

signal B, C : SIGNED (15 DOWNTO 0);

signal A : SIGNED (31 DOWNTO 0);

begin

ClockGenerator: process

begin

clk <= '0';

wait for 2 ns;

while not StopClock loop

clk <= '0';

wait for 1 ns;

clk <= '1';

wait for 1 ns;

end loop;

wait;

end process ClockGenerator;

Stimulus: process

begin

B <= "0000000000000010";

C <= "0000000000001000";

wait;

end process Stimulus;

DUT : entity work.mac

port map (B, C, clk, A);

end architecture BENCH;我在这里和谷歌搜索过其他有同样问题的人,但是给出的解决方案没有帮助。

我试过并使用了testbench中的重置变量,但什么也没有。这就像它根本不会被初始化,而其他的一切都正常工作。

回答 1

Stack Overflow用户

发布于 2017-02-25 02:05:52

问题是,在将add_res和mul_res加载到寄存器时,必须知道add_res和add_res的值。

请注意,进程对clk很敏感,但不使用边缘,也不限定clk的值。

我修改了您的体系结构,将add_res更新限定为clk的上升边缘。当时在mult_res上有一个内置的假设,即非元值。这可以部分地通过定义默认值来处理。

另外,在信号被更新之前,A的新值是不可用的,而在当前的模拟周期中,没有任何待处理的进程需要恢复。这意味着您需要分配给add_res (反正它保存了累积的值),并将其分配给进程外部的A:

ARCHITECTURE mac_rtl OF mac IS

SIGNAL mul_res: SIGNED (31 DOWNTO 0) := (others => '0'); -- added init val

SIGNAL add_res: SIGNED (31 DOWNTO 0) := (others => '0');

BEGIN

mul_res <= B * C;

PROCESS (clk)

BEGIN

if rising_edge(clk) then -- ADDED

-- A <= mul_res + add_res; CHANGED

add_res <= mul_res + add_res;

-- add_res <= A; CHANGED

end if; -- ADDED

END PROCESS;

A <= add_res;

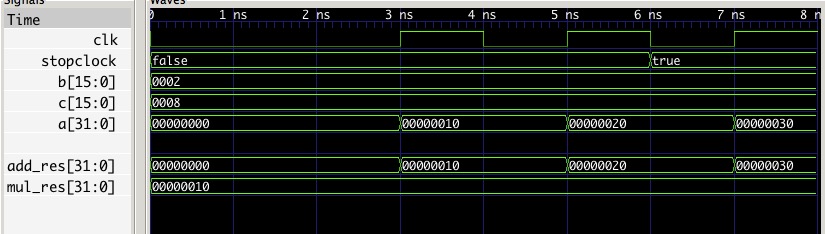

END mac_rtl;这就赋予了:

您可以注意到,没有必要尝试崩溃A和add_res。为了仿真目的,在0仿真时间过去后生效的信号分配引起的增量周期不要占用模拟时间。

调度的信号更新和增量循环用于模拟固有的按顺序分配的信号中的并发性。(是的,在修改后的体系结构中,分配给A的时间将比add_res晚一个增量周期)。

(是的,我将一个StopClock事务放在刺激的尾部,在testbench中的过程刺激中)。

https://stackoverflow.com/questions/42450709

复制相似问题