新手测试板凳,不能做头尾错误。(使用Icarus Verilog)

新手测试板凳,不能做头尾错误。(使用Icarus Verilog)

提问于 2016-06-09 06:10:51

我一直想得到这段我一时兴起的代码。在大多数情况下,我认为我相信模块本身是好的。是测试台把所有的错误都抛出来了。

下面是完整的代码:

/*

Primitive code to control a stepper motor using FPGA

It will run as a seconds hand

9 June 2016

dwiref024

*/

module clock_divider(clock, reset, clock_div);

input clock;

input reset;

output clock_div;

reg [25:0]counter = 26'd0;

// Assuming a clock frequency of 40Mhz

// log2(40M) = 25.25

// Therefore 40MHz corresponds to MOD25

always@(posedge clock, negedge reset) begin

if(!reset) begin

counter <= 26'd0;

end

if(counter == 26'd40000000) begin

counter <= 26'd0;

end

else begin

counter <= counter + 1;

end

end

assign clock_div = counter[24]; // Gives you a clock signal 'clock_div'of approximate frequency 1Hz

initial begin

$dumpvars(0, clock, reset, counter);

end

endmodule

module count_seconds (

input clock_div, reset

);

reg [5:0]seconds = 6'd0;

always@(posedge clock_div, negedge reset) begin

if (!reset) begin

seconds <= 0;

end

else if (seconds == 6'd60) begin

seconds <= 0;

end

else begin

seconds <= seconds + 1;

end

end

initial begin

$dumpvars (0, clock_div, seconds);

end

endmodule

module get_servo(

input clock_div,

output reg servoPin = 0,

output reg ding

);

always@(posedge clock_div) begin

if(clock_div)

ding <= 1;

else

ding <= 0;

end

always@(ding) begin

if (ding) begin

servoPin = 1'b1;

end

else servoPin = 1'b0;

end

initial begin

$dumpvars (0, servoPin);

end

endmodule

module clk_tb;

reg clock;

reg reset;

reg servoPin;

reg clock_div;

reg ding;

initial begin

clock = 0;

reset = 0;

repeat(2) #10 clock = ~clock;

reset = 1;

forever #10 clock = ~clock;

end

clock_divider DUT1 (clock, reset, clock_div);

get_servo DUT2 (clock_div, servoPin, ding);

initial begin

servoPin = 1'b1;

#1 clock_div = 1'b0;

$finish;

end

endmodule在运行时

$ icarusverilog -o servo servo.v我得到以下错误:

servo.v:105: error: reg clock_div; cannot be driven by primitives or continuous assignment.

servo.v:105: error: Output port expression must support continuous assignment.

servo.v:105: : Port 3 (clock_div) of clock_divider is connected to clock_div

servo.v:106: error: reg servoPin; cannot be driven by primitives or continuous assignment.

servo.v:106: error: Output port expression must support continuous assignment.

servo.v:106: : Port 2 (servoPin) of get_servo is connected to servoPin

servo.v:106: error: reg ding; cannot be driven by primitives or continuous assignment.

servo.v:106: error: Output port expression must support continuous assignment.

servo.v:106: : Port 3 (ding) of get_servo is connected to ding

6 error(s) during elaboration.我在这里跨板查看了一些问题,这些问题指定了在测试平台模块中使用reg的时间和地点,以避免出现这种情况:

<variable name> is not a valid l-value in foo这是我最先犯的错误之一。为了避免这种情况,我最终得到了这些。如果有人能指出这些错误的根源以及它们的来源,我可能会修复这个错误,并在这个过程中学到一些新的东西。

回答 1

Stack Overflow用户

回答已采纳

发布于 2016-06-09 07:02:21

信号clock_div、servoPin由多驱动驱动。您已经将servoPin作为来自get_servo模块和testbench ( clk_tb本身)的输出来驱动。这是违法的。

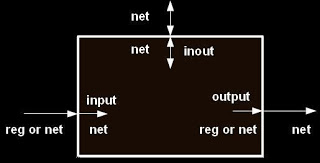

关于clock_div,请参阅下图:

模块的输出必须连接到线。在这里,clock_div是一个输出端口,对于clock_divider模块,它的必须是线型。然后,输出线可以用作逻辑驱动servoPin模块的输入。下面是testbench代码的一个片段:

reg clock;

reg reset;

reg servoPin;

// reg clock_div; // remove this

wire clock_div_w, clock_div_w2;

assign clock_div_w2 = clock_div_w; // drive output from one module to input to another

//...

clock_divider DUT1 (clock, reset, clock_div_w); // wire output

get_servo DUT2 (clock_div_w2, servoPin, ding); // another wire input

//...

initial begin

// servoPin = 1'b1; // donot drive from here, module output

#1 clock_div = 1'b0;

$finish;

end类似的注释也适用于ding端口。

关于IEEE 1800-2012,第23.3.3节:

每个端口连接应是连续分配的源到接收器,其中一个连接项应为信号源,另一个应为信号接收器。该分配应是从源到接收器的连续分配,用于输入或输出端口。

当端口在instantiation,中连接到任何其他端口时,它是一个常量赋值,因此它总是要求目标端口是一个.NET。

有关更多信息,请参考端口连接规则问题。

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/37718081

复制相关文章

相似问题