预期会有更广泛的RTL查看器

预期会有更广泛的RTL查看器

提问于 2016-05-17 10:12:53

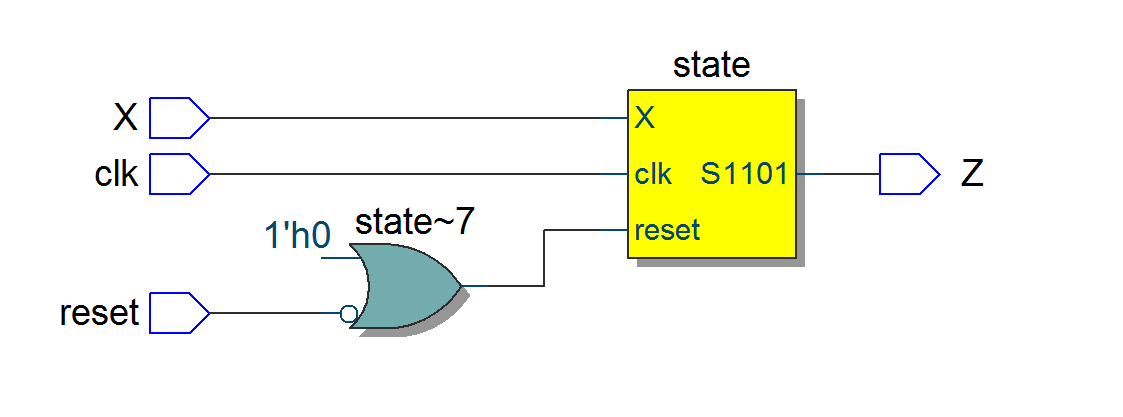

我合成了我的VHDL代码。当我看到RTL查看器时,我正期待着另一个结果。我使用VHDL代码构建了一个状态机(见下文),并得到了以下结果(见图)。有些事情我不明白:

1'h0是什么意思?state~7是什么意思?- 为什么只有一个块

state?其他州在哪里?

VHDL代码:

ENTITY state_machine IS

PORT ( clk: IN std_logic;

reset: IN std_logic;

X: IN BIT;

Z: OUT BIT);

END state_machine;

-- Present State Next State Output

-- X !X

-- Z

-- S0 S0 S1 0

-- S1 S0 S11 0

-- S11 S110 S11 0

-- S110 S0 S1101 0

-- S1101 S0 S11 1

ARCHITECTURE behaviour OF state_machine IS

TYPE states IS (S0, S1, S11, S110, S1101);

SIGNAL state : states;

BEGIN

next_state : PROCESS(reset, clk)

BEGIN

IF reset='0' THEN

state <= S0;

ELSIF rising_edge(clk) THEN

CASE state IS

WHEN S0 =>

IF X='0' THEN

state<=S1;

END IF;

WHEN S1 =>

IF X='0' THEN

state<=S11;

ELSE

state<=S0;

END IF;

WHEN S11 =>

IF X='0' THEN

state<=S11;

ELSE

state<=S110;

END IF;

WHEN S110 =>

IF X='0' THEN

state<=S1101;

ELSE

state<=S0;

END IF;

WHEN S1101 =>

IF X='0' THEN

state<=S11;

ELSE

state<=S0;

END IF;

END CASE;

END IF;

END PROCESS;

output:PROCESS(state)

BEGIN

CASE state IS

WHEN S0 => Z<='0';

WHEN S1 => Z<='0';

WHEN S11 => Z<='0';

WHEN S110 => Z<='0';

WHEN S1101 => Z<='1';

END CASE;

END PROCESS;

END behaviour;RTL原理图:

回答 1

Stack Overflow用户

回答已采纳

发布于 2016-05-17 10:58:22

查看器对常量使用Verilog表示法,Verilog中的1'h0与VHDL中的'0'相同。

OR门简单地命名为state~7,就像黄色框名为state一样。因此,OR门只是一个逆变器,所以复位到state块是not reset作为外部复位输入。

状态机设计的其余部分放在一个名为state的内部块中,因此如果双击它,它可能会扩展。当处于状态S1101时,state块上的S1101输出是断言的,因为只有那时才是Z输出'1'。

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/37273203

复制相关文章

相似问题