在Verilog中,我尝试使用$readmemb读取.txt文件,但它只在内存中加载xxxxx (不关心)

我需要以二进制方式加载一些数据的内存。我读到$readmemb可以用于这一点,甚至有一种方法可以使合成器可用。

因此,我创建了另一个名为RAM_IN的模块(它不是testbench模块)并“连接”到顶层模块。

在了解$readmemb之前,我使用了以下代码:

initial

begin

in_ram [0] <= 32'b11111111_000000000000000000000000;

in_ram [1] <= 32'b10010111_000000000000000000000000;

in_ram [2] <= 32'b00110110_000000000000000000000000;

in_ram [3] <= 32'b00111110_000000000000000000000000;

in_ram [4] <= 32'b00111111_000000000000000000000000;

in_ram [5] <= 32'b00111110_000000000000000000000000;

end但是这样写100个数字对我来说太累了,所以实现了这样的$readmemb:

module RAM_IN (pix_val, indx);

input [0:5] indx;

output [31:0] pix_val;

reg [31:0] pix_val;

reg [31:0] in_ram [0:4];

always @ (indx)

pix_val = in_ram [indx];

initial

begin

$readmemb("in_ram.txt", in_ram);

end读取此文件的目的,是最初将100个二进制值(模拟10x10图像的像素强度)逐一加载到顶部模块(该模块将在以后处理和吐出结果.)

我创建了一个.txt文件,它的内容与下面的内容完全相同

11111111000000000000000000000000

10010111000000000000000000000000

00110110000000000000000000000000

00111110000000000000000000000000

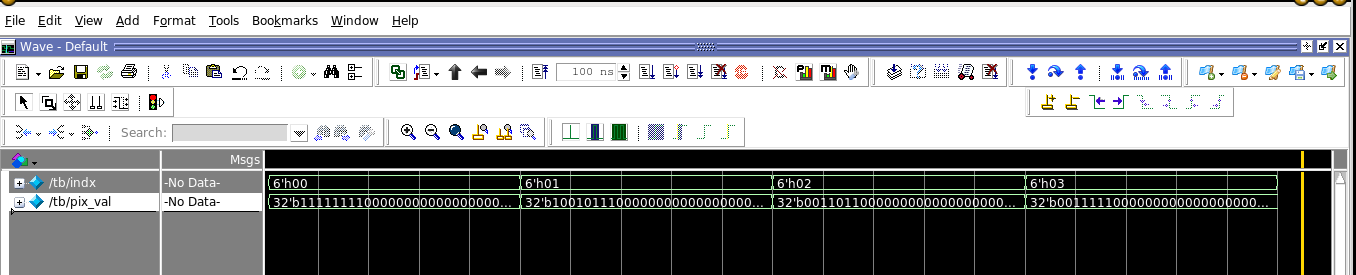

00111111000000000000000000000000 当我模拟时,modelsim向我展示了充满

我不知道我做错了什么。很可能不是处理.txt文件中的数字。也许是因为我打算在另一个不是testbench的模块中用$readmemb加载文件?

PD:这个填充内存的过程的模拟只是为了实际的目的,最后的目的是将顶层模块设计成一个完整的SoC,我认为我将使用QSYS。但我在这方面很新所以我还在学习。任何帮助都将不胜感激!

回答 4

Stack Overflow用户

发布于 2016-06-23 05:58:39

我已经修好了。问题是,modelsim找不到.txt文件,我不知道这些文件的预定位置在哪里,但是在互联网上,我发现我可以在Ram模块中声明如下的路径

initial

begin

$readmemb("C:/altera/15.0/Prueba5/in_ram.txt", in_ram);

end现在,modelsim正在加载正确的数据。谢谢大家。

Stack Overflow用户

发布于 2016-05-10 13:02:14

你确定你是在模拟吗?

您的TB代码:

module RAM_IN (pix_val, indx);

input [0:5] indx;

output [31:0] pix_val;

reg [31:0] pix_val;

reg [31:0] in_ram [0:4];

always @ (indx)

pix_val = in_ram [indx];

initial

begin

$readmemb("in_ram.txt", in_ram);

end

endmodule

module tb;

reg [0:5] indx;

wire [31:0] pix_val;

RAM_IN ram_in(pix_val, indx);

initial

begin

indx = 'b0;

$monitor ($realtime, " Read Data = %0b" ,pix_val);

repeat(4)

begin

#10;

indx = indx + 1'd1;

end

$finish;

end

endmodule用同样的in_ram.txt。

奎斯塔西姆:

QuestaSim-64 qverilog 10.4 Compiler 2014.12 Dec 2 2014

Start time: 18:27:01 on May 10,2016

qverilog me.v

-- Compiling module RAM_IN

-- Compiling module tb

Top level modules:

tb

Reading pref.tcl

# 10.4

# vsim -lib work tb -c -do "run -all; quit -f" -appendlog -l qverilog.log -vopt

# ** Note: (vsim-3812) Design is being optimized...

# // Questa Sim-64

# // Version 10.4 linux_x86_64 Dec 2 2014

# //

# // Copyright 1991-2014 Mentor Graphics Corporation

# // All Rights Reserved.

# //

# // THIS WORK CONTAINS TRADE SECRET AND PROPRIETARY INFORMATION

# // WHICH IS THE PROPERTY OF MENTOR GRAPHICS CORPORATION OR ITS

# // LICENSORS AND IS SUBJECT TO LICENSE TERMS.

# // THIS DOCUMENT CONTAINS TRADE SECRETS AND COMMERCIAL OR FINANCIAL

# // INFORMATION THAT ARE PRIVILEGED, CONFIDENTIAL, AND EXEMPT FROM

# // DISCLOSURE UNDER THE FREEDOM OF INFORMATION ACT, 5 U.S.C. SECTION 552.

# // FURTHERMORE, THIS INFORMATION IS PROHIBITED FROM DISCLOSURE UNDER

# // THE TRADE SECRETS ACT, 18 U.S.C. SECTION 1905.

# //

# Loading work.tb(fast)

# run -all

# 0 Read Data = 11111111000000000000000000000000

# 10 Read Data = 10010111000000000000000000000000

# 20 Read Data = 110110000000000000000000000000

# 30 Read Data = 111110000000000000000000000000

# ** Note: $finish : me.v(34)

# Time: 40 ns Iteration: 0 Instance: /tb

# End time: 18:27:02 on May 10,2016, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0和模拟:

Stack Overflow用户

发布于 2020-05-06 22:33:41

将初始化数据文件(例如"in_ram.txt")的副本粘贴到项目的..\simulation\modelsim\目录中也解决了这个问题。

https://stackoverflow.com/questions/37135859

复制相似问题