基于verilog的低功耗电路设计及不同输入序列的功率计算

基于verilog的低功耗电路设计及不同输入序列的功率计算

提问于 2016-05-04 19:27:07

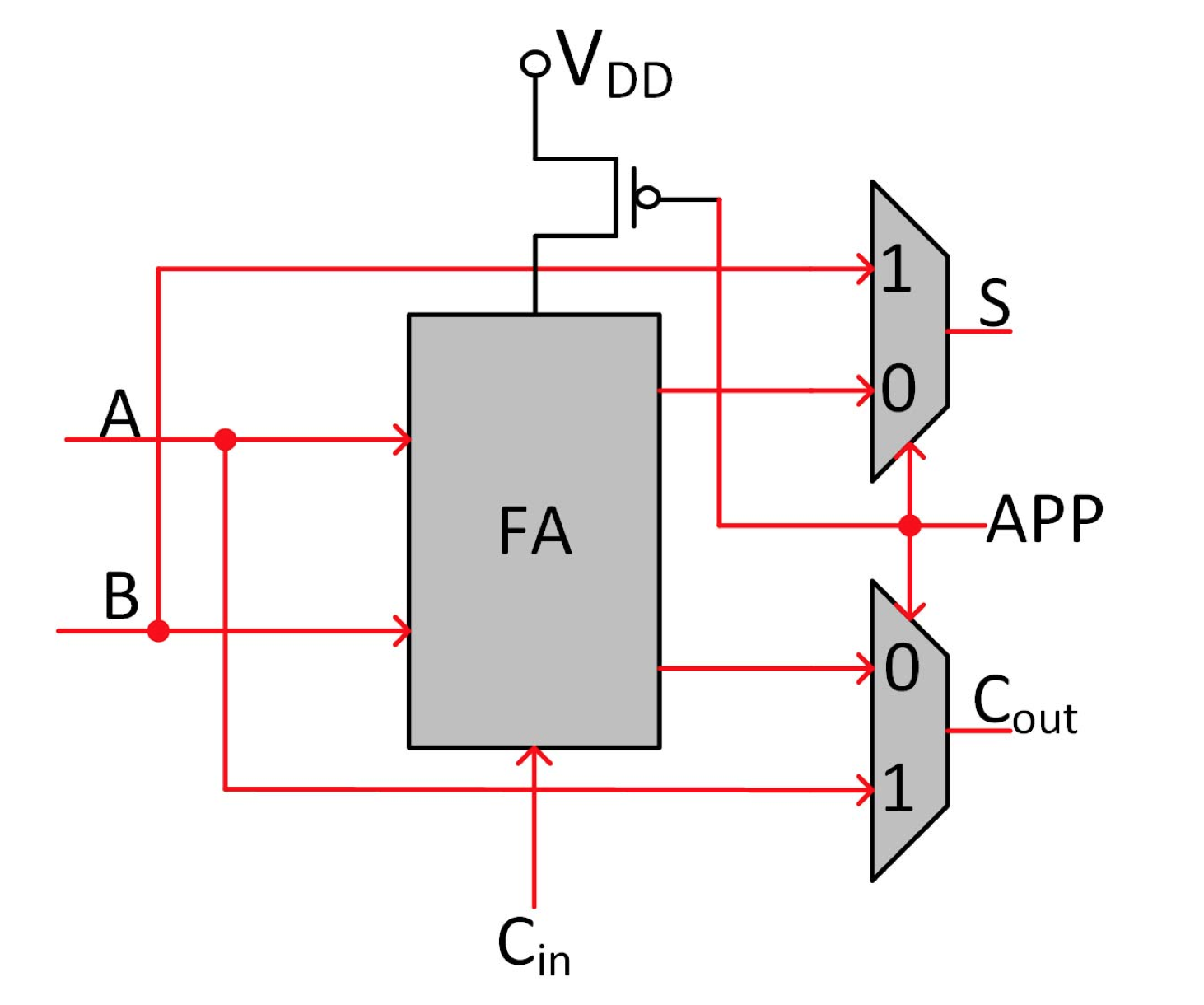

我想用verilog实现以下电路。FA为全加器电路,梯形为mux。我不知道如何在电路中添加这种功率门控pmos。另外,我还想综合一下Synopsys设计视觉中的电路,并计算当应用程序为0和1时的功率差异。

任何帮助都是徒劳无功。

谢谢

法哈纳

回答 1

Stack Overflow用户

回答已采纳

发布于 2016-05-05 13:56:34

设计两个版本的原始电路:其中一个将假设电源开关开着,FA正在工作。另一个假设电源开关关闭,然后FA将从电路中消失。留下剩下的设备(如。在这两个电路和设置应用程序。

告诉Synopsys不要执行任何优化(当select输入被固定为某个值时,它将删除but,但如果这样做,则当前的but压缩(虽然不合格)将不会被考虑在内)。

对这两个版本执行一个权力分析,你将得到不同的权力。

您得到的结果必须假设PMOS设备的泄漏电流在关闭时为0。

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/37036369

复制相关文章

相似问题