VHDL中组件实例化与实体实例化

我有使用Verilog/SystemVerilog的经验,但我对VHDL还不熟悉,我正试图弄清楚什么时候应该使用组件实例化或实体实例化。在组件实例化中,我指的是在实例化之前声明实体组件的遗留方式。另一方面,在VHDL-93中引入的实体实例化允许您直接声明一个实体,而无需指定组件。相关条款

在我看来,实体实例化总是比较可取的,除非您还没有实现体系结构,并且只想定义一个黑匣子。

这是我找到的一个相关问题,但它确实完全消除了我的疑虑。由于可以为任何实体定义通用映射和体系结构:

entity work.MyEntity_E(ARCH) generic map(

...)

port map(

...

);执行组件实例化的额外灵活性是什么?什么是最简单的示例,向展示一些不能用实体实例化完成但可以用组件实例化完成的事情

回答 3

Stack Overflow用户

发布于 2016-03-26 07:45:12

我喜欢把组件想象成一个IC插座。您可以通过将编译(分析)比作组装PCB,并将精化工作比作将芯片放在插座中,从而进一步实现这一类比。如果你使用IC插座,即使你还没有订购芯片,你也可以组装PCB;你可以把芯片放在插座里推迟到以后。同样,如果您使用组件:即使与组件相对应的实体和体系结构还不存在,也可以编译设计;您可以将绑定推迟到以后,直到精化。

那么,为什么会这样?为什么它们还不存在呢?

这是一个很大的项目。并不是每个人都已经完成了他们的街区。但是,您仍然可以轻松地编译顶级程序,并在设计的任一部分上运行模拟。您可以通过注释/编辑来实现这一点,但是使用组件可以使其变得更容易。

(2)您已经自动生成了一些IP。这给了你一个行为模型来模拟,但是没有一个可综合的模型--这个想法是,你结合了一些自动生成的物理视图,在流的后面。这对于模拟是可以的,但是如果有一点遗漏--生成的IP --那么如何编译您的设计以进行综合呢?

( iii)您正在执行递归实例化:您正在实例化内部的一个块。通过直接实例化,您得到了不可打破的鸡和蛋情况(也称为循环依赖关系);通过直接实例化,您无法实例化尚未编译的内容,但无法编译它,因为实例化实体尚未编译。组件实例化可以打破这种循环依赖。

组件实例化还使您能够在设计的同一位置(在配置的控制下)实例化不同的实体。@ using 1155120提供了上述示例:使用组件实例化(和配置)可以创建具有不同子块的相同块。

下面是一个在EDA游乐场- https://www.edaplayground.com/x/2QrS上比较这两者的例子。

Stack Overflow用户

发布于 2016-03-27 04:24:45

使用配置(这取决于组件实例化)可以完成的一件事是使用虚拟组件。

您可以编写依赖于某种理想化实体(此处命名为x)的VHDL描述,并将其映射到具有不同端口信号名称的不同组件:

entity a is

port (

in1: in bit;

in2: in bit;

out1: out bit

);

end entity;

architecture fum of a is

begin

out1 <= in1 xor in2;

end architecture;

entity b is

end entity;

architecture foo of b is

component x is

port (

a: in bit;

b: in bit;

c: out bit

);

end component;

signal a, b, c: bit;

begin

TARG:

x

port map (

a => a,

b => b,

c => c

);

STIMULI:

process

begin

wait for 2 ns;

a <= '1';

wait for 2 ns;

b <= '1';

wait for 2 ns;

a <= '0';

wait for 2 ns;

b <= '0';

wait for 2 ns;

a <= '1';

wait for 2 ns;

wait;

end process;

end architecture;

configuration fum of b is

for foo

for TARG: x use entity work.a

port map (

in1 => a,

in2 => b,

out1 => c

);

end for;

end for;

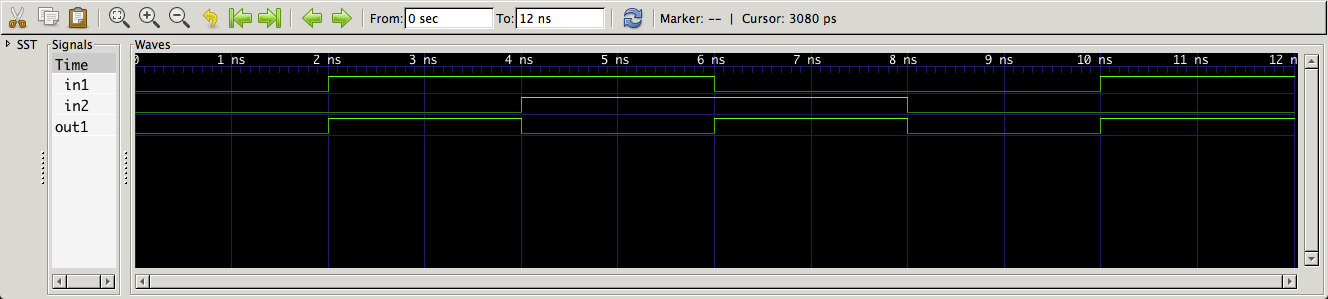

end configuration fum;详细阐述和模拟配置给出:

当看到TARG的端口信号时。

此功能用于将不同供应商库中的原语映射到标准组件声明。

配置所涉及的复杂性与可移植性库(如LPM (参数化模块库))相对应,后者通过使用属性和泛型来增加不同的复杂性轴,同时标准化接口名称和减少库原语的数量。

行为综合已经发展到了顶点,两种结构设计规范的方法都已经走下坡路。

FPGA供应商对显式配置声明的支持在历史上也一直滞后。您可以注意到,IEEE 1076.6-2004 (RTL合成,现在撤回)要求支持配置声明,而隐式配置在精化过程中提供默认绑定指示。

Stack Overflow用户

发布于 2016-03-25 23:34:27

VHDL最初是一种硬件文档语言。不是模拟也不是合成。

我同意组件实例化是痛苦的冗长,但如果实体不在同一个源文件上声明,则更容易阅读。

而且,在非常大的项目上。它允许将每个实体的编译分开。因此,更改一个实体并不意味着重新编译整个项目。

并允许很容易地与行为架构进行交互以进行模拟。Ie: DRAM就是你fpga的一堆端口。或者您可以下载dram模型并验证您的代码是否正常工作。您不需要每次模拟某样东西时返回并更改实例化。

https://stackoverflow.com/questions/36229368

复制相似问题