有反馈循环的D触发器来清除

有反馈循环的D触发器来清除

提问于 2016-01-28 10:43:50

以下是我的d触发器的代码,具有活动、低异步、清除和重置功能。Clear有一个输入,它是Q(d的输出)和复位信号的组合,我上传了一个图像来显示我编写这个程序的电路。我没有得到预期的输出;清晰和Q总是很低。我在模拟中将重置设置为逻辑一。请帮忙,让我知道我的错误:)谢谢。

LIBRARY ieee ;

USE ieee.std_logic_1164.all ;

use ieee.numeric_std.all;

ENTITY d_feedback_clr IS

PORT (

clock, reset, d: IN STD_LOGIC ;

q : OUT STD_LOGIC

) ;

END d_feedback_clr ;

ARCHITECTURE Behavior OF d_feedback_clr IS

signal state, clear: STD_LOGIC:='0'; -- state implies the output of the d register

BEGIN

clear <= reset nand state;

PROCESS (clock, clear, reset)

BEGIN

IF (clear='0') THEN

state <= '0';

elsif reset='0' then

state <= '1';

elsif (clock'event and clock='1') THEN

state <= d;

END IF ;

END PROCESS ;

q <= state;

END Behavior ;回答 1

Stack Overflow用户

回答已采纳

发布于 2016-01-29 13:13:52

我想你的问题就在清楚的信号里。如果你的状态是'1‘,重置是'1’,那么清除信号,作为这两个的nand门的输出,将变成'0‘,状态将立即改变为'0’。所以状态和Q总是很低的。

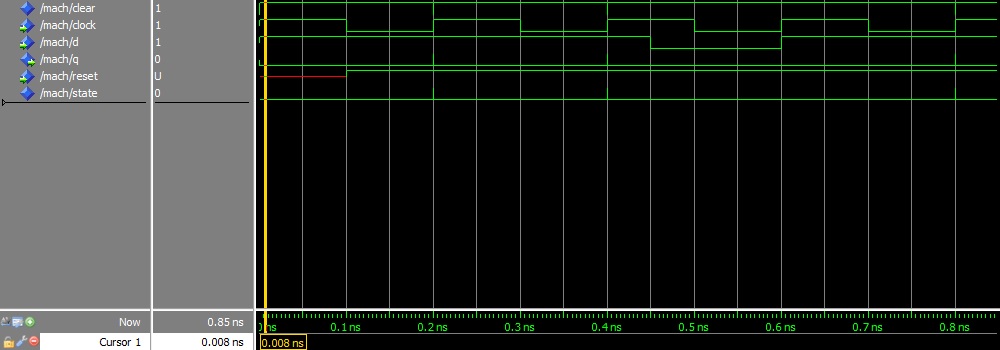

我使用Modelsim Altera来模拟您的设计,它清楚地显示了信号中的故障。

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/35059208

复制相关文章

相似问题