VHDL -合成

我有一个关于VHDL合成的问题,我希望你们中的一些人能帮助我。我有一个加法器的下列模型:

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.numeric_std.ALL;

ENTITY Q3a IS

PORT (A_MSB,B_MSB,A_LSB,B_LSB : IN std_logic_vector(3 DOWNTO 0):="0000";

SEL : IN std_logic:='0';

CARRY : OUT std_logic:='0';

OUTPUT : OUT std_logic_vector(7 DOWNTO 0):="00000000");

END ENTITY Q3a;

ARCHITECTURE behavioral OF Q3a IS

SIGNAL A,B,SUM,B_NEG : std_logic_vector(8 DOWNTO 0);

BEGIN

A <= (A_MSB(3) & '0' & A_MSB(2 DOWNTO 0) & A_LSB) WHEN A_MSB(3) = '0' ELSE

(A_MSB(3) & '1' & A_MSB(2 DOWNTO 0) & A_LSB);

B <= (B_MSB(3) & '0' & B_MSB(2 DOWNTO 0) & B_LSB) WHEN B_MSB(3) = '0' ELSE

(B_MSB(3) & '1' & B_MSB(2 DOWNTO 0) & B_LSB);

B_NEG <= std_logic_vector(signed(not(B_MSB(3) & '0' & B_MSB(2 DOWNTO 0) & B_LSB))+1);

SUM <= std_logic_vector(signed(A)+ signed(B)) WHEN SEL = '0' ELSE

std_logic_vector(signed(A)+ signed(B_NEG));

CARRY <= SUM(7);

OUTPUT <= SUM(8) & SUM(6 DOWNTO 0);

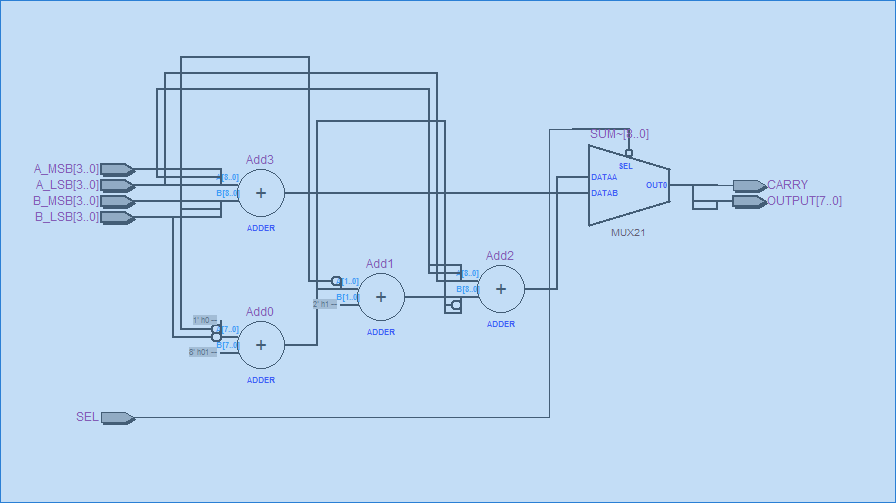

END ARCHITECTURE behavioral;这个模型工作正常,有几个小故障。当我看到它时,我看到了3个复用器,一个用于A,一个用于B,另一个用于对加法器的输入选择。当我在Quartus II上用RTL查看器打开模型时,我得到了以下信息:

在我看来就像4个加法器和一个复用器。有人能和我分享一下这件事吗?干杯D

回答 3

Stack Overflow用户

发布于 2016-01-23 08:26:00

如果我正确地理解了您,您需要一个用于a+b和a+b_neg的加法器,以及一个在b或b_neg之间选择的mux。你没有显式地写它,你需要这样写它

architecture behavioral of Q3a is

signal a,b,sum,b_neg : std_logic_vector(8 downto 0);

signal b_addr : std_logic_vector(8 downto 0);

begin

a <= (a_msb(3) & a_msb & a_lsb);

b <= (b_msb(3) & b_msb & b_lsb);

b_neg <= std_logic_vector(-signed(b));

b_addr <= b when sel = '0' else b_neg;

sum <= std_logic_vector(signed(a)+ signed(b_addr));

carry <= sum(7);

output <= sum(8) & sum(6 downto 0);

end architecture behavioral;希望能帮到你。

Stack Overflow用户

发布于 2016-01-21 00:23:35

您的设计中只有一个mux,正如Brian指出的,A的逻辑被简化为A <= A_MSB(3) & A_MSG & A_LSB,后者没有mux。

B_neg的逻辑是错误的,因为只有当B是肯定的时候,它才会给您-B。如果使用B_neg <= std_logic_vector(signed(not(B))+1);,就会得到不同的合成结果。

应该有3个加法器,一个用于B_neg,一个用于A+B,另一个用于A+B_neg。但是,我怀疑由于使用常数B_neg定义'0'的方式,合成器比您聪明,并将B_neg加法器分成两个较小的加法器。

您不必将B_neg定义为"not + 1",即两个补体的一元减去定义。使用B_neg <= std_logic_vector(-signed(B));或SUM <= std_logic_vector(signed(A)+signed(B)) when SEL = '0' else std_logic_vector(signed(A)-signed(B));的可读性更好

Stack Overflow用户

发布于 2016-01-21 11:28:01

在进行更改之后,我有以下体系结构:

ARCHITECTURE behavioral OF Q3a IS

SIGNAL A,B,SUM,B_NEG : std_logic_vector(8 DOWNTO 0);

BEGIN

A <= (A_MSB(3) & A_MSB & A_LSB);

B <= (B_MSB(3) & B_MSB & B_LSB);

B_NEG <= std_logic_vector(-signed(B));

SUM <= std_logic_vector(signed(A)+ signed(B)) WHEN SEL = '0' ELSE

std_logic_vector(signed(A)+ signed(B_NEG));

CARRY <= SUM(7);

OUTPUT <= SUM(8) & SUM(6 DOWNTO 0);

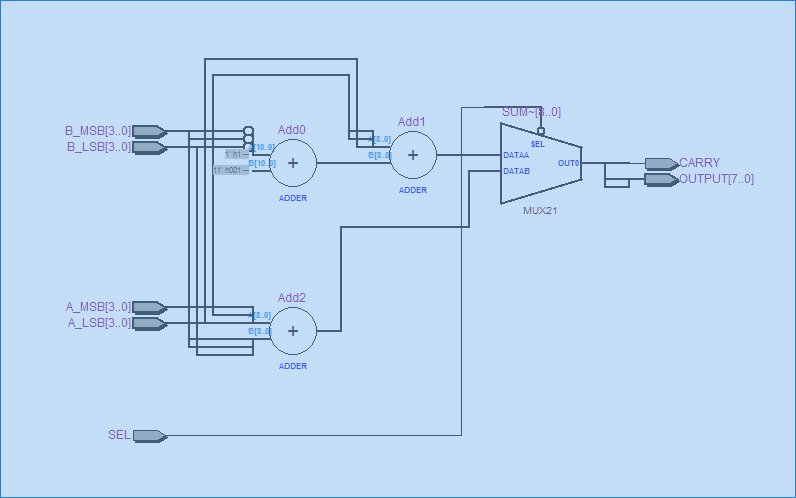

END ARCHITECTURE behavioral;RTL综合图已更改为:

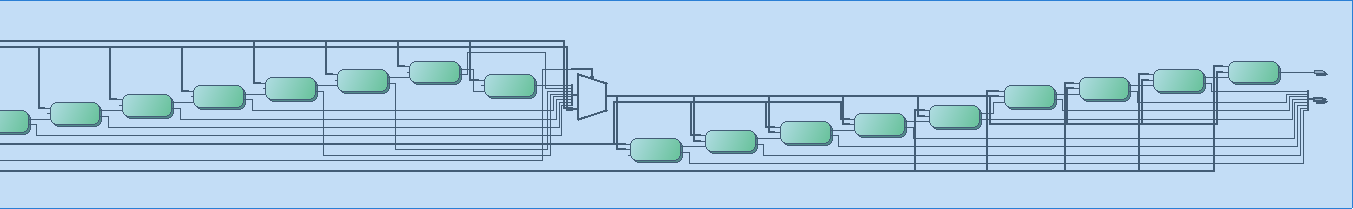

就像乔纳森建议的那样。我知道B_NEG需要一个加法器,但是,他们为什么要为A+B和A+B_NEG设置单独的加法器,然后是一个Mux,而不是有一个Mux和两个加法器呢?更像是这样的:

这只是综合选择吗?

https://stackoverflow.com/questions/34912676

复制相似问题