ModelSim和SignalTap没有显示相同的信号电平。

ModelSim和SignalTap没有显示相同的信号电平。

提问于 2016-01-07 07:08:47

我确实有以下信号:

signal sl_dac_busy : std_logic := '1';当我运行ModelSim仿真时,复位状态下的信号电平显示一个高级,而使用SignalTap的模拟显示与低电平(也处于重置状态)相同的信号。

信号水平不同的可能原因是什么?我需要为这个信号设置一个(附加的)初始值还是.?

谢谢!

回答 1

Stack Overflow用户

回答已采纳

发布于 2016-01-07 13:06:17

在与Russel讨论后,我发现,我的原件和接受回答中的一些观点是错误的。当然,Quartus-II 支持,这是一个启动后触发器的初始高值,但是,Altera上的实际映射会导致ModelSim和SignalTap之间的差异。

所有Altera (截至2016年)上的可编程触发器只能按照Quartus第一版手册第1卷:设计与综合第11节“推荐的HDL编码样式”中的规定初始化为零:

在所有Altera设备上,设备核心中的寄存器始终可以达到较低(0)的逻辑级别。

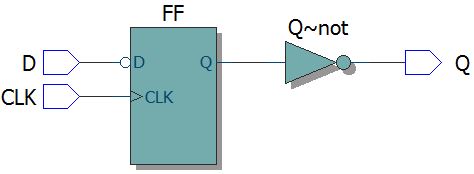

在Altera上,通过反转触发器( FF )数据输入和输出,然后将FF初始化为low,而不是11节中所描述的那样,在Altera上模拟一个高(1)逻辑级别的初始值。因此,对此FF的描述:

library ieee;

use ieee.std_logic_1164.all;

entity FF_init1 is

port (D, CLK : in std_logic;

Q : out std_logic);

end FF_init1;

architecture rtl of FF_init1 is

signal FF : std_logic := '1';

begin

FF <= D when rising_edge(CLK);

Q <= FF;

end rtl;映射如下:

不要忽略FF的D输入上的逆变器。在打开电源后,FF本身被初始化为low,但是由于Q输出后的否定,它表现为实体FF_init1的输出Q的高初始化。在运行期间,FF将被否定的输入存储在上升的时钟边缘,在输出时再次被否定。

输出端的逆变器可能被合并到后续逻辑中,这样,就不能总是在输出逆变器之后连接SignalTap。通常,您只能将SignalTap连接到FF输出本身,但是这条线路的逻辑级别与FF在ModelSim中的信号值相反。

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/34649235

复制相关文章

相似问题