带有R&S的VHDL行为D触发器

嗨,你们中有更多VHDL Quartus II经验的人,请在这个问题上给我设置一下。我有以下实体和行为架构的D触发器设置和重置.

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY Q1 IS

PORT (D,R,S,CLK : IN std_logic;

Q : OUT std_logic

);

END ENTITY Q1;

ARCHITECTURE behavioural OF Q1 IS

BEGIN

D_FF : PROCESS (CLK,R,S)

BEGIN

IF R = '0' THEN Q <= '0';

ELSIF S = '0' THEN Q <= '1';

ELSIF (rising_edge(CLK)) THEN Q <= D;

END IF;

END PROCESS D_FF;

END ARCHITECTURE behavioural;当我使用Quartus II编译代码时,会得到以下错误消息:

警告(335093):TimeQuest定时分析器正在分析一个组合回路作为锁存器。

我认为这是对R&S输入的不完全输出赋值的警告,但当我只使用SET输入制作D触发器锁存时,编译时不会出现此错误消息。这让我想,也许我在写架构时犯了一个错误?如果任何人有任何答案或有用的信息,将是非常感谢。

回答 3

Stack Overflow用户

发布于 2016-01-05 16:01:26

您已经描述了具有异步复位和异步设置的时钟边缘触发触发器(FF)。因为AFAIK,Altera上的所有FF都只有异步复位,所以同时只支持其中一个。

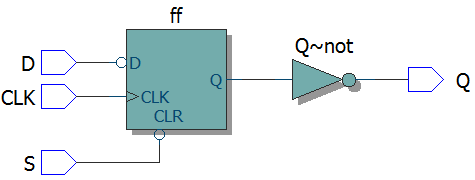

在Altera上,通过反转FF数据的输入和输出来模拟异步集,然后将其重置为低,而不是设置为高。看起来是这样的:

不要忽略FF的D输入上的逆变器。如果S是低的,那么FF 本身的是异步重置的,但是由于Q输出后的否定,它表现为实体Q1的一组异步输出Q。如果S很高,FF会在上升的时钟边缘存储被否定的输入,而在输出时又会被否定。如您所见,已经使用了FF的异步重置端口,因此不能用于对实体Q1进行额外的异步重置。

我建议使用具有同步设置和重置的触发器:

ARCHITECTURE sync_rs OF Q1 IS

BEGIN

D_FF : PROCESS (CLK)

BEGIN

IF (rising_edge(CLK)) THEN

IF R = '0' THEN Q <= '0';

ELSIF S = '0' THEN Q <= '1';

ELSE Q <= D;

END IF;

END IF;

END PROCESS D_FF;

END ARCHITECTURE sync_rs;Stack Overflow用户

发布于 2016-01-05 16:18:54

FPGA设备中的触发器通常有异步设置或复位,但两者都没有,因此Altera试图用锁存器而不是专用硬件来制作请求的电路。

然而,在大多数情况下,这不是您想要的,所以使用触发器或者异步复位或者设置,或者使用同步设置和重置,就像Martin在他的回答中建议的那样。

注意,在高速设计中,异步复位比同步复位具有优势,因为异步复位不会在主同步数据路径中添加任何登录名,而主同步数据路径通常是高速设计的关键路径。

最后,对于异步重置,使用两个if单独语句(最后重置)是一个好习惯,因此时钟不依赖于复位的断言。这不是单个位翻转触发器的问题,但是如果在同一过程中控制了更多的信号,并且重置并不适用于所有信号,那么对于那些没有重置的信号,时钟不应该依赖于复位,因为这将推断锁存。代码如下:

D_FF : PROCESS (CLK, R)

BEGIN

IF rising_edge(CLK) THEN

Q <= D;

END IF;

IF R = '0' THEN

Q <= '0';

END IF;

END PROCESS D_FF;Stack Overflow用户

发布于 2016-01-05 16:45:58

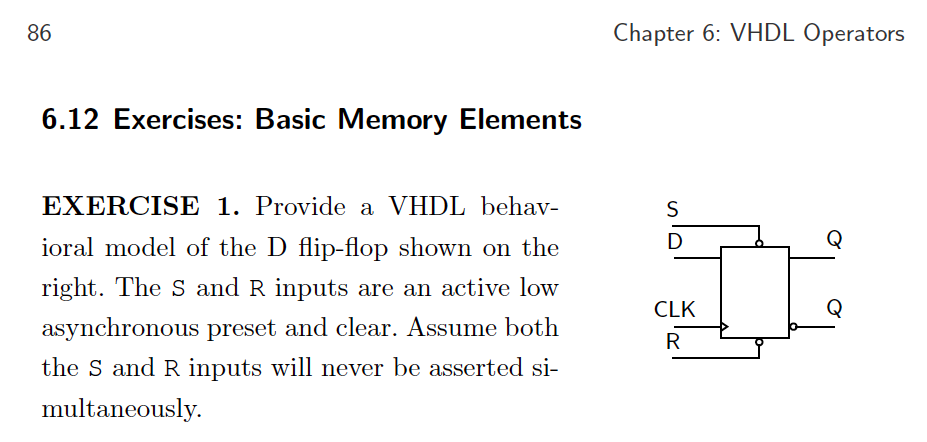

谢谢你的回复,我故意让R&S输入是异步的。我一直在阅读VHDL教材“自由范围VHDL”,并在练习中遇到了以下问题:

这个问题要求两个输入都是异步的。你说这可以通过倒置输入和输出来模仿Altera,并将其重置为低而不是高。你能再谈一谈吗?谢谢

https://stackoverflow.com/questions/34615664

复制相似问题