使用Yosys的FSM出口

使用Yosys的FSM出口

提问于 2015-09-18 07:13:13

我正在尝试这个叫做约西斯的非常整洁的工具来合成我的Verilog设计。我想导出FSM在我的Verilog设计使用Yosys命令fsm_export,但它不产生任何东西。我想知道这个命令应该怎么叫?

我调用的一系列命令是:read_verilog qwerty.v ; fsm_export

如果这代人是成功的,而且我有KISS2格式的FSM,那么有人知道有什么(开源)工具可以让我可视化FSM吗?

谢谢一堆人!

回答 1

Stack Overflow用户

回答已采纳

发布于 2015-09-18 09:10:30

fsm_export命令对提取的FSM(即$fsm单元)进行操作。为了创建设计包含此类FSM单元的状态,首先需要检测FSM (fsm_dectect),然后提取它们(fsm_extract)。有关FSM流的更多信息,请参见help fsm。

达到这种状态的最简单方法是简单地运行fsm -nomap。示例脚本:

read_verilog test.v

proc; opt; fsm -nomap

fsm_export -o test.kiss2例如,考虑下面的test.v文件。

module test(input clk, rst, ctrl, output [3:0] O);

reg [1:0] state;

always @(posedge clk) begin

O <= 0;

if (rst) begin

state <= 0;

end else case (state)

0: begin

state <= ctrl ? 1 : 2;

O <= 1;

end

1: begin

O <= 2;

if (ctrl) begin

state <= 2;

O <= 3;

end

end

2: begin

O <= 4;

if (ctrl) begin

state <= 3;

O <= 5;

end

end

3: begin

if (!ctrl)

state <= 2'b00;

end

endcase

end

endmodule上面的脚本将生成以下test.kiss2文件。(我有检出,所以使用当前的git头。)

.i 2

.o 3

.p 12

.s 4

.r s0

-1 s0 s0 100

00 s0 s1 100

10 s0 s2 100

-1 s1 s0 001

00 s1 s1 001

10 s1 s3 001

-1 s2 s0 010

10 s2 s1 010

00 s2 s2 010

00 s3 s0 000

-1 s3 s0 000

10 s3 s3 000注意:在这种情况下,FSM的输出不是直接的四个O信号位。相反,Yosys创建了一个具有三位输出的FSM和一个FSM外部的编码器,用于创建四个O信号位。

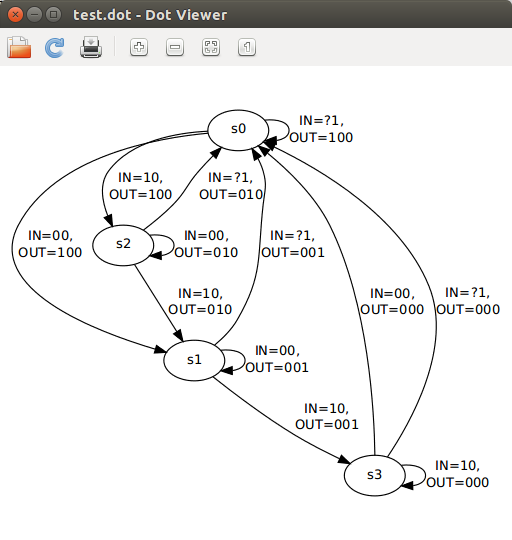

关于可视化:不幸的是,我不知道有任何图形用户界面工具来显示KISS2文件(这并不意味着不存在这样的工具)。但是从一个GraphViz文件创建一个.dot文件非常容易,例如使用下面的python脚本(kiss2dot.py)。

#!/usr/bin/env python3

import fileinput

print("digraph fsm {")

for line in fileinput.input():

if not line.startswith("."):

in_bits, from_state, to_state, out_bits = line.split()

print("%s -> %s [label=\"IN=%s,\\nOUT=%s\"];" % (from_state, to_state,

in_bits.replace("-", "?"), out_bits.replace("-", "?")))

print("}")示例用法:

python3 kiss2dot.py test.kiss2 > test.dot

xdot test.dot这将显示以下图形:

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/32645965

复制相关文章

相似问题