xilinx ise PRO

我们正在设计一个8位加法器在verilog。代码是

module addsub (

input [7:0] dataa,

input [7:0] datab,

input clk,

output reg[8:0] result

);

always@(posedge clk)

begin

result <= dataa + datab;

end

endmodule你能给我们简单的步骤来生成核心,以便我们使用CHIPSCOPE PRO在Spartan3e板上运行这段代码。我们试图使用各种论坛和视频,但没有找到确切的步骤。

编辑1-警告列表:

这里有警告消息,但没有错误消息。

有关警告如下:

WARNING:Xst:2211 - "ipcore_dir/aj_icon_core.v" line 16: Instantiating black box module <aj_icon_core>.

WARNING:Xst:2211 - "ipcore_dir/aj_vio_core.v" line 25: Instantiating black box module <aj_vio_core>.

WARNING:Xst:2211 - "ipcore_dir/aj_ila_core.v" line 36: Instantiating black box module <aj_ila_core>.

WARNING:Xst:1780 - Signal <CONTROL> is never used or assigned. This unconnected signal will be trimmed during the optimization process.

WARNING:Xst:1780 - Signal <CLK> is never used or assigned. This unconnected signal will be trimmed during the optimization process.

WARNING:PhysDesignRules:372 - Gated clock. Clock net CONTROL1<13> is sourced by a combinatorial pin. This is not good design practice. Use the CE pin to control the loading of data into the flip-flop.

WARNING:Route:455 - CLK Net:CONTROL1<13> may have excessive skew because

WARNING:Route:455 - CLK Net:result_3 may have excessive skew because

WARNING:Route:455 - CLK Net:result_6 may have excessive skew because

WARNING:Route:455 - CLK Net:result_4 may have excessive skew because

WARNING:Route:455 - CLK Net:result_7 may have excessive skew because

WARNING:Route:455 - CLK Net:result_8 may have excessive skew because

WARNING:Route:455 - CLK Net:result_1 may have excessive skew because

WARNING:Route:455 - CLK Net:result_0 may have excessive skew because

WARNING:Route:455 - CLK Net:result_5 may have excessive skew because

WARNING:Route:455 - CLK Net:result_2 may have excessive skew because

WARNING:PhysDesignRules:372 - Gated clock. Clock net CONTROL1<13> is sourced by a combinatorial pin. This is not good design practic我们的代码如下:

`timescale 1ns / 1ps

module addsub (

inout [7:0] dataa,

inout [7:0] datab,

input clk1,

output reg[8:0]result

);

/////////////////ICON////////////////////////////

wire[35:0] CONTROL0;

wire[35:0] CONTROL1;

aj_icon_core YourInstanceName (

.CONTROL0(CONTROL0), // INOUT BUS [35:0]

.CONTROL1(CONTROL1) // INOUT BUS [35:0]

);

//////////////////////VIO//////////////////////////////////////

wire[35:0] CONTROL;

wire CLK;

wire [8:0] SYNC_IN;

wire [15:0] SYNC_OUT;

aj_vio_core vio_core1 (

.CONTROL(CONTROL0), // INOUT BUS [35:0]

.CLK(clk1), // IN

.SYNC_IN(SYNC_IN), // IN BUS [8:0]

.SYNC_OUT(SYNC_OUT) // OUT BUS [15:0]

);

//////////////////////////////////ila///////////////////////

wire [31 : 0] TRIG0;

aj_ila_core ila_core1(

.CONTROL(CONTROL1), // INOUT BUS [35:0]

.CLK(clk1), // IN

.TRIG0(TRIG0) // IN BUS [31:0]

);

assign TRIG0={16'h0000, dataa ,datab}; //

assign dataa= SYNC_OUT[15:8], datab= SYNC_OUT[7:0], SYNC_IN=result;

always@(posedge clk1)

begin

result <= dataa + datab;

end

endmodule回答 1

Stack Overflow用户

发布于 2015-03-12 15:31:12

在项目中创建一个新的源代码(文件):ChipScope定义和连接文件(*.cdc),并遵循向导的说明。

阅读UG750一步一步的指南。

Edit1 -示例:

对不起,目前我只能提供一个VHDL示例。

entity myExample is

port (

A : out : STD_LOGIC_VECTOR(31 downto 0);

B : out : STD_LOGIC_VECTOR(31 downto 0);

C : in : STD_LOGIC_VECTOR(31 downto 0)

);

end entity;

architecture rtl of myExample is

subtype T_XIL_CHIPSCOPE_CONTROL is STD_LOGIC_VECTOR(35 downto 0);

type T_XIL_CHIPSCOPE_CONTROL_VECTOR is array (NATURAL range <>) of T_XIL_CHIPSCOPE_CONTROL;

signal ControlBus : T_XIL_CHIPSCOPE_CONTROL_VECTOR(0 downto 0);

signal ControlVIO_In : STD_LOGIC_VECTOR(31 downto 0);

signal ControlVIO_Out : STD_LOGIC_VECTOR(63 downto 0);

begin

-- instantiate a ICON IPCore with one ports

ICON : entity PoC.xil_ChipScopeICON_1

port map (

control0 => ControlBus(0)

);

ControlVIO : entity myDesign.CSP_ControlVIO

port map (

CONTROL => ControlBus(0),

CLK => SoFPGA_Clock,

SYNC_IN => ControlVIO_In,

SYNC_OUT => ControlVIO_Out

);

A <= ControlVIO_Out(31 downto 0);

B <= ControlVIO_Out(63 downto 32);

ControlVIO_In <= C;

end;此示例使用带有一个控制端口的图标IPCore。所有信号都聚合成一个T_XIL_CHIPSCOPE_CONTROL类型。(见xil.pkg.vhdl)。

预配置的图标核心可以从这里下载。每个可能的端口计数有15个图标核。除此之外,还有一个通用图标包装器ChipScopeICON.vhdl来隐藏所有核心,并通过泛型选择适当的核心。

ControlVIO的同步端口连接到你的加法器可以使用的32位中的A,B,C。

编辑2-包括netlists:

关于如何包含netlists,有三种方法:

1)

将生成的xco文件添加到项目中。它包含了一切。

2)

将生成的ngc文件添加到项目中。那是网络名单。关联的netlist约束文件(ncf)将自动加载。

3) (这适用于VHDL,而不是用Verilog测试)

将生成的包装器vhdl文件添加到项目中,并将其分配给库。现在指定一个或多个IPCore读目录:

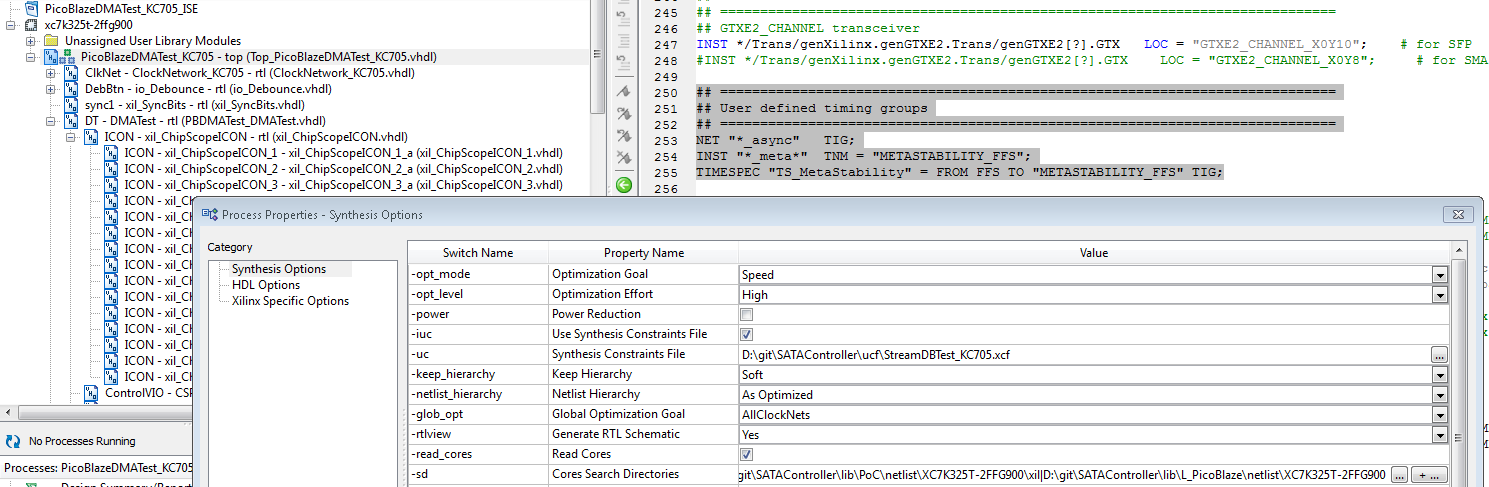

XST process properties -> Synthesis options page:

-read_cores - Read Cores

-sd - Cores Search Directories = d:\git\....\IPCores

(可点击)

这张图片显示了背景中1..15端口的ChipScope图标包装。15个VHDL文件作为占位符加载。在Forground中,您可以看到XST属性和配置的搜索路径。使用“\”分隔多个目录。

如果启用了读核,XST应该报告XST报告(syr文件)中找到的netlists。

https://stackoverflow.com/questions/29013072

复制相似问题