将50 VHDL转换为38 VHDL的VHDL代码不起作用

将50 VHDL转换为38 VHDL的VHDL代码不起作用

提问于 2014-11-18 17:28:47

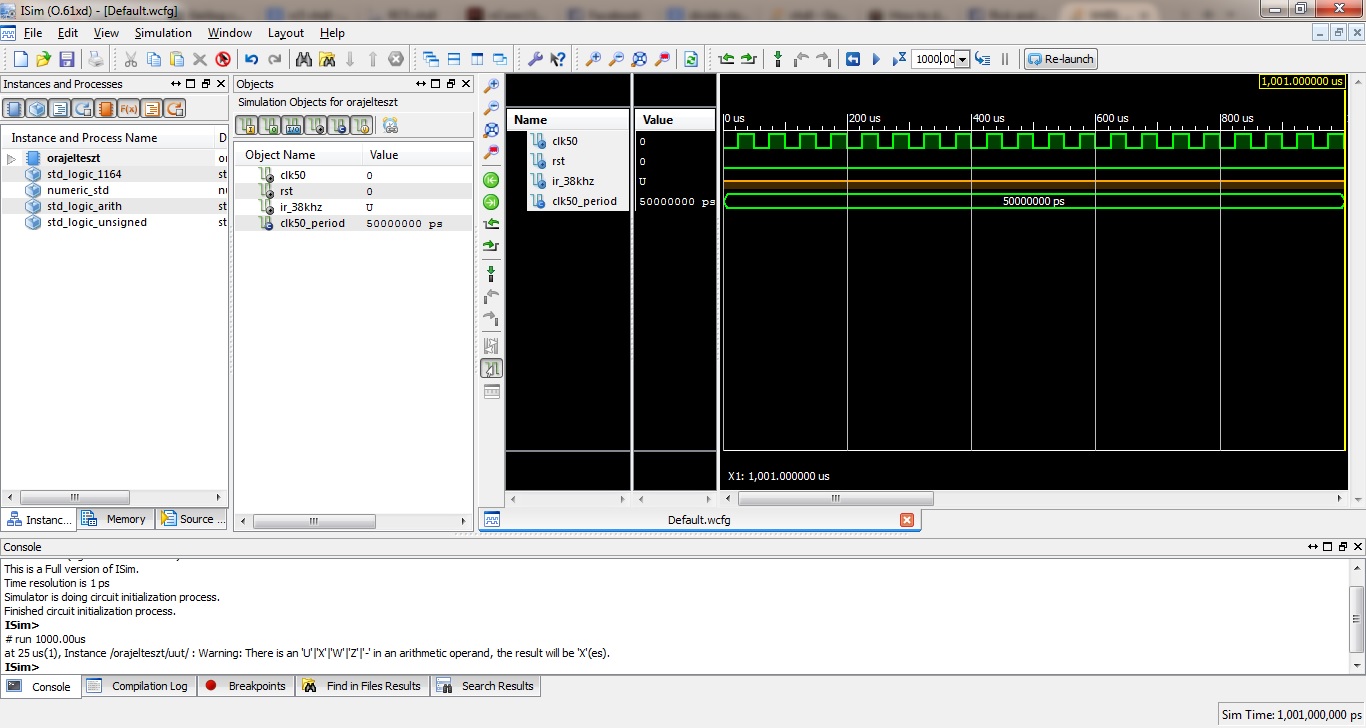

我对这段代码有意见。理论上,它应该将我的50兆赫信号转换为36 the,但是当我运行模拟时,结果是ir_38khz没有得到任何未分配的值。

你能帮我滑到哪里吗?

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

use IEEE.NUMERIC_STD.all;

entity orajelKonverter is

Port ( clk50 : in STD_LOGIC;

rst : in STD_LOGIC;

ir_38khz : out STD_LOGIC);

end orajelKonverter;

architecture Behavioral of orajelKonverter is

signal hz38_ctr : STD_LOGIC_VECTOR(9 downto 0);

signal s38 : std_logic;

begin

clk_generator : process (clk50, rst)

begin

if rst = '1' then

s38 <= '0';

hz38_ctr <= (others => '0');

elsif clk50='1' then

if hz38_ctr = "1010010010" then

hz38_ctr <= (others => '0');

s38 <= not s38;

else

hz38_ctr <= hz38_ctr + "1";

end if;

end if;

end process clk_generator;

ir_38khz <= s38;

end Behavioral;下面是模拟的图片:

回答 1

Stack Overflow用户

回答已采纳

发布于 2014-11-18 17:42:56

您需要将您的信号初始化为某个值,或者断言您的重置以在模拟中初始化它们。我个人更喜欢#1,因为信号初始条件是可综合的,尽管人们普遍认为它们不是。事实上,我避免在我的设计中重置,除非我绝对需要使用它们。这实际上是Xilinx推荐。例如,您可以这样做:

signal s38 : std_logic := '0';这将保证当您的模拟开始时,它知道如何处理该行:

s38 <= not s38;在此之前,模拟器试图进行not U,即U。

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/27000334

复制相关文章

相似问题