信号ModelSim中奇怪的尖峰

信号ModelSim中奇怪的尖峰

提问于 2014-07-14 13:02:01

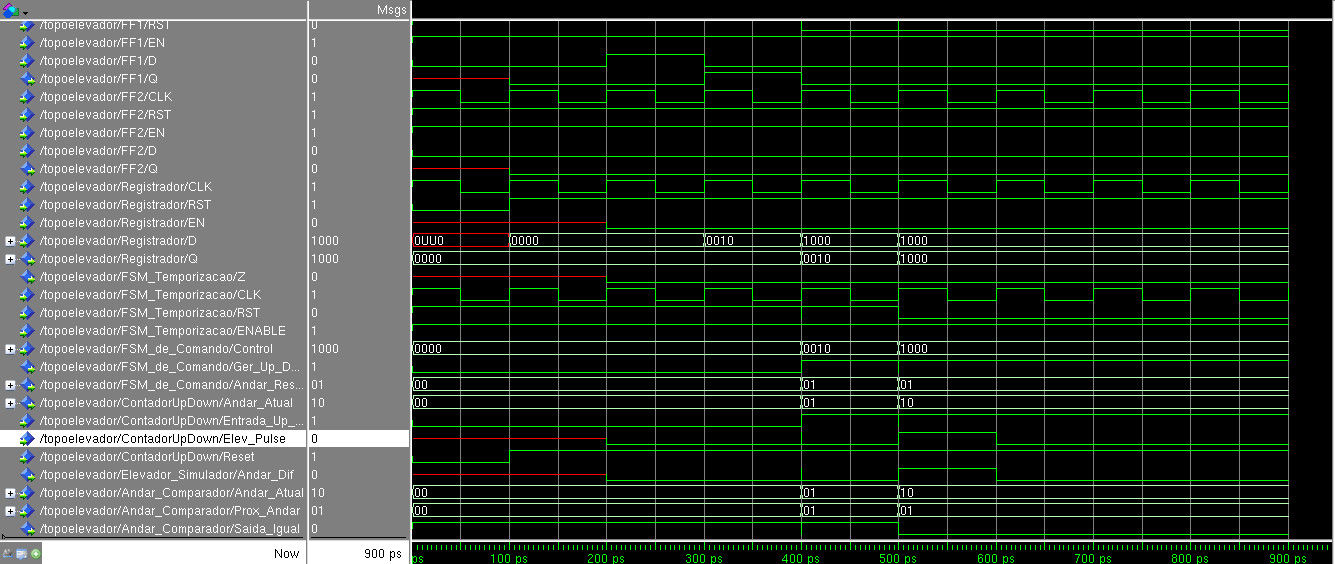

我正在为学校做最后一个项目,这是我第一次在Quartus和ModelSIM中使用VHDL。它应该是三层电梯的控制点。我有这些奇怪的尖峰在几个信号,我似乎找不到他们的来源。

我遇到的一个问题是一个信号的尖峰,它提供给一个显示当前地板的上下计数器。当它停在一层楼的时候,它会多数一次,或者一层太高,或者一层太低,而下一层的显示器似乎显示同一层,直到另一层被调用。下一层显示来自FSM,而当前地板显示来自上/下计数器。

这是有点复杂的张贴在这里,所以我现在只张贴波形,以防有人遇到信号尖峰的事情,这是一个小的错误/简单的修复。

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity FSM_Elevador is

port (Up_Down, Igual, Reset, Clock: in std_logic;

Andar_Dif: out std_logic

);

end FSM_Elevador;

architecture FSM_beh of FSM_Elevador is

type Elev_States is (Start, Wait_State, Pulse_State);

signal Current_State, Next_State: Elev_States;

signal RST, CLK, Sig_Andar_Dif, Cont_Mesmo_Andar: std_logic;

begin

RST <= Reset;

CLK <= Clock;

process(RST, CLK)

begin

if RST = '0' then

Current_State <= Start;

elsif CLK'event and CLK = '1' then

Current_State <= Next_State;

end if;

end process;

process(Current_State, Igual)

begin

case Current_State is

when Start =>

Next_State <= Wait_State;

when Wait_State =>

if Igual = '1' then

Next_State <= Wait_State;

Sig_Andar_Dif <= '0';

else

Next_State <= Pulse_State;

Sig_Andar_Dif <= '1';

end if;

when Pulse_State =>

if Igual = '1' then

Sig_Andar_Dif <= '0';

Next_State <= Wait_State;

else

Sig_Andar_Dif <= '0';

Next_State <= Pulse_State;

end if;

end case;

end process;

Andar_Dif <= Sig_Andar_Dif;

end FSM_beh;fru1tbat:这是教授建议的。

编辑:很抱歉,之前的代码错了。Andar_Dif是将信号发送到具有Elev_Pulse的组件的信号。

回答 1

Stack Overflow用户

回答已采纳

发布于 2014-07-14 15:47:35

摆脱时钟的重新分配和重置到CLK和RST,直接使用来自端口的信号。这就产生了一个δ周期延迟,这就是这种尖峰的原因。看起来你在设计中有不同的延迟重置,这也会使事情复杂化。如果移除间接方向并不能使事情清晰起来,那么您需要仔细检查事件何时在信号上生成以及何时被处理。

来自状态机的输出未注册,这也可能涉及到。考虑对FSM进行重新加工,以便所有输出都已注册。一般来说,这是一个更好的设计实践,因为它确保您不会有影响下游逻辑的未知组合延迟。

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/24737148

复制相关文章

相似问题