防止编译器对逻辑进行优化

我想要产生一个reset信号(活动高),将持续很短的时间。我是通过以下代码实现的:

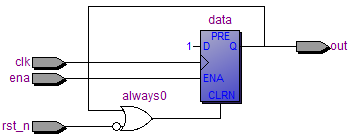

always @(posedge clk or negedge rst_n or posedge data) begin

if(~rst_n | data)

data <= 1'b0;

else if(ena)

data <= 1'b1;

else

data <= data;

end 它被合成为D flip-flop:

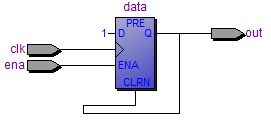

我所产生的信号只有当时间等于通过1门的传播时间时才是OR。现在我要删除rst_n信号。但是,如果我这样做,我会收到以下D flip-flop:

那样的话,我的信号就不会很高了。我想出的最简单的解决方法是在Q和CLR之间添加两个CLR门。不幸的是,我的软件(Quartus II)将合成这两个大门之外。

如何去除rst_n,以便正确产生reset信号?

回答 2

Stack Overflow用户

发布于 2014-07-14 04:56:21

你试过使用Quartus的“合成保持”标签来插入缓冲区吗?

keep.htm

试试这个:

module test(clk,ena,data);

input clk, ena;

wire data_n /*synthesis keep*/;

wire data_nn /*synthesis keep*/;

output reg data;

assign data_n = ~data;

assign data_nn = ~data_n;

always @(posedge clk or posedge data_nn) begin

if(data_nn)

data <= 1'b0;

else if(ena)

data <= 1'b1;

else

data <= data;

end

endmoduleStack Overflow用户

发布于 2014-07-12 19:53:18

你能让D触发器同步复位,而不是异步复位吗?

如果您将输出反馈到异步复位,您将得到一个非常不稳定的短脉冲,这可能甚至可能无法完全通过设计。在这种情况下,您可能实际上只是重置一半的失败在您的设计,您可能会得到不同的行为,每次你的权力在设备上。

如果你想要驱动重置直到第一个边缘,然后将触发器初始化为1,并将0放在D引脚上。然后你的失败将驱动1,直到第一个时钟周期。这很可能是不稳定的,这取决于时钟什么时候开始运行,而设备什么时候才能完全启动。

理想情况下,您需要一个更长的复位脉冲,让设备有更多的时间使用powerup,并通过设计稳定地传递复位信息,并确保在复位释放之前,任何其他同步复位触发器都被初始化。在这种情况下,您可以将几个位的计数器初始化为某个值,并让它开始在电源上进行计数,然后在计数器达到0时取消重置。

而且,这只适用于FPGA设计,您可以在这里设置触发器的初始值。如果您正在讨论硅设计,那么肯定需要外部复位信号。

https://stackoverflow.com/questions/24712976

复制相似问题