ShiftRegister Verilog输出提供xxxxxxx

ShiftRegister Verilog输出提供xxxxxxx

提问于 2020-04-24 16:15:56

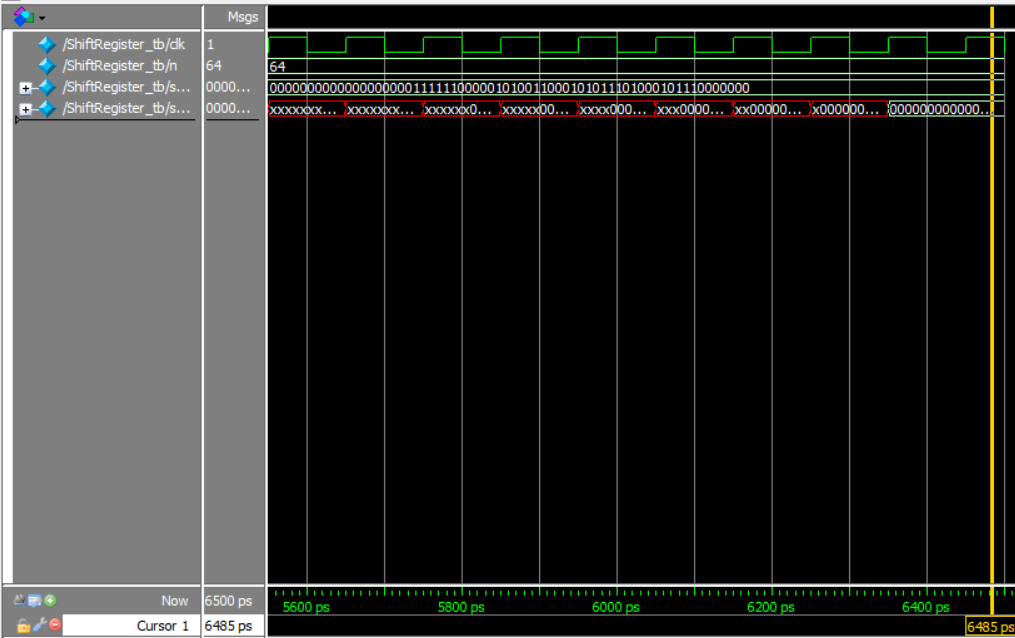

我在用Verilog做64位移位寄存器。当我尝试testbench中的代码时,我只得到xxxxxx作为输出,直到所有的位都被移开。我不知道问题出在哪里。下面是我带testbench的代码和结果:

module ShiftRegister (shift_out, clk, shift_in); //module ports

parameter n = 64; //Parameter n declared to store 64

input [n-1:0] shift_in; //64-bit input shift_in

input clk; //Input clock

output [n-1:0] shift_out; //64-bit output shift_out

reg [n-1:0] ff; //64-bit flipflop

assign shift_out = ff [n-1:0]; //give the output of the 64th bit

//The operation of verilog:

always @ (posedge clk) //Always at the rising edge of the clock

begin

ff <= ff << 1; //Shift bits to the left by 1

ff[0] <= shift_in; //Take the input bits and give it to the first flipflop

end

endmodule //ShiftRegister module

///Testbench\\\

module ShiftRegister_tb; //Module shiftRegister_tb

parameter n = 64; //Parameter n declared to store 64

reg [n-1:0] shift_in; //64-bit register input shift_in

reg clk, rst; //register clock

wire [n-1:0] shift_out; //64-bit wire output shift_out

ShiftRegister DUT(shift_out, clk, shift_in); //Calling the module

initial

begin

clk = 0; //clock = 0 initally

shift_in = 64'd34645767785344; //Random decimal number to test the code

#100;

end

always #50 clk =~clk; //invert the clock input after 50ps

endmodule //ShiftRegister testbench

回答 1

Stack Overflow用户

回答已采纳

发布于 2020-04-24 16:30:29

您可以将ff声明为reg,reg的默认值是x。在时钟的第一个前缘之前,所有64位ff都是x (未知)。在时钟的第一个前缘之后,ff[0]变成0,因为shift_in[0]是0。以此类推,直到达到64个时钟,那么所有的ff位都是0。shift_out就跟在ff后面。

通常,您的设计也会有一个重置信号。如果有,则可以在开始时断言重置,并在重置期间将ff分配给0。以下是重置后的样子:

module ShiftRegister (shift_out, clk, shift_in, rst); //module ports

parameter n = 64; //Parameter n declared to store 64

input rst;

input [n-1:0] shift_in; //64-bit input shift_in

input clk; //Input clock

output [n-1:0] shift_out; //64-bit output shift_out

reg [n-1:0] ff; //64-bit flipflop

assign shift_out = ff [n-1:0]; //give the output of the 64th bit

always @ (posedge clk or posedge rst) //Always at the rising edge of the clock

begin

if (rst) begin

ff <= 0;

end else begin

ff <= ff << 1; //Shift bits to the left by 1

ff[0] <= shift_in; //Take the input bits and give it to the first flipflop

end

end

endmodule

module ShiftRegister_tb; //Module shiftRegister_tb

parameter n = 64; //Parameter n declared to store 64

reg [n-1:0] shift_in; //64-bit register input shift_in

reg clk, rst; //register clock

wire [n-1:0] shift_out; //64-bit wire output shift_out

ShiftRegister DUT(shift_out, clk, shift_in,rst); //Calling the module

initial

begin

clk = 0; //clock = 0 initally

rst = 1;

shift_in = 64'd34645767785344; //Random decimal number to test the code

#100;

rst = 0;

#50_000 $finish;

end

always #50 clk =~clk; //invert the clock input after 50ps

endmodule页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/61412781

复制相关文章

相似问题