verilog中的操作数

verilog中的操作数

提问于 2021-01-31 05:32:37

我正在尝试使用Verilog实现PID控制器,但是在编码过程中我遇到了一些问题。

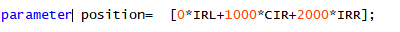

我试图将这个位置设置为parameter,就像屏幕截图中显示的那样:

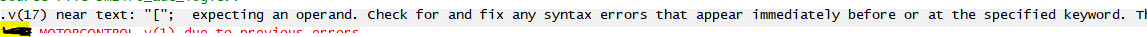

但是,我遇到了一个我不知道的错误:

错误1:-

Error (10170): Verilog HDL syntax error at Verilog1.v(16) near text: "["; expecting an operand. Check for and fix any syntax errors that appear immediately before or at the specified keyword. The Intel FPGA Knowledge Database contains many articles with specific details on how to resolve this error. Visit the Knowledge Database at https://www.altera.com/support/support-resources/knowledge-base/search.html and search for this specific error message number.错误2:-

Error (10170): Verilog HDL syntax error at Verilog1.v(34) near text: "["; expecting "@", or an operand. Check for and fix any syntax errors that appear immediately before or at the specified keyword. The Intel FPGA Knowledge Database contains many articles with specific details on how to resolve this error. Visit the Knowledge Database at https://www.altera.com/support/support-resources/knowledge-base/search.html and search for this specific error message number.我也尝试过类似的integer position= [0*IRL+1000*CIR+2000*IRR];,但我仍然面临着同样的问题。如何修复此语法错误?

回答 2

Stack Overflow用户

回答已采纳

发布于 2021-01-31 18:57:43

编译后,只能读取参数值,不能修改参数值。它们是运行时常量。integer类型只能在过程块中分配。您可以在声明时给它一个初始值,但它不会自动更新。因此,您需要一个过程赋值或具有连续赋值的净类型。

方括号([])用于索引向量的数组或切片。它们不能像圆括号(())或花括号({})一样使用。在你的情况下,不需要。

更改:

integer position= [0*IRL+1000*CIR+2000*IRR];至:

wire [31:0] position= 0*IRL+1000*CIR+2000*IRR;或者:

wire [31:0] position;

assign position= 0*IRL+1000*CIR+2000*IRR;或者:

integer position;

always @* begin

position= 0*IRL+1000*CIR+2000*IRR;

end也改变:

Proportional<= [position/IRL+CIR+IRR]-1000;至:

Proportional<= (position/IRL+CIR+IRR)-1000;Stack Overflow用户

发布于 2021-01-31 11:43:51

假设IRL、CIR和IRR声明为常量类型(如parameter),则应去掉方括号:

parameter position = 0*IRL+1000*CIR+2000*IRR;页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/65976067

复制相关文章

相似问题