gtkwave中的奇异试验台行为

gtkwave中的奇异试验台行为

提问于 2021-02-09 15:06:03

我试图在SystemVerilog中设计一个电梯控制器。代码编译得很好,但是当我将代码放在gtkwave中时,testbench完全不同。控制器接收3种不同的输入(3层中每层一层,就像适当电梯的按钮),并将其输出传递给电梯引擎,后者可以停留在同一层,上下两层。

这是模块的代码:

enum logic [4:0] {fermo, sale, sale2, scende, scende2} motore;

module ascx (input logic x0, x1, x2, clk, reset,

output logic [4:0] y);

enum logic [1:0] {pianoterra, primopiano, secondopiano} piani;

logic [1:0] pianoatt, pianoprox;

always_ff@(posedge clk, posedge reset)

if(reset) pianoatt <= pianoterra;

else pianoatt <= pianoprox;

always_comb begin

if(x1) pianoprox = primopiano;

else if(x0) pianoprox = pianoterra;

else if(x2) pianoprox = secondopiano;

end

always @(*) begin

case(pianoatt)

pianoterra: begin

if(x0) assign y = fermo; /*assign y = 5'b00001;*/

if(x1) assign y = sale; /*assign y = 5'b00010;*/

if(x2) assign y = sale2; /*assign y = 5'b00100;*/

end

primopiano: begin

if(x0) assign y = scende; /*assign y = 5'b01000;*/

if(x1) assign y = fermo; /*assign y = 5'b00001;*/

if(x2) assign y = sale; /*assign y = 5'b00010;*/

end

secondopiano: begin

if(x0) assign y = scende2; /*assign y = 5'b10000;*/

if(x1) assign y = scende; /*assign y = 5'b01000;*/

if(x2) assign y = fermo; /*assign y = 5'b00001;*/

end

default assign y = fermo;

endcase

end

endmodule 这里是测试台:

module tst_ascx();

logic clk, reset, x0, x1, x2;

logic [4:0] y;

ascx dut(clk, reset, x0, x1, x2, y);

always begin

clk=0; #10;

clk=1; #10;

end

initial begin

$dumpfile("ascx.vcd");

$dumpvars;

reset=1; x0=0; x1=0; x2=0; #10;

reset=0; x0=1; x1=0; x2=0; #10;

x0=0; x1=1; #10;

x1=0; x2=1; #10;

x0=1; x2=0; #10;

x0=0; x2=1; #10;

x1=1; x2=0; #10;

x0=1; x0=0; #10;

end

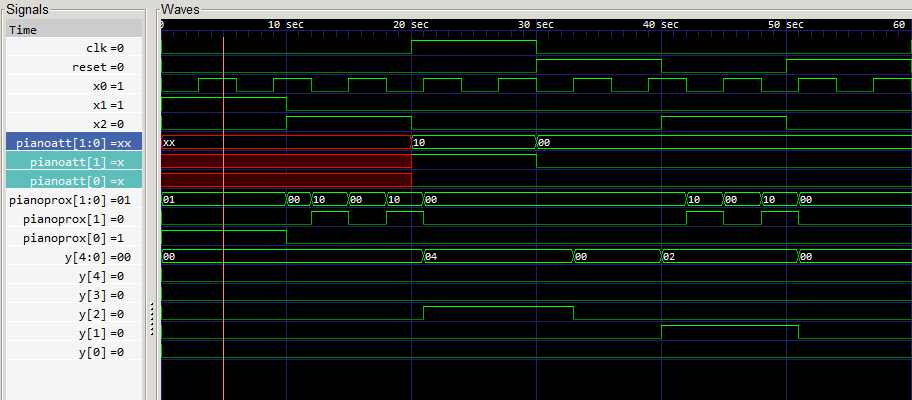

endmodule在这里,gtkwave显示:

如图像所示,时钟是不正确的。

输入x0不应该是周期性的,它只是表示在某个时候按下的按钮。由于这两个问题,我不能说其余的模块是否正常工作。

回答 1

Stack Overflow用户

回答已采纳

发布于 2021-02-09 15:30:22

您不正确地将信号连接到您的dut。dut实例(clk)中的第一个信号连接到模块声明(x0)中的第一个端口,等等。

要避免这种常见的错误,请使用按名称连接而不是按位置连接.参见IEEEST1800-2017,23.3.2.2节,按名称连接模块实例端口。

更改:

ascx dut(clk, reset, x0, x1, x2, y);至:

ascx dut (

.clk (clk),

.reset (reset),

.x0 (x0),

.x1 (x1),

.x2 (x2),

.y (y)

);与您的问题无关:不应该在assign块中使用always关键字。Refer to this explanation of a procedural continuous assignment

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/66121592

复制相关文章

相似问题