寄存器和整数比较不起作用

寄存器和整数比较不起作用

提问于 2021-03-08 05:07:33

在SystemVerilog中,我面临一个有趣的问题,在这里,与寄存器的比较不起作用。

module VGA_Colours

(

input wire clk, reset,

// input wire [3:0] swred, swgreen,

// input wire [1:0] swblue,

output wire hsync, vsync,

output wire [3:0] r, g, b

);

// constant declarations for VGA sync parameters

localparam H_DISPLAY = 640; // horizontal display area

localparam H_L_BORDER = 48; // horizontal left border

localparam H_R_BORDER = 16; // horizontal right border

localparam H_RETRACE = 96; // horizontal retrace

localparam H_MAX = H_DISPLAY + H_L_BORDER + H_R_BORDER + H_RETRACE - 1;

localparam START_H_RETRACE = H_DISPLAY + H_R_BORDER;

localparam END_H_RETRACE = H_DISPLAY + H_R_BORDER + H_RETRACE - 1;

localparam V_DISPLAY = 480; // vertical display area

localparam V_T_BORDER = 10; // vertical top border

localparam V_B_BORDER = 33; // vertical bottom border

localparam V_RETRACE = 2; // vertical retrace

localparam V_MAX = V_DISPLAY + V_T_BORDER + V_B_BORDER + V_RETRACE - 1;

localparam START_V_RETRACE = V_DISPLAY + V_B_BORDER;

localparam END_V_RETRACE = V_DISPLAY + V_B_BORDER + V_RETRACE - 1;

wire video_on, p_tick;

reg [9:0] ii;

reg j;

reg [3:0] red_reg, green_reg, blue_reg;

reg [11:0] rbg;

// mod-2 counter to generate 25 MHz pixel tick

reg pixel_reg = 0;

wire pixel_next;

wire pixel_tick;

always @(posedge clk)

pixel_reg <= pixel_next;

assign pixel_next = ~pixel_reg; // next state is complement of current

assign pixel_tick = (pixel_reg == 0); // assert tick half of the time

// registers to keep track of current pixel location

reg [9:0] h_count_reg, h_count_next, v_count_reg, v_count_next;

// register to keep track of vsync and hsync signal states

reg vsync_reg, hsync_reg;

wire vsync_next, hsync_next;

// infer registers

always @(posedge clk)

if(~reset)

begin

v_count_reg <= 0;

h_count_reg <= 0;

vsync_reg <= 0;

hsync_reg <= 0;

end

else

begin

v_count_reg <= v_count_next;

h_count_reg <= h_count_next;

vsync_reg <= vsync_next;

hsync_reg <= hsync_next;

end

// next-state logic of horizontal vertical sync counters

always @*

begin

h_count_next = pixel_tick ?

h_count_reg == H_MAX ? 0 : h_count_reg + 1

: h_count_reg;

v_count_next = pixel_tick && h_count_reg == H_MAX ?

(v_count_reg == V_MAX ? 0 : v_count_reg + 1)

: v_count_reg;

end

// hsync and vsync are active low signals

// hsync signal asserted during horizontal retrace

assign hsync_next = h_count_reg >= START_H_RETRACE

&& h_count_reg <= END_H_RETRACE;

// vsync signal asserted during vertical retrace

assign vsync_next = v_count_reg >= START_V_RETRACE

&& v_count_reg <= END_V_RETRACE;

// video only on when pixels are in both horizontal and vertical display region

assign video_on = (h_count_reg < H_DISPLAY)

&& (v_count_reg < V_DISPLAY);

// output signals

assign hsync = hsync_reg;

assign vsync = vsync_reg;

assign p_tick = pixel_tick;

always @(posedge p_tick) begin

if (~reset) begin

rbg <= 12'b000000000000;

ii <= 9'b0;

end else begin

if (h_count_reg == 0) begin

rbg <= 12'b000000000000;

ii <= 9'b0;

end else if (h_count_reg == ii) begin

ii <= ii + 9'b001010000;

rbg <= rbg + 12'b000010000000;

end

end

end

// output

assign r = (video_on) ? rbg[11:8] : 4'b0;

assign g = (video_on) ? rbg[7:4] : 4'b0;

assign b = (video_on) ? rbg[3:0] : 4'b0;

endmodule在上面的代码中,h_count_reg是0,工作正常。如果我将0更改为任何不同的数字,它就会像预期的那样工作。但是,如果我用一个变量(在我的模块顶部声明为reg[9:0] ii的"ii“)替换这个数字,代码似乎会忽略它,这是很奇怪的。用任何数字替换ii变量都可以。为什么?

TestBench文件:

module VGA_Colours_tb ();

logic clk;

reg reset;

wire hsync, vsync;

wire [3:0] r, g, b;

VGA_Colours scr0 (

.clk (clk),

.reset (reset),

.hsync (hsync),

.vsync (vsync),

.r (r),

.b (b),

.g (g)

);

initial begin

clk = 0;

forever #10 clk = ~clk;

end

always @(posedge clk) begin

#20

reset <= 1'b0;

#20

reset <= 1'b1;

#100000

$finish;

end

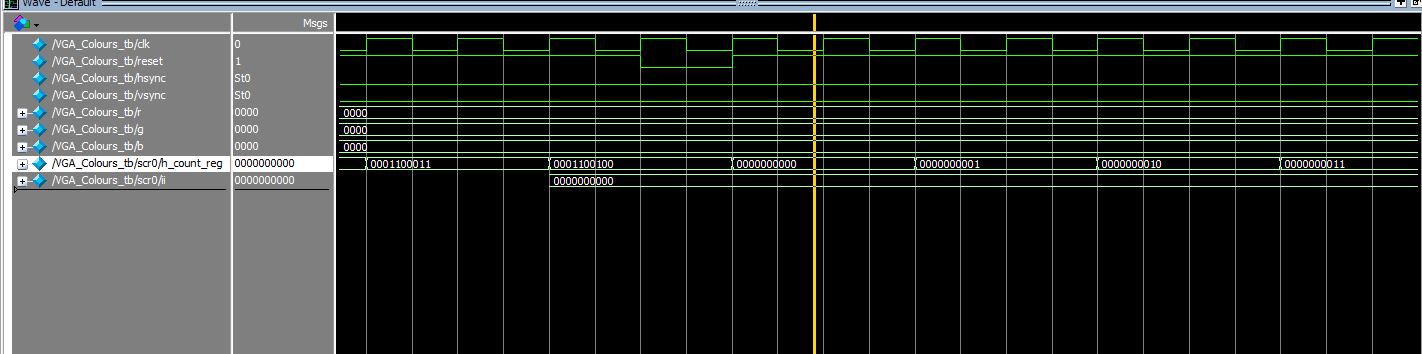

endmodule模拟波:

从代码中可以看到,当h_count_reg为==到ii时,增加rbg和ii的值。然而,基于模拟波,它并不是这样做的h_count_reg值不等于ii,而它实际上是。

回答 1

Stack Overflow用户

回答已采纳

发布于 2021-03-09 14:09:44

VGA_Colours模块中有一个逻辑错误。

下面是具有更一致缩进的代码:

always @(posedge p_tick) begin

if (~reset) begin

rbg <= 12'b000000000000;

ii <= 9'b0;

end else begin

if (h_count_reg == 0) begin

rbg <= 12'b000000000000;

ii <= 9'b0;

end else if (h_count_reg == ii) begin

rbg <= rbg + 12'b000010000000;

ii <= ii + 9'b001010000;

end

end

end当我运行您的模拟时,我观察到ii总是在初始重置之后为0。

代码有3条if语句。第一条if语句在模拟开始时为真,此时为reset=0。这将ii设置为0。

复位后,我看到h_count_reg=0 4次。这意味着第二个if语句是真实的4次。这使得ii = 0。

只有当if不是0时,第三个h_count_reg语句才会被计算。现在应该清楚的是,第三条if语句永远不可能是真的。这意味着ii不会增加,它将保持在0。例如,当h_count_reg=1时,(h_count_reg == ii)是false,因为ii总是0。

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/66524571

复制相关文章

相似问题