如何连续地将数据从全双工双口SRAM的端口放到端口?

如何连续地将数据从全双工双口SRAM的端口放到端口?

提问于 2022-09-27 08:58:56

在一个全双工双口SRAM中,我试图读取数据并将数据从A端口写入B端口,而无需等待时间。

module tb_fbdp_ram();

// Define our controlled signals

reg clk=0;

reg cs=0;

reg a_we, a_oe, b_we=0, b_oe=1;

wire [7:0] a_data; // this is the connection to ramcu data port

reg [7:0] a_addr=0; // this is the address for port A

wire [7:0] b_data; // this is the connection to ramcu data port

reg [7:0] b_addr=0; // this is the address for port A

reg [7:0] a_data_value; // need a register to store value to send on a write

reg [7:0] b_data_value; // need a register to store value to send on a write

// Instantiate our DUT

fbdp_ram dut (

clk , // clock input

cs , // chip select

a_we , // channel A write enable

a_oe , // channel A output enable

a_addr , // channel A address

a_data , // channel A inout data

b_we , // channel B write enable

b_oe , // channel B output enable

b_addr , // channel B address

b_data // channel B inout data

);

assign a_data = !a_oe ? a_data_value : 'bz;

assign b_data = !b_oe ? b_data_value : 'bz;

always #5 clk = ~clk;

initial begin

for(int i=0; i< 15; i++) begin

@(posedge clk);

// set up initial conditions

cs = 1;

a_we = 1;

a_oe = 0;

a_addr = i;

a_data_value = $urandom%10;

end

// set up initial conditions

for(int i=0; i< 15; i++) begin

@(posedge clk);

cs = 1;

a_we = 0;

a_oe = 1;

a_addr = i;

b_we = 1;

b_oe = 0;

b_addr = i+20;

b_data_value = a_data;

end

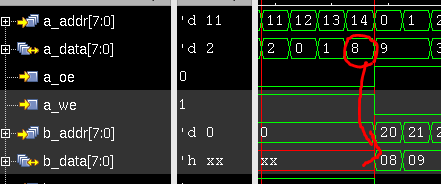

end我从A端口读取一些数据,并立即将它们写入B端口。但是,来自A端口的B端口的输入数据延迟了一个时钟。

如图中所示,'h08值被放入B端口的数据,而不是'h09。我怎么写“h09而不是”h08呢?

回答 1

Stack Overflow用户

回答已采纳

发布于 2022-09-27 10:23:05

首先删除行b_data_value = a_data;

在testbench的末尾,在任何其他块之外,添加:

assign b_data_value = a_data;

例如:

// ...

// ...

// set up initial conditions

for(int i=0; i< 15; i++) begin

@(posedge clk);

cs = 1;

a_we = 0;

a_oe = 1;

a_addr = i;

b_we = 1;

b_oe = 0;

b_addr = i+20;

end

// combinatorially assign to ensure instantaneous writing to b_data

assign b_data_value = a_data;

end页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/73864888

复制相关文章

相似问题